全球互联网巨头纷纷高调宣布进入半导体行业

描述

近些日子,全球互联网巨头纷纷高调宣布进入半导体行业。阿里、微软、Google、Facebook等都宣布在芯片领域的动作,那么互联网巨头的这些动作又会对芯片行业造成什么影响?本文为您带来详细分析。

阿里、微软、Google、Facebook互联网巨头纷纷入局芯片

我们首先盘点一下互联网巨头近几年来在芯片领域的动作。

Google可谓是互联网公司在芯片领域走得最远的公司。2015年Google就开始在其数据中心中部署自己设计的深度学习加速芯片TPU负责推理,在去年则是推出了第二代TPU可以兼顾深度学习推理和训练,并且还在手机Pixel 2中也部署了自己设计的IPU用以加速图像处理相关应用。此外,Google还把处理器架构领域的两大宗师David Patterson和John Hennessy招入麾下,未来可望在芯片领域有更多产出。

微软也不甘落后,2014年在ISSCC上发表了自己设计的使用在Xbox Kinect 2中的ToF传感器芯片,之后在2016年又发布了自己设计的用在HoloLens中的HPU协处理器芯片,而在近日更是发布了Azure Sphere 物联网平台,其中包含了使用在MCU芯片中的Microsoft Pluton安全模块以保证物联网数据安全。第一款Azure Sphere芯片将会是联发科和微软合作推出的MT3620,其中就包含了Microsoft Pluton。

除了Google和微软外,Facebook也开始在芯片领域有所动作,在网站上贴出了ASIC和FPGA设计的相关职位招聘启事。Facebook AI研究负责人Yann LeCun也在twitter上跟帖表示这将会是一个和深度学习相关的芯片设计岗位,据业界预测Facebook正在招募工程师开发和TPU类似的芯片以加速服务器端深度学习应用。

Yann LeCun对于Facebook招募ASIC工程师的tweet

在中国,互联网巨头阿里先是宣布开始研发人工智能加速芯片Ali-NPU,其性能将是目前市面上主流CPU、GPU架构AI芯片的10倍,而制造成本和功耗仅为一半,可以实现比传统GPU高40倍以上的性价比。之后,阿里高调宣布全资收购中天微系统,而该系统目前拥有中国独立知识产权的指令集,阿里此举据信是为了加强自己在物联网领域的布局。

启示一:摩尔定律的尽头是异构计算时代,互联网巨头要自己定制芯片

互联网巨头纷纷布局芯片,意味着原有的半导体产业局面正在发生重大改变。最初,半导体行业作为高科技行业,其发展遵循摩尔定律的方式,每18个月工艺特征尺寸缩小,随着工艺制程的进化,同样的芯片的制造成本会更低,因为单位面积晶体管数量提升导致相同的芯片所需要的面积缩小,另外芯片性能会随着工艺特征尺寸缩小而上升,于是半导体行业走在摩尔定律指导下的周期性性能提升成本降低的高速发展模式。由于其高技术高附加值的特点,芯片的毛利率很高,因此芯片设计公司可以通过把芯片出售给下游企业,就能活得很滋润。

在半导体设计的黄金年代,“芯片设计”这四个字就意味着高技术和高利润率,芯片的原材料是砂子,却能卖出几十甚至上百美金的单价,因此成功的芯片一旦量产就像是开动了印钞机一样。为了增加出货量改善设计复用性,半导体公司往往青睐通用平台式芯片,例如Intel的处理器以及Qualcomm的SoC。

然而,随着摩尔定律越来越接近物理极限,再继续缩小特征尺寸需要的资本量越来越大,换句话说随着特征尺寸缩小,芯片的成本上升很快。芯片的成本包括NRE成本(Non-Recurring Engineering,指芯片设计和掩膜制作成本,对于一块芯片而言这些成本是一次性的)和制造成本(即每块芯片制造的成本)。在先进工艺制程,由于工艺的复杂性,NRE成本非常高。例如FinFET工艺往往需要使用double patterning技术,而且金属层数可达15层之多,导致掩膜制作非常昂贵。

另外,复杂工艺的设计规则也非常复杂,工程师需要许多时间去学习,这也增加了NRE成本。对于由先进制程制造的芯片,每块芯片的毛利率较使用落后制程制造的芯片要高,但是高昂的NRE成本意味着由先进制程制作的芯片需要更多的销量才能实现真正盈利。

随着摩尔定律遇到瓶颈,靠工艺制程提升来增进性能的成本实在太高,因此需要更多根据应用做专用设计,靠架构设计来进一步提升性能,这也是“异构计算”的思路。在过去,半导体公司通常倾向于推出平台式的产品,例如Intel的CPU,Qualcomm的Snapdragon等等,但是这样的通用平台在今天已经无法满足移动设备对于性能和能效比的需求,尤其是在AR/VR、终端人工智能等新兴应用中。

就在同时,我们看到了Facebook、Google、阿里等互联网巨头向硬件领域的进军。事实上,这也是互联网公司生态化发展到今天的必然:互联网公司之前一直在搭建生态抢夺流量入口,让用户可以更方便地使用自己的服务;这个入口过去是从PC,手机,到了今天PC、手机等传统入口已经没法满足高速发展的互联网巨头的胃口,因此巨头们都想到了搭建自己的硬件平台作为自己服务的入口。这样的硬件可以是AR/VR设备(如微软的HoloLens,Facebook的Oculus),可以是新型消费电子设备(如Google的Clip自动摄像机),也可以是进入智能制造和智能家庭的IoT终端节点。

当互联网巨头开始进入硬件市场时,会对半导体行业产生巨大的影响。首先,互联网巨头追求硬件能实现极致化的性能以实现差异化用户体验用来吸引用户。如前所述,目前摩尔定律遇到瓶颈,想要追求极致体验需要的是走异构计算自己定制化芯片的路子,光靠采购传统半导体厂商的芯片已经没法满足互联网巨头对于硬件的需求,至少在核心芯片部分是这样。因此,Facebook、Google、阿里等互联网巨头都是异构计算的积极拥护者,为了自己的硬件布局或计划设计芯片,或已经开始设计芯片。这么一来,原来是半导体公司下游客户的互联网公司现在不需需要从半导体公司采购芯片了,这样的产业分工变化会引起行业巨变。

其实这样的上下游整合趋势从很久以前就已经在手机领域开始,几年前消费电子巨头苹果和华为已经开始从采购标准芯片到设计自己的SoC,前几年小米也逐渐开始做自己的SoC芯片,一旦Oppo,Vivo等手机巨头都跟风开始自己做核心芯片,高通的就会承受很大压力。而互联网巨头入局芯片,也可以理解为手机领域发生的故事也开始发生到了其他硬件领域,将对于高通以及其他传统半导体公司产生深远的影响。

其次,互联网巨头制造硬件的目的只是为了吸引用户进入自己的生态使用自己的服务,其最终盈利点并不在贩卖硬件上而是在增值服务上。因此,互联网巨头在为了自己的硬件设计芯片时可以不计成本,基本不考虑cost-down。在传统半导体公司的眼光中,一块芯片成本是10美元还是8美元可以是天壤之别,但是在互联网公司的看法里这样的成本差别根本不是事,性能怎么好就怎么来。

从另一个角度来说,一旦自己设计核心芯片的互联网公司进入同一个领域,那些靠采购半导体公司标准芯片搭硬件系统的公司的就完全没有竞争力了,无论是从售价还是性能,拥有自己核心芯片的互联网巨头都能实施降维打击。一旦这些硬件公司失去竞争力,那么依赖于这些客户的半导体公司的生存空间又会进一步被压缩。

总而言之,互联网巨头进入芯片领域,首先处于性能考虑不再从半导体公司采购核心芯片,这冲击了传统行业分工,使传统芯片公司失去了一类大客户;另一方面互联网巨头的生态式打法可以让自研硬件芯片不考虑成本,这又冲击了那些从半导体公司采购芯片的传统硬件公司,从而进一步压缩了半导体公司的市场。在这两个作用下,半导体芯片公司的传统经营模式必须发生改变才能追上新的潮流。

启示二:半导体行业分工洗牌,三种道路应对互联网企业野蛮人入侵

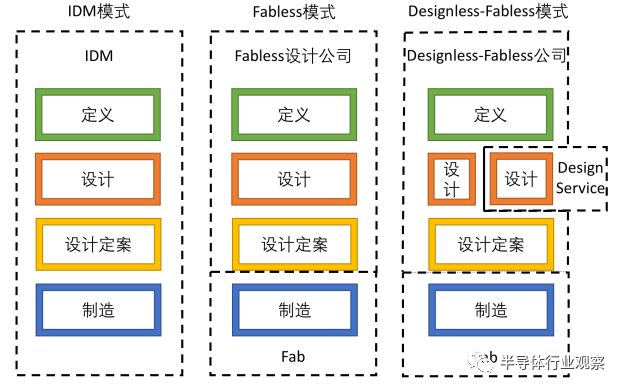

目前,半导体芯片领域的分工,大概可以分为定义、设计、设计定案、制造等几个环节。定义是指芯片顶层架构和指标的定义;设计是指具体的电路设计,包括数字RTL设计、模拟/混合信号电路设计等等;设计定案是指芯片设计最终确定并进入Fab决定开始制造光刻掩膜,意味着需要花费一笔掩膜开销;制造则是在Fab最终根据掩膜把芯片制造出来。

今天的半导体行业的分工,最为大家熟知的是Fabless模式,即芯片设计公司负责定义、设计和设计定案,而制造则是在提供代工的Fab完成;三星、Intel等半导体巨头也会走包含从定义到制造所有环节的IDM模式;此外不少公司是混合Fabless和IDM,即有的产品走Fabless模式,而有的产品走IDM模式,例如Broadcom在CMOS芯片产品线走的是Fabless,而在射频前端模组产品线则是IDM模式有自己的Fab。在今天的半导体行业分工中,设计服务公司提供模块设计IP以及协助一些公司做设计,主要起的是辅助作用。

在互联网巨头入局半导体行业后,又出现了一种新的模式,即互联网公司负责定义芯片、完成小部分设计、并花钱完成设计定案流片(互联网公司不差钱!),设计服务公司负责大部分设计,而代工厂负责芯片制造。这种新模式可以称为Designless-Fabless模式。历史上,半导体公司从传统的IDM走到Fabless模式,主要是因为Fab开销过高,成为了半导体公司发展的包袱,而代工厂则提供了一个非常灵活的选项。

今天,互联网公司入局半导体后走Designless-Fabless模式,把大量设计外包,则主要是因为时间成本。互联网巨头做芯片,追求的除了极致性能之外,还有快速的上市时间。对于他们来说,错过了圣诞节/双十一档期将会是灾难性的。如果要像传统半导体公司一样,需要从头开始培养自己的前端+后端设计团队,从头开始积累模块IP,恐怕第一块芯片上市要到数年之后。这样的节奏,是跟不上互联网公司的快速迭代节奏的。

那么如何实现高性能加快速上市呢?最佳方案就是这些巨头自己招募芯片架构设计团队做芯片定义,用有丰富经验的业界老兵来根据需求定制架构以满足性能需求,而具体的实现,包括物理版图设计甚至前端电路设计都可以交给设计服务公司去做。半导体芯片的一个重要特点就是细节非常重要,ESD、散热、IR Drop等一个小细节出错就可能导致芯片性能大打折扣无法达到需求。因此,如果把具体设计工作交给有丰富经验的设计服务公司,就可以大大减少细节出错的风险,从而减小芯片需要重新设计延误上市时间的风险。

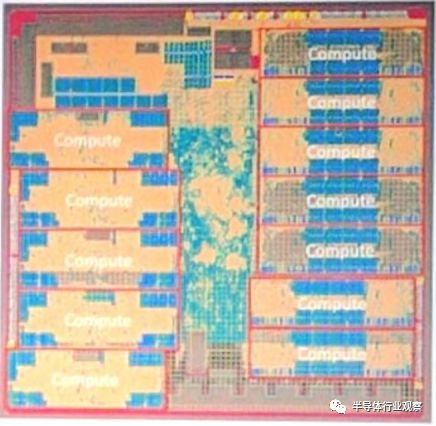

事实上,我们已经在一些芯片中看到互联网巨头负责芯片架构+设计服务公司提供IP/设计服务的模式了。一个例子就是微软使用在HoloLens中的HPU,其中微软设计了多核架构以加速AR计算,而每个核则是使用了Cadence的Tensilica IP。

微软的HPU,大量使用了Cadence的Tensilica IP

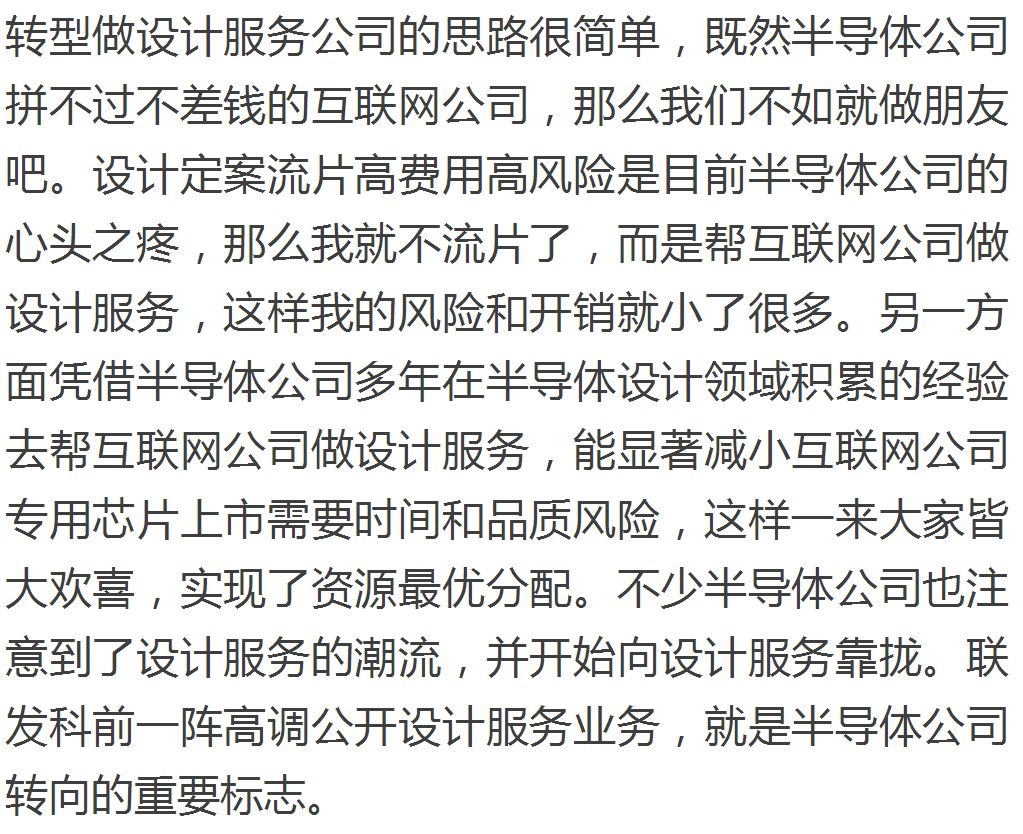

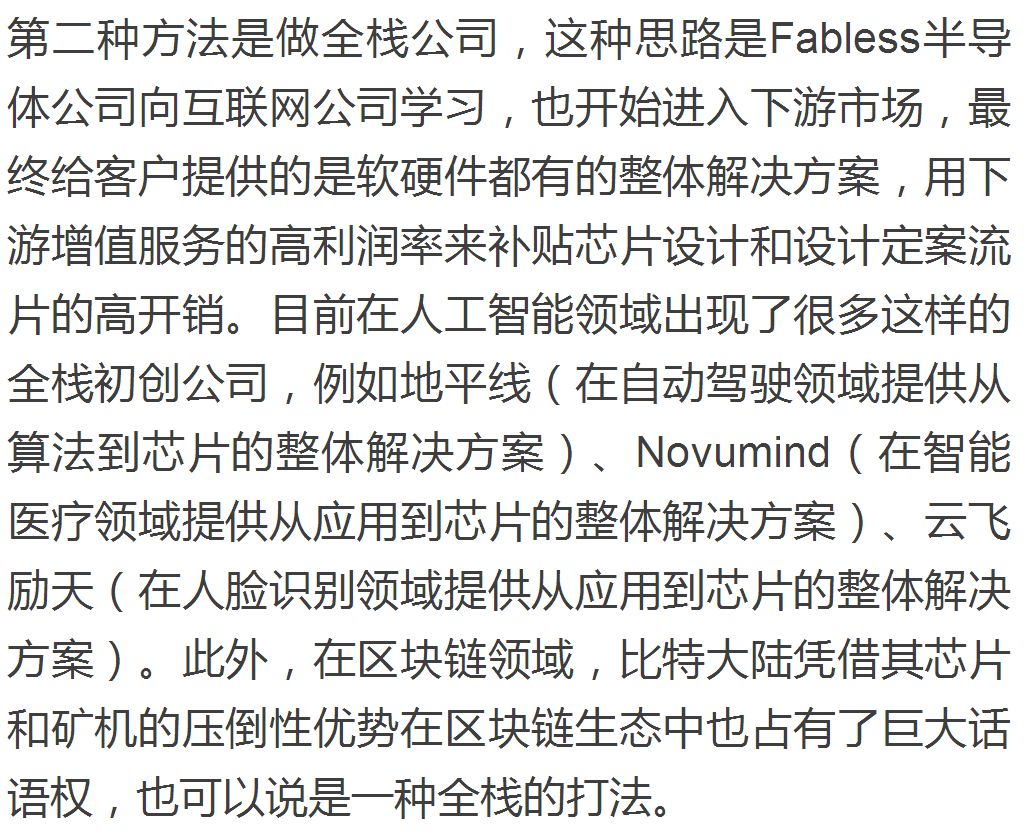

不差钱的互联网公司以生态打法入局半导体行业,犹如野蛮人入侵,对于Fabless公司最头疼的设计定案流片费用人家互联网公司不差钱基本不在乎,那么半导体公司如何应对呢?应该说至少有三种方法,分别是转型做设计服务公司、做全栈公司和做IDM公司。

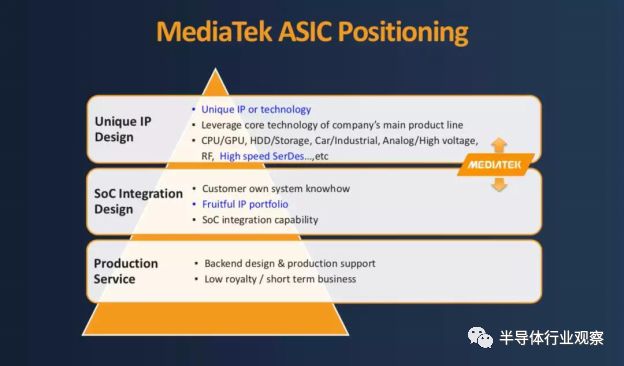

联发科作为把传统半导体芯片公司的运营哲学发展到极致的公司在今天也开始转向设计服务业务,可以说是设计服务的春天来临了。

结语

随着互联网厂商纷纷入局半导体芯片,传统半导体公司的商务模式将会遇到很大挑战,需要有新的商务模式来迎合时代潮流。面对互联网公司Designless-Fabless模式的威胁,我们认为半导体公司可以转型做设计服务,可以做全栈公司从下游获取更多利润,或者走IDM去做更高利润率的核心半导体元器件。互联网公司入局对于半导体行业未来走向的影响,让我们拭目以待。

-

联想将进军互联网2011-03-18 0

-

汽车半导体行业2012年或将基本实现复苏2012-01-15 0

-

全球半导体市场进入供大于求的局面2013-01-30 0

-

互联网公司做手机,你觉得靠谱吗?2014-09-04 0

-

工业互联网2016-01-25 0

-

智能热潮来袭,净水行业的”互联网+“时代2016-09-21 0

-

锐捷助互联网数据中心网络自动化、可视化运维2017-01-25 0

-

CRM在互联网行业的应用2017-08-28 0

-

中美贸易战对全球半导体产业链的影响2018-08-30 0

-

企业拿什么迎战互联网下半场2018-11-07 0

-

智慧重庆,2019全球半导体产业博览会欢迎您2018-11-20 0

-

嵌入式行业和互联网行业哪个好2021-12-17 0

-

有哪些“跨界造芯”的互联网巨头2022-03-31 1743

全部0条评论

快来发表一下你的评论吧 !