74ls151应用电路图大全(全加器\表决器)

IC应用电路图

描述

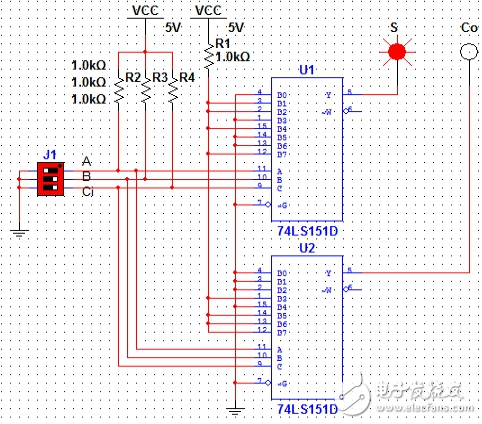

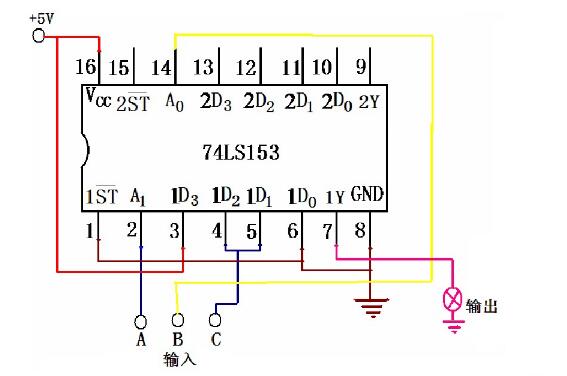

74ls151应用电路图(一):全加器设计电路

利用74LS151数据选择器可以设计如图6所示电路:

两个74LS151分别得到S和Co;其中U1的数据端配置为D1=D2=D4=D7=1,其余为0;

U2配置为D3=D5=D6=D7=1,其余为0.

图6

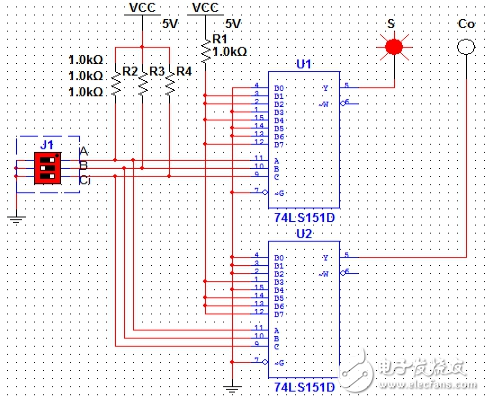

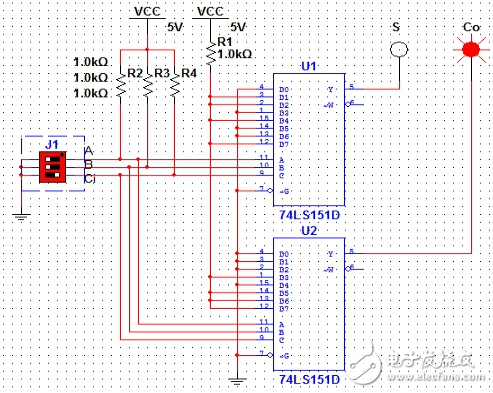

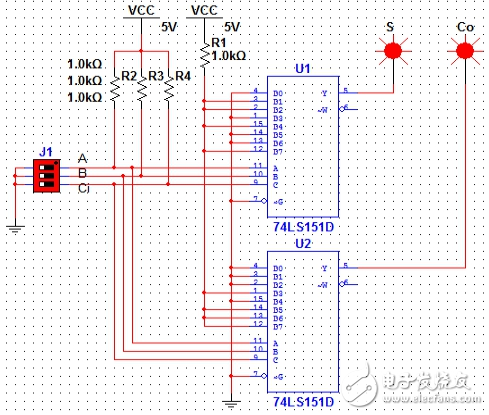

同样,下面也给出{A=1,B=0,Ci=0};{A=0,B=1,Ci=0};{A=1,B=1,Ci=0}和{A=1,B=1,Ci=1}四种输入状态下的S和Co状态。

图7(A=1,B=0,Ci=0)

图8(A=0,B=1,Ci=0)

图9(A=1,B=1,Ci=0)

图10(A=1,B=1,Ci=1)

可以看出,电路的逻辑关系也是正确的。

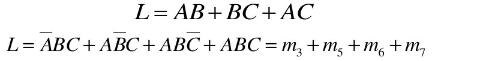

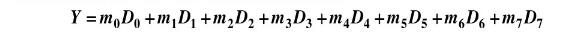

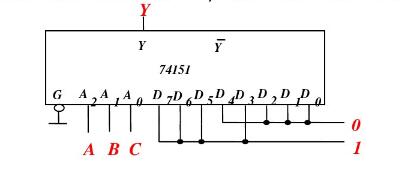

74ls151应用电路图(二):实现三人表决器

将输入变量接至数据选择器的地址输入端,即A=Ay,B=A,C=A。o输出变量接至数据选择器的输出端,即L=Y。将逻辑函数L的最小项表达式与74151的功能表相比较,

显然,Y式中出现的最小项,对应的数据输入端应接1,Y式中没出现的最小项,对应的数据输入端应接0。即D3=D5=D6=D7=1;D0=D1=D2=D4=0。

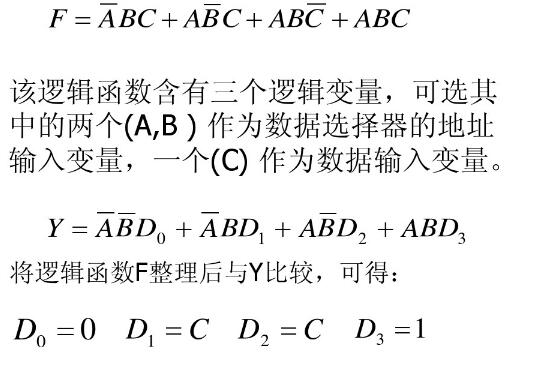

该逻辑函数含有三个逻辑变量,可选其中的两个(A,B)作为数据选择器的地址输入变量,一个(C)作为数据输入变量。

用数据选择器74LS151实现接线图

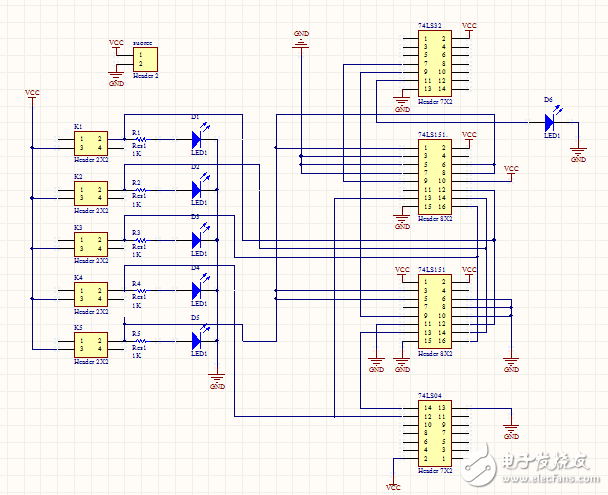

74ls151应用电路图(三):实现五人表决器

系统原理

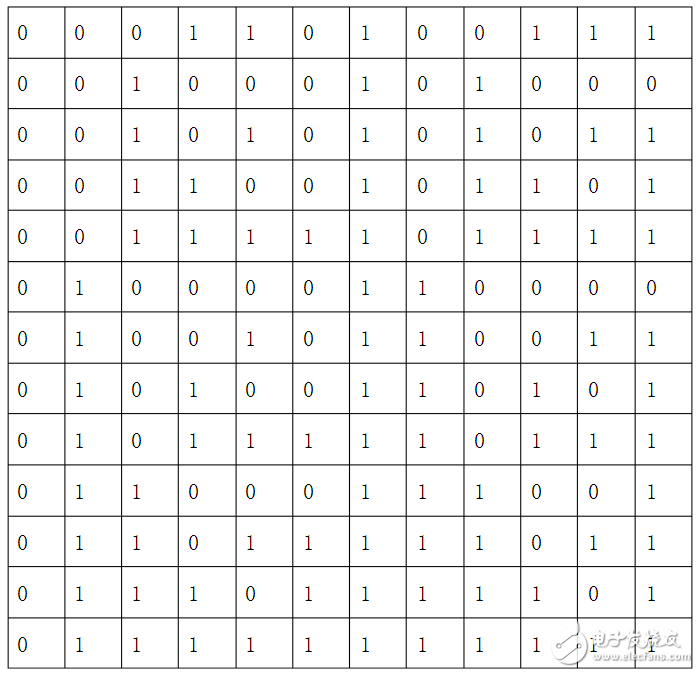

五人表决器,只要赞成人数大于或等于三,则表决通过。因此,只需将每位表决人的结果相加,判断结果值。设五个开关A、B、C、D、E作为表决器的五个输入变量,输入变量为逻辑“1”时,表示表决者“赞成”,红灯亮;输入变量为“0”时,表示表决者“不赞成”,红灯不亮;输出逻辑“1”时,表示表决“通过”,绿灯亮;输出逻辑“0”时,表示表决“不通过”,绿灯不亮;当表决器的五个输入变量中有3个以上(含3个)为“1”时,则表决器输出为“1”,此时绿灯就亮了。

真值表

如果绿灯亮了,则表示表决通过,若绿灯不亮了,表示不通过。

电路设计

-

8人表决器2015-04-12 0

-

求proteus有74ls151的元件库2017-12-04 0

-

一个简单的lm339和74ls151的组合电路,lm339和74ls151接合起来后,功耗电流变得很大,这是为什么?2019-01-25 0

-

74LS151/54LS151 pdf datasheet2008-08-06 2392

-

74ls151管脚图引脚图 真值表2007-11-29 91199

-

74LS151 英版数据手册2016-08-29 1445

-

74LS151英文手册2016-11-22 1089

-

74LS153实现三人表决电路(4种方式实现3人表决电路)2018-01-26 342857

-

74ls00制作三人表决器电路详解2018-02-08 248514

-

74ls20实现的四人表决器2018-02-08 93894

-

74ls151实现三人表决器2018-02-08 182886

-

74ls138应用电路图大全(五款74ls138全加器电路/抢答器电路/三人表决器电路)2018-05-04 99888

-

用74ls151实现全加器设计电路2018-05-07 114289

-

74ls151中文资料汇总(74ls151引脚图及功能_工作原理及应用电路)2018-05-07 501525

-

74ls151引脚图及功能表2021-06-25 134953

全部0条评论

快来发表一下你的评论吧 !