74ls165中文资料汇总(74ls165引脚图及功能_工作原理及应用电路)

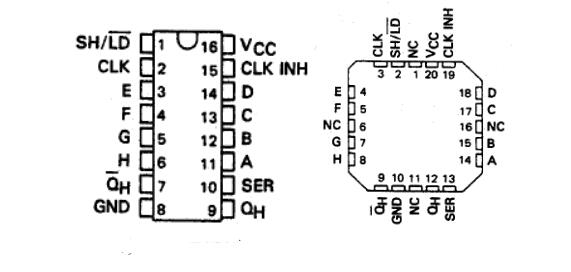

芯片引脚图

描述

74ls165引脚图及功能

74ls165是8位并入串出移位寄存器。

CLK,CLK INH 时钟输入端(上升沿有效)

A-H 并行数据输入端

SER 串行数据输入端

QH 输出端

互补输出端

互补输出端

移位控制/置入控制(低电平有效)

移位控制/置入控制(低电平有效)

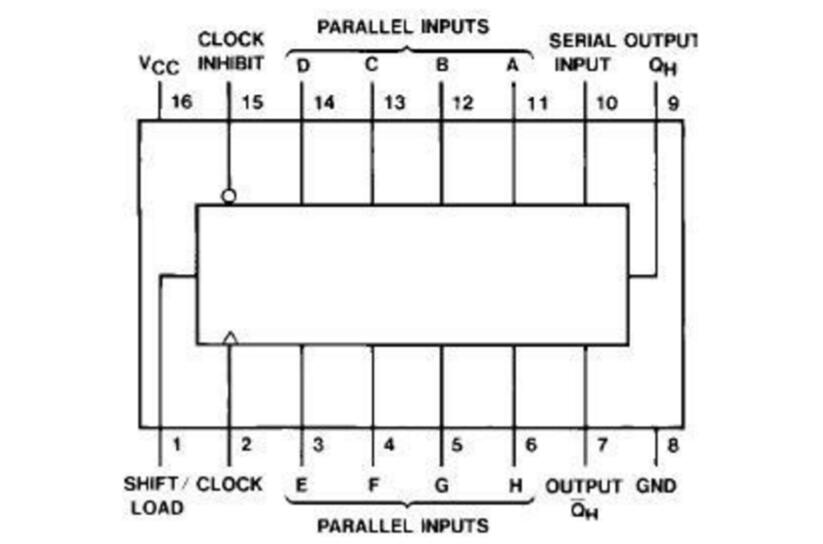

74ls165工作原理

当移位\植入控制端(SH/LD)为低电平时,并行数据(A-H) 被置入寄存器,而时钟(CLK,CLK INH)及串行数据(SER)均无关。当SH/LD)为高电平时,并行置数功能被禁止。

CLK和CLK INK在功能上是等价的,可以交换使用。当CLK和CLK INK有一个为低电平并且SH/LD为高电平时,另一个时钟可以输入。当CLK和 CLK INK有一个为高电平时,另一个时钟被禁止。只有在CLK为高电平时CLK INK才可变为高电平。

74ls165逻辑图

74ls165极限值

电源电压…………………………………7V

输入电压…………………………………5.5V

SH/LD与CLKINK间电压……………………5.5V

工作环境温度

54164……………………………………-55~125℃

74164……………………………………-0~70℃

储存温度……………………………………-65℃~150℃

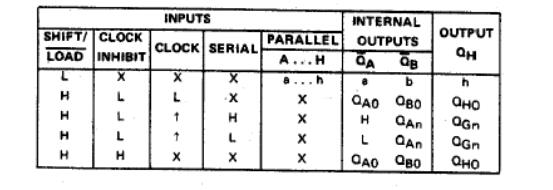

74ls165真值表

H-高电平

L-低电平

X-任意电平

↑-低到高电平跳变

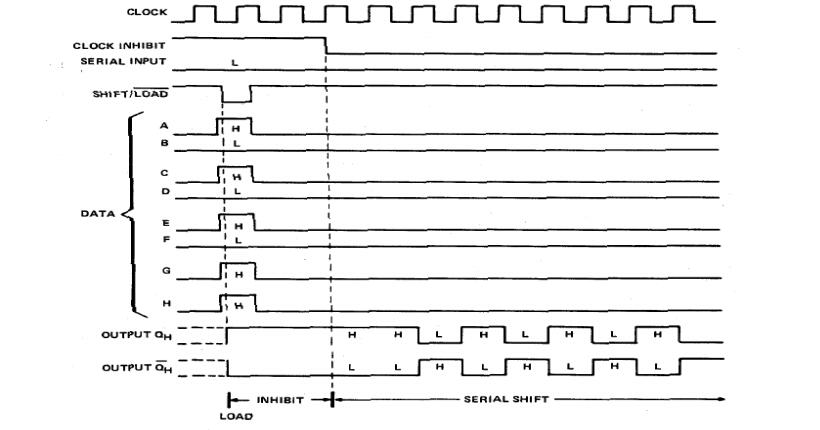

74ls165时序图

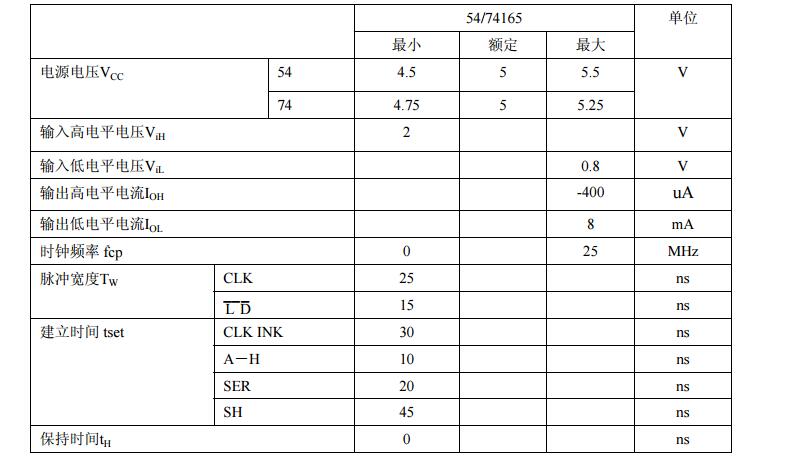

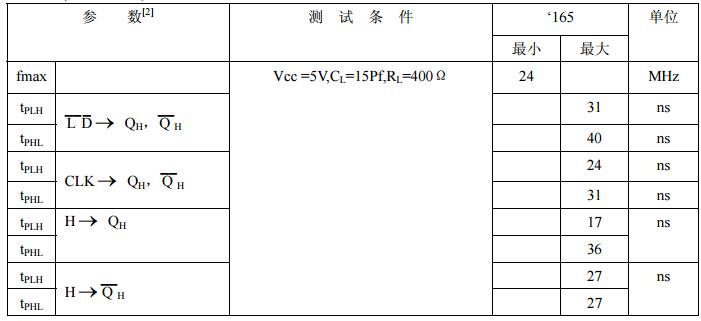

74ls165推荐工作条件

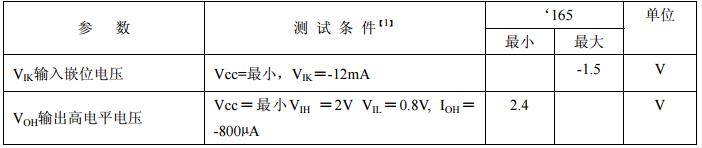

74ls165静态特性

[1]:测试条件中的“最小”和“最大”用推荐工作条件中的相应值。

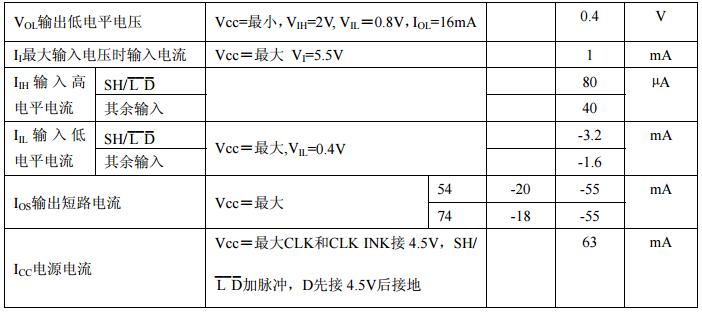

74ls165动态特性

[2]:fmax最大时钟频率。tPLH输出由低电平到高电平传输延迟时间tPHL输出由高电平到低电平传输延迟时间

两款74ls165应用电路

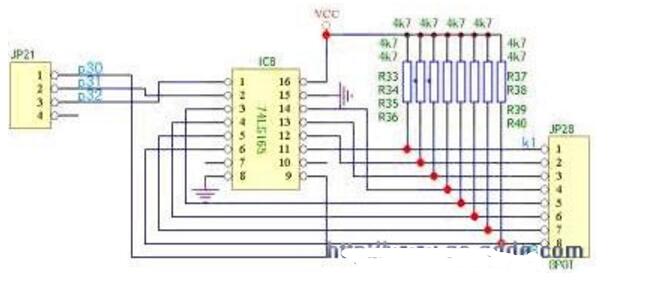

应用电路一:

TXD(P3.1)作为移位脉冲输出端与74LS165的移位脉冲输入端CLOCK相连;RXD(P3.0)作为串行输入端与74LS165的串行输出端QH相连;P3.2用来控制74165的移位与置入。

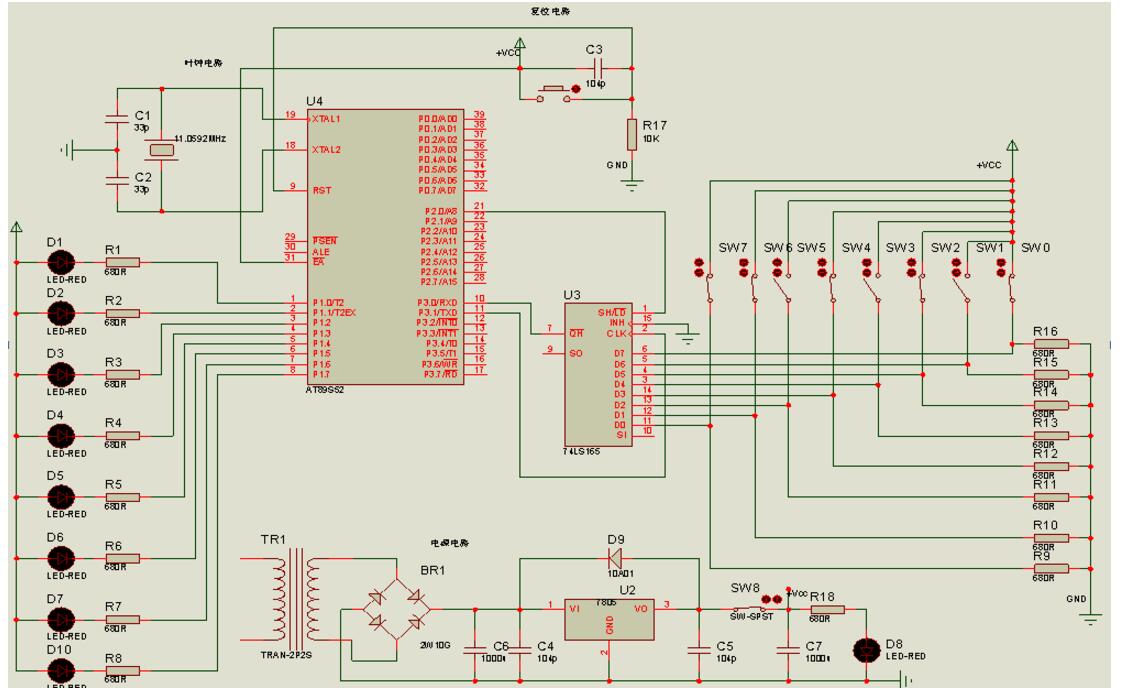

应用电路二:

89C51和74LS165连接电路图

74ls165相关文章:

一文看懂74ls165级联测试程序与proteus仿真电路图

74ls165相关下载:

-

74LS165如何接可以实现并串转换?2015-03-06 0

-

74hc164和74hc165串口驱动程序对不?2015-05-06 0

-

请问如何使用74LS165将AVR的串口输入扩为并口输入?2020-11-17 0

-

74LS165中文资料.pdf2008-03-19 3144

-

74LS165 pdf|sn54165A pdf2008-06-08 939

-

74ls165引脚图,74ls165参数资料2008-09-06 10939

-

芯片74LS165资料2015-12-31 803

-

74LS165英文手册2016-11-21 588

-

74hc165中文资料详细(74hc165工作原理_引脚图及功能_应用电路_逻辑图)2018-02-02 187979

-

怎么样用单片机的串口驱动74LS1652018-03-07 6640

-

74ls273中文资料汇总(74ls273引脚图及功能_工作原理及应用电路)2018-04-26 169712

-

74ls165应用电路图大全(三款74ls165应用电路)2018-05-08 16955

-

一文看懂74ls165级联测试程序与proteus仿真电路图2018-05-08 12632

-

基于74LS165芯片的串行口方式仿真电路图2020-10-07 3560

-

使用单片机和74LS595和74LS165扩展实现8乘8键盘的仿真文件免费下载2021-03-22 840

全部0条评论

快来发表一下你的评论吧 !