74ls160和74ls161区别

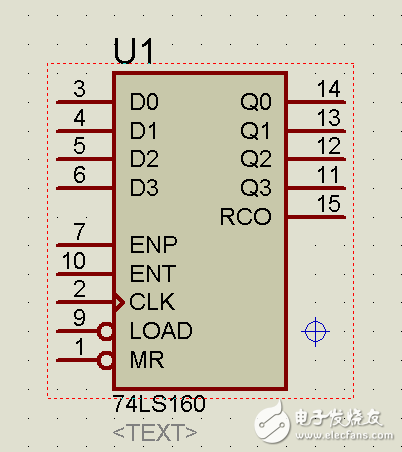

芯片引脚图

描述

74ls160介绍

·用于快速计数的内部超前进位

·用于n 位级联的进位输出

·同步可编程序

·有置数控制线

·二极管箝位输入

·直接清零

·同步计数

74ls160是十进制计数器,也就是说它只能记十个数从0000-1001(0-9)到9之后再来时钟就回到0,首先是clk,这是时钟。之后是rco,这是输出,MR是复位低电频有效(图上接线前面花圈的都是低电平有效)load是置数信号,当他为低电平时,在始终作用下读入D0到D3。为了使161正常工作ENP和ENT接1另外D0到D3是置数端Q0到Q3是输出端。

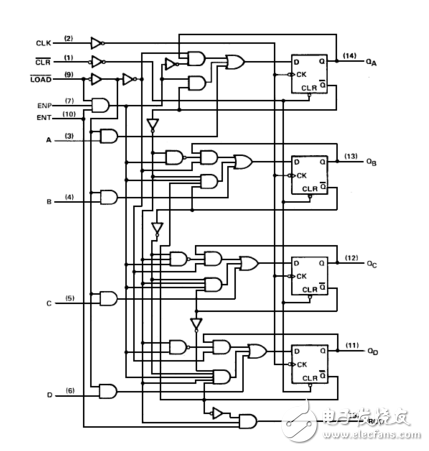

这种同步可预置十进计数器是由四个D型触发器和若干个门电路构成,内部有超前进位,具有计数、置数、禁止、直接(异步)清零等功能。对所有触发器同时加上时钟,使得当计数使能输入和内部门发出指令时输出变化彼此协调一致而实现同步工作。这种工作方式消除了非同步(脉冲时钟)计数器中常有的输出计数尖峰。缓冲时钟输入将在时钟输入上升沿触发四个触发器。

这种计数器是可全编程的,即输出可预置到任何电平。当预置是同步时,在置数输入上将建立一低电平,禁止计数,并在下一个时钟之后不管使能输入是何电平,输出都与建立数据一致。清除是异步的(直接清零),不管时钟输入、置数输入、使能输入为何电平,清除输入端的低电平把所有四个触发器的输出直接置为低电平。

超前进位电路无须另加门,即可级联出n位同步应用的计数器。它是借助于两个计数使能输入和一个动态进位输出来实现的。两个计数使能输入(ENP和ENT)计数时必须是高电平,且输入ENT必须正反馈,以便使能动态进位输出。因而被使能的动态进位输出将产生一个高电平输出脉冲,其宽度近似等于QA输出高电平。此高电平溢出进位脉冲可用来使能其后的各个串联级。使能ENP和ENT输入的跳变不受时钟输入的影响。

电路有全独立的时钟电路。改变工作模式的控制输入(使能ENP、ENT或清零)纵使发生变化,直到时钟发生为止,都没有什么影响。计数器的功能(不管使能、不使能、置数或计数)完全由稳态建立时间和保持时间所要求的条件来决定。

74ls160逻辑图

74LS161介绍

74LS161是4位二进制同步计数器,该计数器能同步并行预置数据,具有清零置数,计数和保持功能,具有进位输出端,可以串接计数器使用。

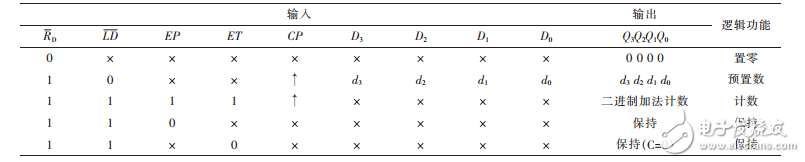

74LS161的引脚排列和逻辑功能如图1所示。各引出端的逻辑功能如下。1脚为清零端/RD,低电平有效。2脚为时钟脉冲输入端CP,上升沿有效(CP↑)。3~6脚为数据输入端A0~A3,可预置任意四位二进制数。7脚和10脚分别为计数控制端EP和ET,当其中有一脚为低电平时计数器保持状态不变,当均为高电平时为计数状态。9脚为同步并行置数控制端/LD,低电平有效。11~14脚为数据输出端QQ30~。15脚为进位输出端RCO,高电平有效。74LS161可编程度数器的真值表如下。

表 74LS161可编程度数器的真值表

74ls161和74ls160 有什么区别?

74ls161为四位二进制,74ls160 为2-10进制;且都为同步可预置计数器。

74ls161 是4位二进制同步计数器(直接清除),74ls160 是4位十进制同步计数器(直接清除)。

-

8.9.4 74LS161介绍(1)#硬声创作季学习硬声知识 2022-12-03

-

74ls1612013-05-20 0

-

三片74LS161怎么级联计数2400?2019-04-24 0

-

74LS161计数器及显示应用电路图2007-12-02 12389

-

74ls160引脚图管脚图及功能真值表2008-01-06 127258

-

74ls160/1电路图2008-01-06 3433

-

74ls192和74ls160的区别有哪些2017-12-21 32288

-

74ls161中文资料_74ls161计数器功能及其应用2018-01-02 543218

-

基于74LS161的扭环形计数器自启动设计2018-01-17 38457

-

74ls161与74ls163有什么区别2018-05-08 55933

-

74ls161商品批发价格 74ls161引脚图与管脚功能测试2021-06-08 5231

-

74ls160引脚图与真值表2021-06-04 88595

-

74ls161引脚图及功能介绍2021-07-08 208133

-

74ls160引脚图及功能真值表介绍2022-05-25 130750

全部0条评论

快来发表一下你的评论吧 !