MOS管简介:PART–0基础知识

描述

PART– 0 基础知识

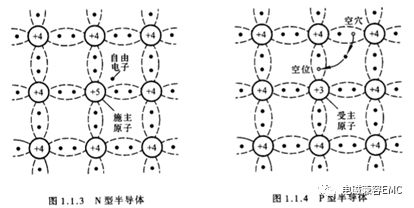

在讲MOS管之前,我们来回忆一下半导体材料。如下图:

做笔记:

N型半导体杂质为P原子,多子为电子

P型半导体杂质为B原子,多子为空穴

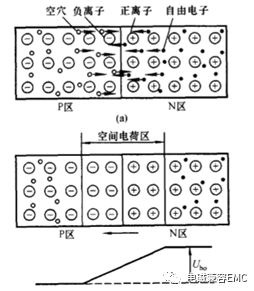

由于杂质半导体中有可自由移动的多子,当N型半导体跟P型半导体相接触,多子发生扩散运动,自由电子与自由空穴复合形成空间电荷区,也就是我们常说的耗尽层。

再做个笔记:耗尽层中没有自由移动的导电粒子。

PN结的结电容的充电过程,实际上可以近似地看做对耗尽层复合的自由带电粒子进行补充。

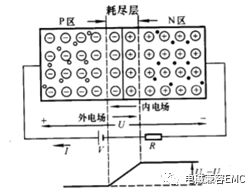

外加电压:

当PN结外接正偏电压高于PN结两端势垒区的电压时,耗尽层导电粒子补充完毕,可以跟正常杂质半导体一样具备导电能力,电路导通。

相反的,如果PN结外接反偏电压,耗尽层扩大,电路截止。

PART-1 MOS管结构

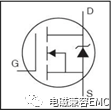

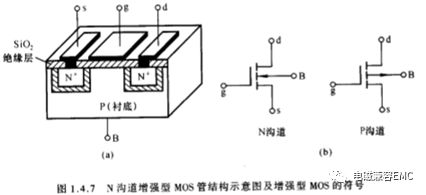

下文开始介绍MOS管,以增强型N-MOSFET为例子进行讲解。

增强型N-MOSFET,全称:N沟道增强型绝缘栅场效应管,在讲解其结构前,请读者记住几个关键词:

① N沟道

② 绝缘栅

③ 增强型

④ 体二极管

如模电书(童诗白,第四版)中我们熟悉的结构示意图所示,N沟道增强型MOSFET的结构可视为:

在P型半导体衬底上,制作两个N型半导体区域并引两个金属电极,作为源极S与漏极D;并在P衬底上制作一层SiO2绝缘层,另外引一个金属电极作为栅极G。

其结构特征可解释为以下几点:

①由于N型半导体直接加在P型半导体衬底上,两个N区与P区之间会形成耗尽层。

②由于栅极G是加在SiO2绝缘层上,与P型半导体衬底间并不导电,只有电场作用

③栅极G外加电场后,吸引P型半导体中的自由电子,同时填充耗尽层,形成反型层导电沟道,连接两个N型半导体区域,使得增强型N-MOSFET导通。

④ 工艺上制作N-MOSFET时,将源极S与P型半导体衬底直接连接,源极S等同于P型半导体衬底,与漏极D的N型半导体区之间有一个PN结,该PN结即为N-MOSFET的体二极管。

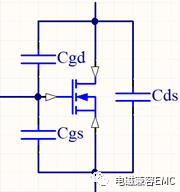

⑤如上图所示,增强型N-MOSFET各电极之间各有一个寄生电容,其中源极S与漏极D之间的电容Cds为其输出电容,结构上为体二极管位置PN结的结电容;栅极G与S极、D极之间的寄生电容Cgd、Cgs之和为输入电容,实质上为形成反型层而吸引的电子(至于为何分为两个电容,下文讲解MOS管开关过程的时候继续解释)。

PART-2 MOS管导通过程

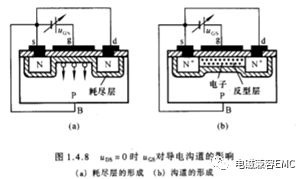

MOS管的导通过程,其实就是形成反型层导电沟道的过程。

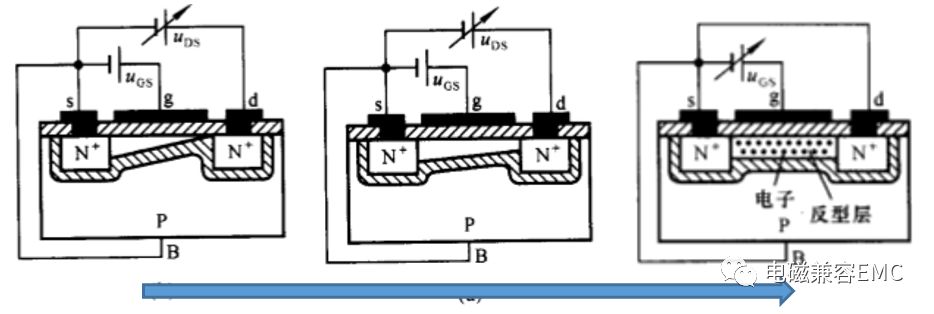

重新看回这张图,当栅极G与源极S之间加一个正偏电压Vgs时,增强型N-MOSFET的P型半导体衬底中的电子受电场作用,会被吸引到栅极附近,同时连接两个N型半导体区域,形成反型层导电沟道。

!敲黑板!划重点!

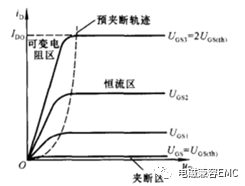

导电沟道刚刚形成的时候那个正偏电压Vgs,称为开启电压Vgs(th)(或称为“阈值电压”);Vgs大于Vgs(th)的这一段电压区间,称为可变电阻区,MOS管漏极D到源极S的导通阻抗随Vgs增大而降低;当Vgs大于2×Vgs(th)之后,基本视为导通阻抗Rds-on降为最低,s且在温度一致时保持不变,此时增强型N-MOSFET视为完全导通。如下图

故设置开关MOS管驱动电压时,一般设置为远大于2×Vgs(th)。

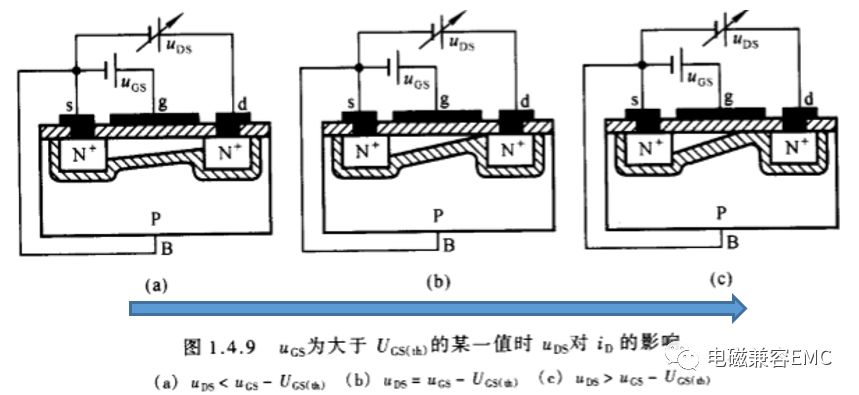

模电书中给了这么一组图,阐述了当Vgs大于开启电压时,Vds的增大对于流过MOS管的电流iD的影响。

实际上将图序反过来,可以近似地模拟MOS管开启过程反型层的行程过程:

MOS管导电过程可近似理解为:

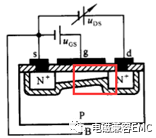

①由于电场作用,先形成靠近源极S区域的反型层,使得MOS管漏极D到源极S之间可以导通并流过电流iD。

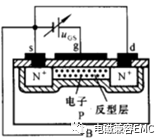

②iD开始流过的同时,反型层逐渐向漏极D扩大,并最终使得靠近漏极D的反型层与靠近源极S的反型层宽度基本一致。

③反型层继续扩大,Rds-on一直降至完全导通,保持不变。

给Cgd充电的过程,Vgs保持不变,此时Rds-on较大,当流过电流iD一定时,MOS管损耗较大。

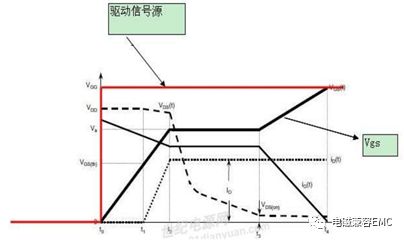

当栅极G外接电压,MOS管导通过程,Vgs保持不变的区间称为米勒区间,由于反型层的形成过程而影响的Vgs、Rds-on及MOS管损耗变化过程的现象称为米勒效应。下面结合波形详细介绍一下米勒效应。

这是在论坛中一个博客截的一个图,已经很形象地体现了外加栅极驱动性号时,MOS管相关电流电压的变化情况。

(见底部原文链接)

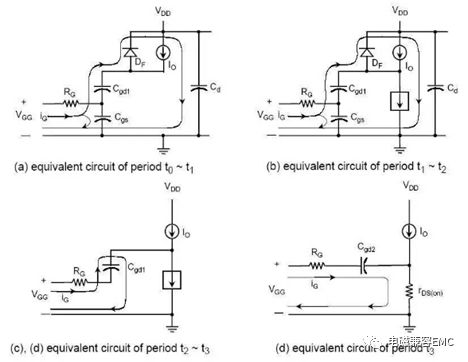

t0-t1:由于栅极电压未到达开启电压,MOS管未导通,如下图

t1-t2: Vgs到达了开启电压,MOS管开始导通,反型层不断拓宽,栅极电压继续升高,如下图:

t2-t3: MOS管位于可变电阻区,保持持续导通,反型层往漏极侧拓宽(大致如下图红框中区域),栅极电压不变,进入米勒平台:

t3-t4:反型层基本拓宽到宽度一致的情况,栅极继续施加驱动电压,整个反型层一齐拓宽,直至栅极电压Vgs与驱动信号源一致,导通阻抗Rds-on:

用MOS管模型看的话,大致如下侧四图,也就解释了为什么反型层的输入电容Ciss要被划分为两个电容Cgs跟Cgd,是因为二者的充电顺序不一样:

PART-3MOS管参数

相信各位读者对MOS管的参数已经耳熟能详了,这里就不再详细说明了,参照上文博客中给出的介绍,这里仅对其中部分参数进行补充说明:

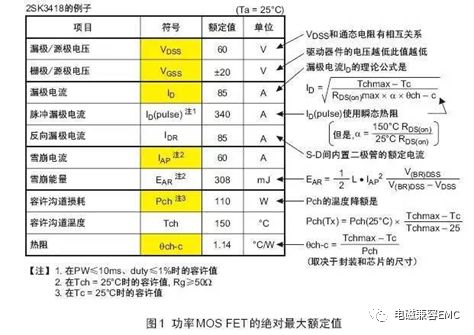

1)、功率MOSFET的绝对最大额定值:

注①:漏源最大电压VDSS,可视为反向施加在体二极管两端的电压值,故只有一个方向。

注②:栅源最大电压VGSS,即施加在栅极电极与源极电极之间的电压,由于栅极与P型半导体衬底中加了SiO2绝缘层,只要电压绝对值超过绝缘层耐压均会击穿,故有两个方向“±”。

注③:漏级最大电流ID与体二极管流过的反向漏级最大电流IDR(或称为IS)一般规格书中数值一致,均为流过N型半导体与P型半导体衬底形成的PN结的最大电流。

注④:ID(pulse)需要看施加电流的脉冲宽度,脉宽不一致的不能沿用规格书数据。

注⑤:雪崩电流IAP同样需要关注脉冲宽度。

2)、静态电特性

注①:Vgs(off)其实就是开启电压Vgs(th),只不过这里看的角度不一样。

注②:看完前文的读者应该知道为什么这里两个Rds(on)大小有差异,不知道的回去前面重新看。

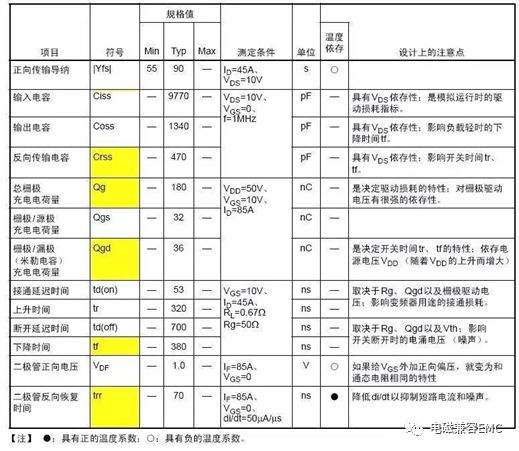

3)、动态点特性

注①:Ciss = Cgs + Cgd ;Coss = Cds ;Crss = Cgd

注②:MOS管开启速度最主要关注的参数是Qg,也就是形成反型层需要的总电荷量!

注③:接通/断开延迟时间t d(on/off)、上升/下降时间tr / tf,各位工程时使用的时候请根据实际漏级电路ID,栅极驱动电压Vg进行判断。

MOS的介绍基本如上,时间及篇幅关系文中不涉及具体电路讲解。图源及主要参考书籍为《模拟电子技术基础,(童诗白.第4版)》,《电子技术基础.模拟部分.(康华光.第5版)》,各位工程师工作时多看会大学课本有时会有不同的收获。

-

斯丢彼得阿格雷雷

2018-11-29

0 回复 举报你这有错误吧,B是在N型还是P型中? 收起回复

斯丢彼得阿格雷雷

2018-11-29

0 回复 举报你这有错误吧,B是在N型还是P型中? 收起回复

-

单片机基础知识简介2012-08-05 0

-

MOS管的基础知识/主要参数/应用电路2021-01-20 0

-

了解一下MOS管的种类以及相关基础知识2023-02-21 0

-

DAQ基础知识简介2010-03-26 567

-

PCB基础知识简介2009-04-07 3643

-

PLC基础知识简介2009-06-20 1064

-

三极管基础知识及检测方法简介2009-11-28 1501

-

安规电容基础知识简介2009-11-28 1495

-

MOS管的基础知识2022-07-22 1667

-

关于mos管的基础知识2023-01-29 3752

-

分享几种常用的三极管和MOS管的基础知识及应用电路2023-03-30 4643

-

MOS管的基础知识介绍2023-05-18 1953

-

关于MOS管的基础知识2023-05-23 885

全部0条评论

快来发表一下你的评论吧 !