Kintex7的SERDES的结构图 CPRI应用的应用

可编程逻辑

描述

Kintex7系列的GTX,以其良好的性能和功耗表现,已经成为业界FPGA选型时的明星。由于其良好的DFE性能,它能提供高达12.5Gbps的过背板能力,能支持在插损高达30dB的信道上可靠传输。在众多的SERDES应用中,有些应用比较特别,那就是需要在实际运行过程中动态切换GTX的链路速率,如无线中的CRPI接口,需要同时支持9.8G,4.9G,2.4G等众多速率。那么,如何能做到可靠地进行速率切换呢?本文就此作为主题,希望能充分发挥GTX的优势。

1. 背景知识GTX结构

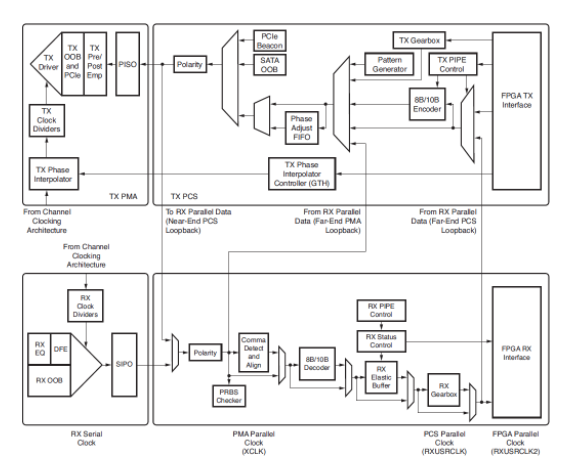

Kintex7的SERDES的结构图如图1。

图1 Kintex7 GTX结构图

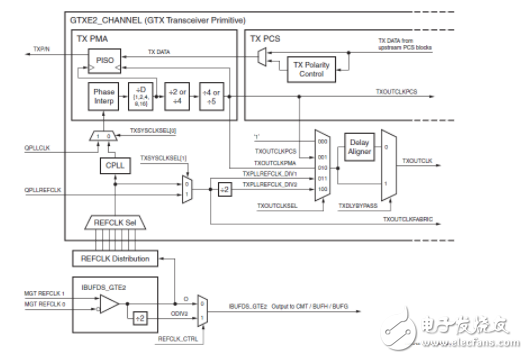

以发送方向为例,参看图2的发送方向的时钟分布图:

图2 GTX 发送方向时钟分布图

Kintex7在进行链路速率切换时,主要有如下几种办法:

1) 切换QPLL/CPLL的参考钟源头;

2) 通过DRP接口修改QPLL/CPLL的参数设置

3) 切换QPLL/CPLL提供链路时钟;

4) 调整PMA的分频系数。

GTX工作模式介绍

在GTX内部,有2种工作模式:LPM模式和DFE模式。

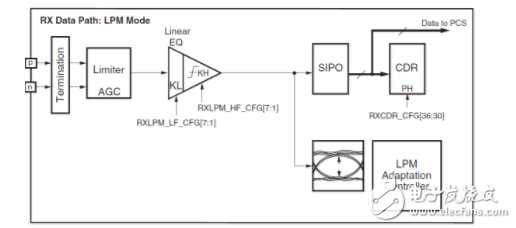

LPM(Low Power Mode)模式是低功耗模式,其主要支持低插损信道,链路速率《11.2G,信道插损在12dB以下的情况。在LPM模式中,CTLE和baseline wander cancellation都是全自动的,不需要手工调整。LPM模式的结构图如下:

图3 LPM模式下GTX结构图

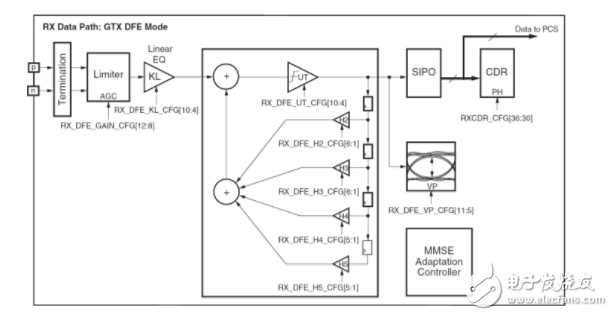

DFE模式则提供更好的信道补偿,其能够支持高达12.5G的链路速率,并在信道插损大于8dB的场景下有良好表现。DFE和CTLE不同,它不会放大噪声和串扰,能纠正信道不连续引起的反射。它能自动利用AGC,CTLE,DFE和baseline wander cancellation来完成信道补偿,同时也支持CTLE手动模式。DFE模式下GTX的结构图如图4。

图4 DFE模式下GTX结构图

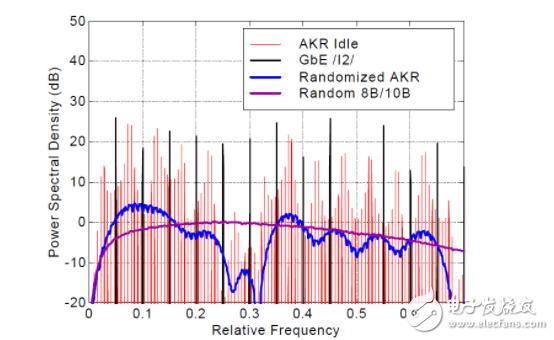

8B/10频谱特性介绍

为何单独介绍8B/10B呢?主要是因为采用8B/10B编码的系统,其当系统空闲时,大体上都会发送固定码型的数据,如802.3中定义的/I1/和/I2/。固定码型的数据其频谱比较离散,有太多的毛刺,不利于EMI也不利于DFE进行补偿跟踪。一般来说,当链路速率》5Gbps时,只是简单的采用8B/10B编码已经不适合。众多协议一般此时会使用加扰进行替代或者在8B/10B编码前先对数据进行加扰。

在实际应用中,可以通过示波器对信号进行快速FFT分析,得到其频谱特性。如果频谱毛刺比较多,那么就需要考虑在发送端改善信号频谱。图5是8B/10B编码下,不同的模式的频谱。从图上可以看出,发送固定序列的AKR IDLE和GbE下的/I2/,其频谱毛刺都很多,不适合于DFE工作。

图5 频谱图

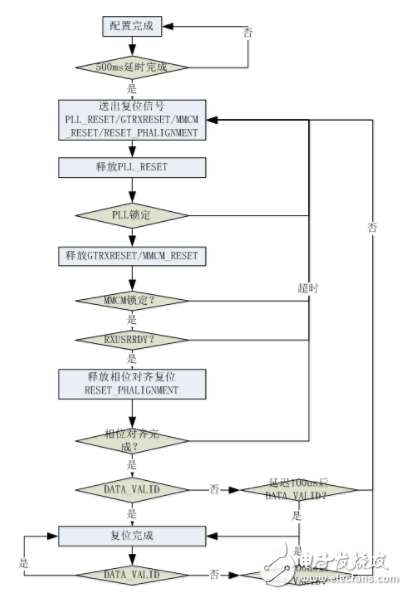

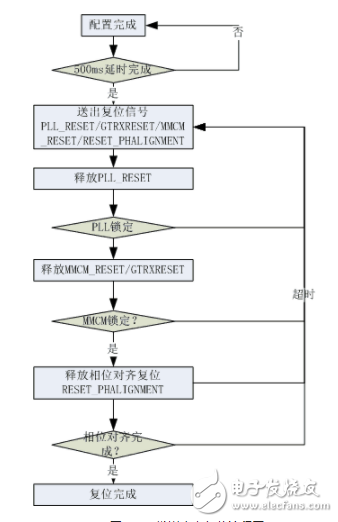

GTX复位流程

如果是以ISE14.4例化GTX,那么GTX的IP版本应该是2.4。在此版本的example code中,对于GTX的复位流程有充分的考虑。其可以作为大家设计GTX的复位处理的样板。复位顺序的一个总体原则是:从PLL,到PMA,再到PCS,再到用户逻辑,依序处理。需要注意的是,GTX的复位都以统一的GTRXRESET/GTTXRESET来启动,而复位模式则配置成sequential reset。

在接收方向,复位流程大致为:

图7 GTX接收方向复位流程图

在发送方向,复位流程大致为:

图8 GTX发送方向复位流程图

2. GTX配置介绍

GTX的配置需要重点关注的是:1) AGC;2) CTLE;3) RXCDR_CFG;4) 发送方向的Pre-emphasis。本文主要讨论前面3项。

LPM模式下,AGC和CTLE都是全自动模式。其也提供了HOLD,OVERRIDE端口进行控制,如{RXOSHOLD, RXOSOVRDEN},{RXLPMLFHOLD, RXLPMLFKLOVRDEN},{RXLPMHFHOLD, RXLPMHFOVRDEN}。

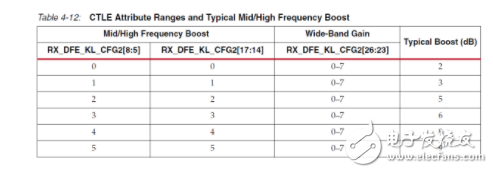

在DFE模式下,同样也提供了HOLD,OVERRIDE端口进行控制各种属性。其还分为CTLE Auto模式和CTLE Manual模式。CTLE Auto模式的启用可以通过DRP接口修改如下属性来完成。

RX_BIAS_CFG[5:4] = 2‘b11

RX_DFE_KL_CFG2[26:23] = 4’b0111

RX_DFE_LPM_CFG[5:2] = 4‘b0010

而在CTLE Manual模式下,通过DRP接口修改RX_DFE_KL_CFG2属性,可以调整CTLE的频率响应曲线,从而获得适合于信道的值。

图9 DFE模式下CTLE的设置

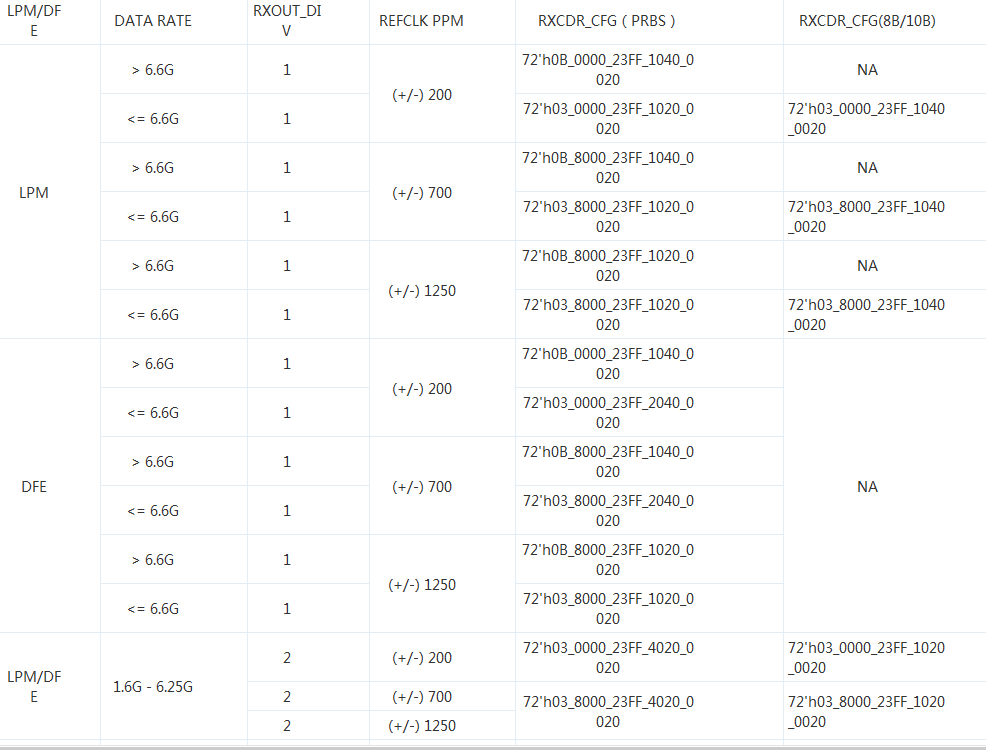

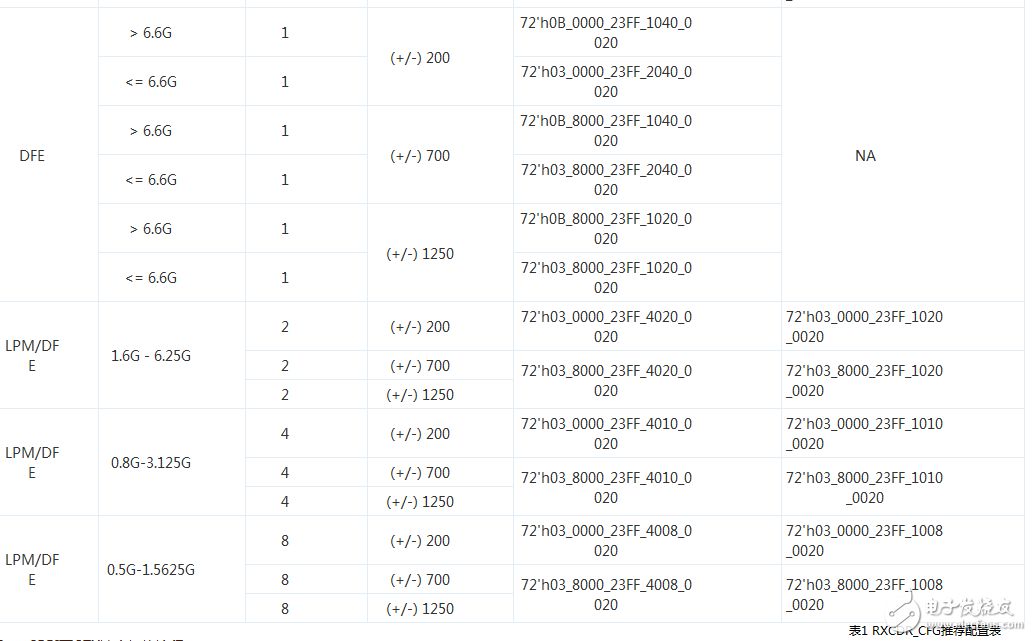

除去上面的配置,影响GTX性能的还有RXCDR_CFG属性,其也只能通过DRP接口完成修改。具体推荐配置值参看表1。

3. CPRI下GTX速率切换流程

CPRI一般分如下几个工作链路速率:

1) 2.4576 Gbps

2) 3.072 Gbps

3) 4.9152 Gbps

4) 6.144 Gbps

5) 9.8304 Gbps

在实际应用中,如果最高速率需要支持到9.8304Gbps,那么QPLL是必须启用的。由于每个Quad只有1个QPLL,如果Quad里的4个GTX都要单独调节链路速率,那么QPLL就只能工作在9.8304Gbps。下面又分2个情况进行讨论:

a) 支持的速率有倍速关系;

只需要通过修改PMA部分的RXOUT_DIV和TXOUT_DIV属性,或者RXRATE和TXRATE端口即可,而QPLL只工作在9.8304Gbps上。

b) 支持的速率没有倍速关系。

除9.8304Gbps及其他和9.8304Gbps有倍速关系的速率外,其他速率的支持通过CPLL来支持。在CPLL不使用的时候可以讲起PowerDown。

无论上面的哪种配置场景,其最基本的速率切换流程都不会有太大区别。其切换流程大体都应如下:

Step1:通过DRP接口更新相关属性:

RXCDR_CFG,值具体参照表1

RX_BIAS_CFG

RX_DFE_KL_CFG2,值具体参照图9

RX_DFE_LPM_CFG

RXOUTDIV

TXOUTDIV

Step2:复位GTX,参照GTX的复位流程。

值得注意的是,由于不同的链路速率下信道的表现不一致,RXCDR_CFG,RX_DFE_KL_CFG2的最佳值都会有不同,所以在切换速率时,必须通过DRP接口将最佳值配置到GTX。在切换LPM模式和DFE模式时,也必须从PMA开始进行一次完整复位。

-

万能外圆磨床结构图2009-03-18 9933

-

中断结构图2017-03-19 0

-

控制系统的结构图2021-06-30 0

-

化学电源的结构图2009-11-02 607

-

二极管结构图2009-11-11 944

-

高压油泵结构图2008-04-12 11188

-

机油滤结构图2008-04-12 3688

-

汽车变速箱结构图2008-05-29 19841

-

离心泵的结构图2008-07-14 10212

-

滚齿机的结构图2009-03-18 7273

-

MOS管结构图2009-04-06 4575

-

摄像管靶结构图2009-08-02 1313

-

Tadiran 电池的结构图2009-10-30 1654

-

微型四轴PCB结构图2016-06-03 831

-

自控控制:结构图2016-12-30 1362

全部0条评论

快来发表一下你的评论吧 !