将RF信号转换为数字信号的CMOS转换器

模拟技术

描述

从频率计数与合成到传感器信号调整等很多应用都需要将RF 信号转换为数字逻辑电平。在这些情况下,设计者一般采用一个高速电压比较器完成RF到数字信号的转换工作。由于电压比较器具有高增益,它们一般有很好的灵敏度,但也会带来一些问题。高速比较器价格高,很难找到现成的商品,并且易于被快速淘汰。

图1中的电路可以为高达180 MHz的频率提供一种有吸引力的方案。设计中的IC是一个74LVCU04极高速CMOS六反相器,可以是采用现成的,也可以从很多来源获得。此外,很多设备中可能已经含有三个未用到的反相器。一个反相器IC1A作为线性前置放大器工作,构成转换器的输入级。偏置电阻R3使反相器的输入、输出电压平均在电源电压的一半处[VO1=VI1=(VDD/2)],从而使反相器进入自己的线性区。由于在RF段上,极高速CMOS反相器的交流增益相对较低,(VO1/ VI1)≈7,前置放大器后要增加一个增益级。增加的反相器级联方案在低频和直流下,当没有施加RF信号源时稳定性不佳。

图1中的电路采用了一种基于施密特触发器和放大器电路的拓扑(IC1B和IC1C),从而解决了这个问题,它包括一个与频率有关的正反馈网络,由R1、R2、CD1和CD2构成。随着输入频率的不同,网络可表现出两种特性:在高频时,去耦电容器对CDC1和CDC2将反馈电阻器R1短路,从而抵消了由正反馈网络R1、R2与反相器IC1B的输入电容引起的时间常数。因此,在高频下,三个反相器IC1A、IC1B和IC1C表现为三个级联的高速放大器,可以实现最佳的输入信号带宽。在直流和低频时,耦合电容器对CD1和CD2的影响可以忽略不计,而反相器IC1B、IC1C与正反馈网络R1、R2可以起到一个施密特触发器电路的作用。为了对VS的输入灵敏度与确保比较器输出的无条件稳定之间做出折衷,要对施密特触发器输入VO1处的高、低阈值电压VTH和VTL做出选择。公式1和公式2分别设定高、低阈值电压:

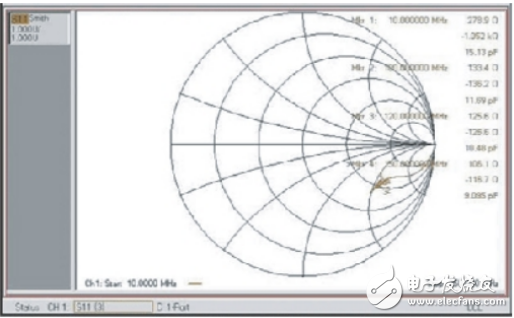

为中和较高频率时灵敏度下降问题,在比较器的输入端增加了一个由L1和C1构成的低Q阻抗匹配网络。由于设计目标是在高至160 MHz获得可接受的灵敏度,因此网络将50Ω的RF源与运行在150 MHz的IC1A的输入阻抗ZI1作匹配。不幸的是,数字IC 的制造商通常不会说明逻辑器件的输入阻抗。因此在设计匹配网络时,首要任务是用Agilent的矢量网络分析仪测量第一个反相器IC1A输入VI1的散射参数S11。图2显示了反相器S11参数的史密斯特性图。

已知

其中ZC=50Ω,可以用图2中的数据提取第一个反相器在所需频率处的输入阻抗。在150 MHz时,得到ZI1= 106.1Ω-j 116.7Ω(在图2的标记4处)。要确定匹配网络中各元件的值,可以用任何一种软件工具(参考文献1与2)。如果你不熟悉史密斯特性图的计算,也可以用下列方法进行分析:

1. 用串-并转换公式(公式4和5),将第一个反相器的输入阻抗转换为并联形式:

将这些公式用于150 MHz时,得到:RP=233Ω,XP=213Ω。(在150 MHz下,XP代表输入阻抗,CP=5 pF。)

2.算出第一个反相器输入阻抗RP和50Ω RF源之间实现匹配的网络匹配初始值。用公式6和7计算出匹配网络中各元件的值(参考文献3)。

将这些公式用于150 MHz,得到L1≈100 nH,C1 +CP≈8.7 pF。

3. 从式7中减去反相器的输入电容CP =5 pF,计算出C1的值:

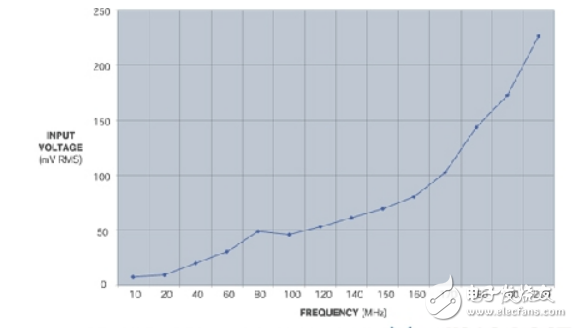

搭建电路时,使用最接近于计算值的标准元件:L1=100 nH,C1=3.6 pF。如图3中输入频率与灵敏度的关系曲线所示,100 MHz ~ 170 MHz频率时电路的灵敏度增加,这清楚地证明了阻抗匹配网络的有效性。可以在选定频率下将这种方法用于其它感兴趣的任何频率段,实现电路灵敏度的优化。在10 MHz~180 MHz输入信号范围内,RF至数字逻辑转换器的功耗变化不大。最差条件下,3.3V供电电压下消耗的电流不超过58 mA。

-

怎样将模拟信号转换为数字信号2015-08-07 0

-

编码器转换为数字信号的电路2015-09-28 0

-

RF信号和数字信号转换2019-06-21 0

-

IF/RF数据转换器中的数字信号处理在实际应用中是如何工作的呢?2019-08-01 0

-

如何把模拟电压信号转换为数字信号?2019-11-03 0

-

风门状态返回信号转换为数字信号2021-06-16 0

-

模拟信号如何才能转换数字信号2021-07-26 0

-

数字转换器是指什么2021-08-02 0

-

ADC模拟信号是怎样转换为数字信号的2021-11-24 0

-

多功能信号转换器的相关介绍2021-12-07 0

-

如何将模拟信号转换为数字信号MCU呢2022-02-17 0

-

如何将模拟音频信号转换为数字信号输出?2022-06-29 0

-

信号转换器的主要作用2023-02-14 3228

-

多通道振弦传感器信号转换器 将振弦、温度传感器信号转换为RS485数字信号和模拟信号输出2023-08-01 364

-

IF/RF数据转换器中数字信号处理说明2023-11-23 84

全部0条评论

快来发表一下你的评论吧 !