ad9854中文资料汇总(ad9854引脚图及功能_内部结构及应用电路)

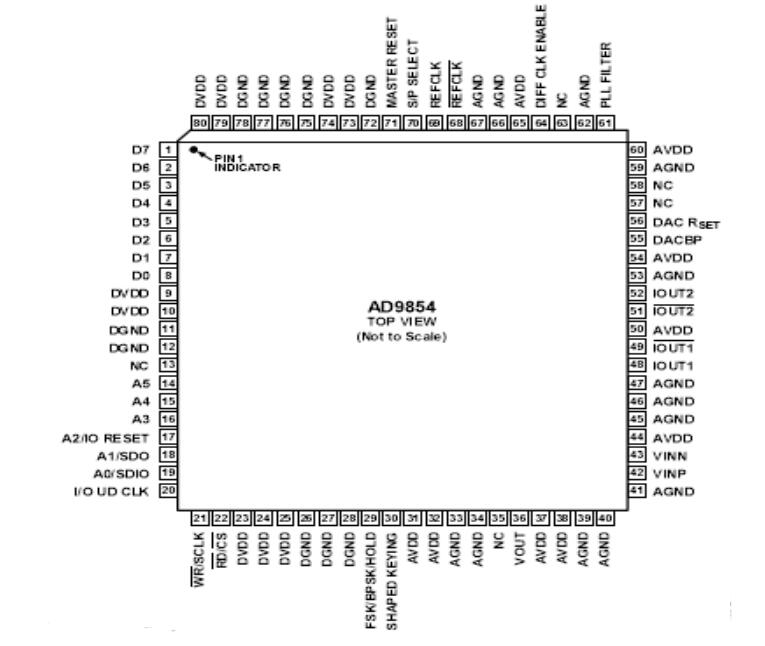

芯片引脚图

描述

AD9854概述

AD9854数字合成器是高集成度的器件,它采用先进的DDS技术,片内整合了两路高速、高性能正交D/A转换器通过数字化编程可以输出I、Q两路合成信号。在高稳定度时钟的驱动下,AD9854将产生一高稳定的频率、相位、幅度可编程的正弦和余弦信号,作为本振用于通信,雷达等方面。AD9854的DDS核具有48位的频率分辨率(在300M系统时钟下,频率分辨率可达1uHZ)。输出17位相位截断保证了良好的无杂散动态范围指标。AD9854允许输出的信号频率高达150MHZ,而数字调制输出频率可达100MHZ。通过内部高速比较器正弦波转换为方波输出,可用作方便的时钟发生器。

AD9854特征

·300M内部时钟频率

·可进行频移键控(FSK),二元相移键控(BPSK),相移键控(PSK),脉冲调频(CHIRP),振幅调制(AM)操作

·正交的双通道12位D/A转换器

·超高速比较器,3皮秒有效抖动偏差

·外部动态特性:

80 dB无杂散动态范围(SFDR)@ 100 MHz (±1 MHz) AOUT

·4倍到20倍可编程基准时钟乘法器

·两个48位可编程频率寄存器

·两个14位可编程相位补偿寄存器

·12位振幅调制和可编程的通断整形键控功能

·单引脚FSK和BPSK数据输入接口

·PSK功能可由I/O接口实现

·具有线性和非线性的脉冲调频(FM CHIRP)功能,带有引脚可控暂停功能

·具有过渡FSK功能

·在时钟发生器模式下,有小于25 ps RMS抖动偏差

·可自动进行双向频率扫描

·能够对信号进行sin(x)/x校正

·简易的控制接口:

可配置为10MHZ串行接口,2线或3线SPI兼容接口或100MHZ 8位并行可编程接口

·3.3V单电源供电

·具有多路低功耗功能

·单输入或差分输入时钟

·小型80脚LQFP 封装

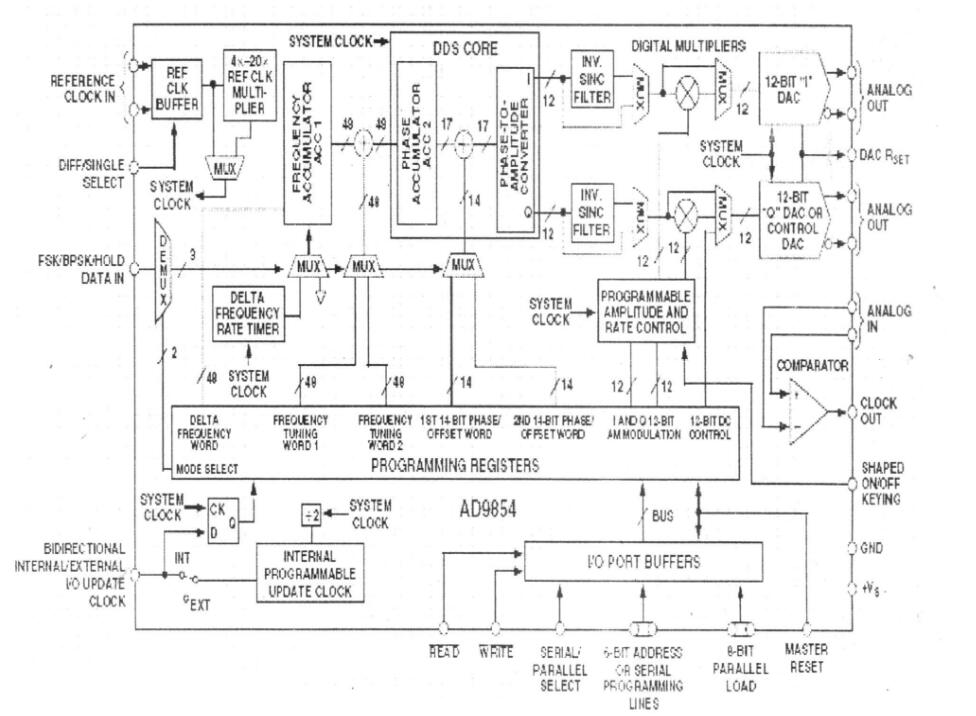

ad9854内部结构框图

AD9854的结构与功能

AD9854采用3.3V单电源供电,允许电源误差为+5%,最大功耗4.06W。由于整体功耗很大,器件内部控制寄存器设置了可以关断比较器、QDAC、数字部分、PLL、反辛格滤波器等模块的关断位,用户可以将未使用的模块关闭,需要时再打开,减小芯片功耗和发热。AD9854的控制接口采用节省I/O口的2线或3线SPI协议串行接口和100MHz高速并行接口。AD9854片上重要模块介绍如下:

(1)DDS核

AD9854中的新型高速DDS核提供了48位频率分辨率,在系统时钟300MHz的情况下仍能够精确到1,保持17位即可确保该芯片具有优秀的无杂散动态范围(SFDR),100MHz()输出下SFDR达到80dB。

根据奈奎斯特采样定理,在300MHz系统时钟下,AD9854理论上最高可以输出150MHz的信号,在实际应用中,输出信号达到150MHz时,信号质量很差,幅度衰减非常大,实际可用最高频率大概在130MHz左右。AD9854的输出信号数字调谐频率可以达到每秒1亿次。

(2)双路正交DAC

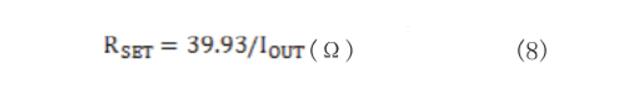

AD9854内部有两路DAC——IDAC和QDAC。两路DAC的满量程输出幅度由第56引脚的电阻——中电流决定,最大不超过20mA,当设置满量程电流在20mA时可获得最佳SFDR性能的电流由下式决定:

式中,为输出满量程电流。在输出高频信号时,总谐波失真变得明显,双路DAC的满量程电流更应合理设置以获得最佳SFDR。两路DAC都可以由程序设定是否经过反辛格滤波器。

IDAC内部固定于正弦表连接,QDAC可配置为与内部余弦表连接或独立出来,作为一个单独的高速电流DAC使用,此时QDAC的输出幅度由用户写入的12位二进制补码决定。当QDAC不用时可以关断以降低功耗。

(3)反辛格滤波器(反sinc滤波器)

DDS是靠高速DAC将模拟正弦信号量化输出的过程,输出信号是由一个一个小台阶构成的。这时信号的频谱为sinc包络,由于DAC的零阶保持效应,输出信号的频谱为sinc包络与脉冲流经过付里叶变换的乘积,所以输出频谱会有遵从sine响应的固有的畸变。反辛格滤波器的频谱响应为反sinc包络,数据经过该滤波器就可以校正sinc包络形的畸变。反辛格滤波器使得宽带信号在低频和高频使得幅度变化不会太大,如QPSK信号。反辛格滤波器能起到稳定幅度的作用,但功耗很大,在300MHz频率下达到400mA以上,且会带来插入损耗。

(4)时钟倍频器

AD9854的参考时钟为300MHz,在最大时钟频率下页能够精确到1。但是这是基于所提供的时钟源为高精度时钟源,如何提供这一高精度、高频参时钟是一个不得不解决的问题。

有厂商生产这样的振荡器,但性价比太低,一个300MHz的高精度振荡器不比AD9854便宜。而且300MHz的振荡信号还很容易耦合到其他电路中,干扰有用信号。为此,AD9854内设了一个4-20倍可编程时钟倍频器,用户可以外接一个高精度、低频的时钟源,然后经内部倍频后再共给DDS核使用。需要指出的是,AD9854提供两种时钟输入方式——单端输入和双端输入。建议用户将单端时钟经用变压器或时钟芯片(如MC100LVEL16)把单端时钟转换为差分信号再输入到DDS芯片,这样能获得更好的性能。

(5)调幅模块

AD9854在内部还集成了调幅模块,可以通过程序设定DAC输出最大幅度。可以通过高速控制器,如FPGA、DSP对信号进行调幅操作,同时可以用此功能软件稳幅。

(6)比较器

AD9854的片上比较器具有300MHz切换速率、3ps均方根抖动,输出可以用作其他电路的高精度时钟源。

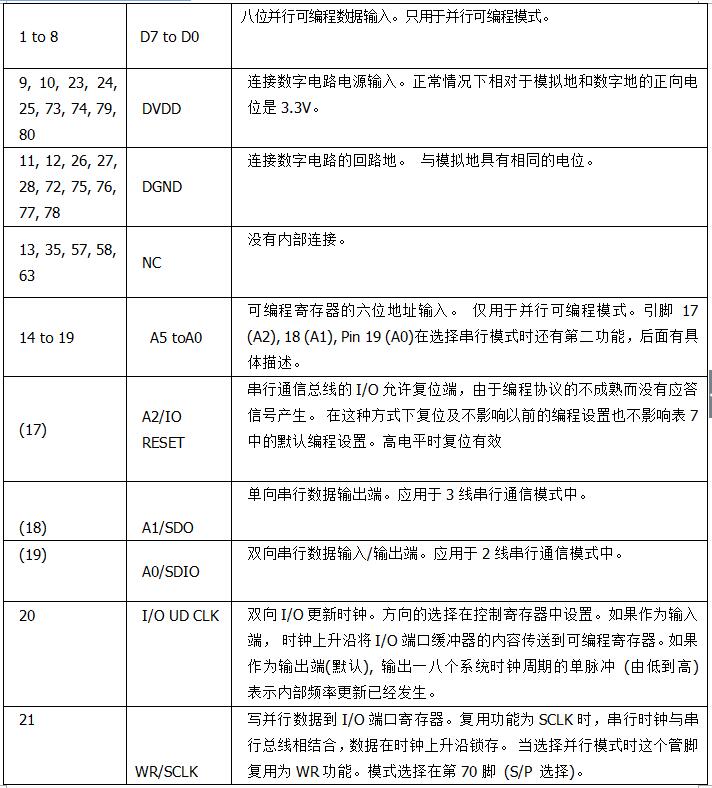

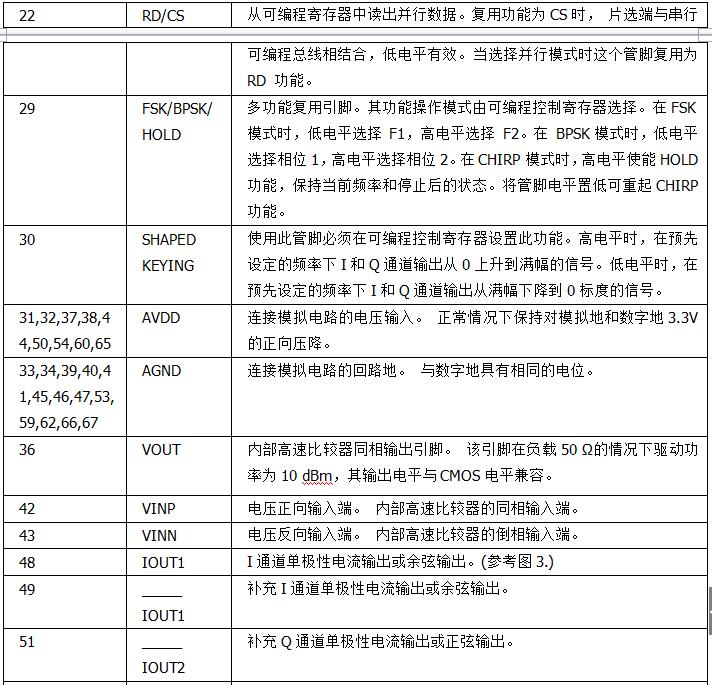

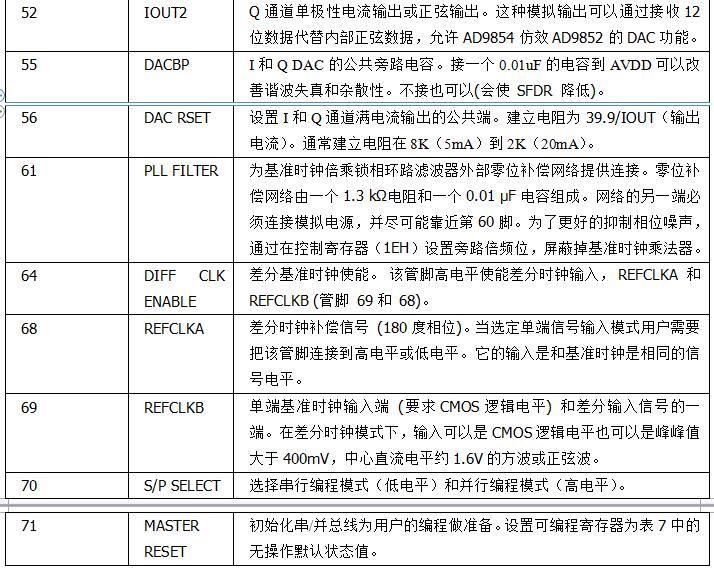

AD9854引脚及功能

引脚描述:

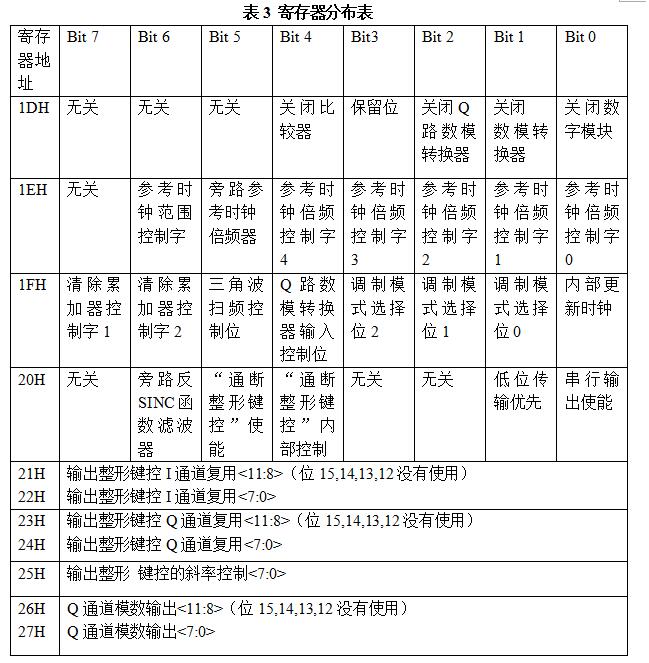

AD9854的编程

AD9854的各寄存器列出在下表,包含各各功能的片内编程信息。很多应用要求很小的编程规模去装配AD9854,就可以使用了,实现功能了。但有一些要求用户使用所有的12个寄存器入口地址。AD9854支持8位并行I/O操作或一位SPI-compatible串行I/O操作。所有入口寄存器能读和写,在每个I/O操作模式下。S/P选择,引脚70,用于I/O模式选择。若系统使用并行I/O模式,必须连接S/P选择引脚到VDD。若系统操作在串行模式,必须连接S/P选择引脚到GND。

不使用模式,I/O口数据写入缓冲寄存器,不影响该部分操作直到缓冲寄存器传输数据到寄存器数据库。信息传输同时产生在系统时钟,两种产生方式:

(1)内部控制在某一由用户编程产生的速率

(2)由用户外部控制,I/O操作能在没有REFCLK情况下进行,但数据从缓冲期传输到存储器,没有REFCLK是不行的。能从该文献更新时钟章节中了解到更多的详细信息。复位管理——逻辑高电平有效,必须保证电平不小于10个系统时钟周期的持续时间。复位主要引起通信总线的初始化并载入默认值到内部或外部的时钟更新段。

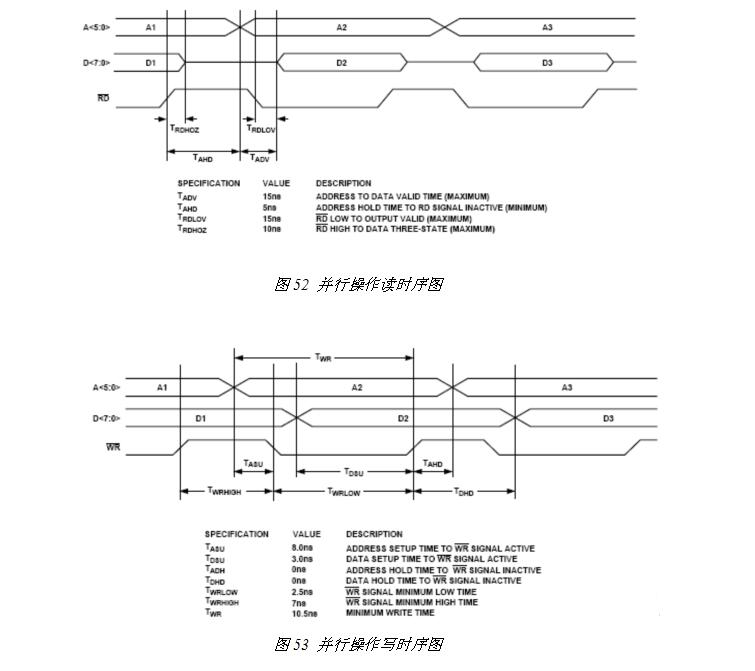

并行输入输出操作

在S/P选择引脚被拉为高电平时,并行输入输出模式被激活。这种输入输出口与标准工业DSPs 和microcontrollers相兼容。6个地址位,8个双向数据位,和分离的写/读控制输入来补足这输入输出口引脚。

并行输入输出操作模式允许到1/10.5纳秒对每个寄存器进行单字节操作。对寄存的回读操作主要用来优化对AD9854的设计 (读寄存器不能保证100 MHz的操作速度,这一点他们为只是软件调试准备的)。

并行输入输出操作时序图如图52 和图53 所示。

两款ad9854应用电路

应用电路一:

这里采用了AD9854 这款DDS 芯片, 它在300 MHz 时钟驱动下, 按照乃奎斯特采样定律可以产生最高150 MHz 的信号,为了得到信号较好的频率则一般只得到最高100 MHz 的信号。若要得到高于100 MHz 的信号, 则可采用其高次谐波得到。基于AD9854 的信号发生电路如图 所示:

应用电路二:

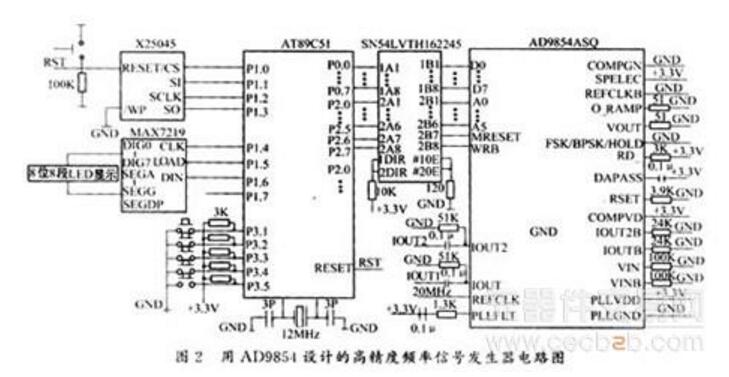

下面给出一种用AD9854开发高精度频率信号发生器的简易方法,开发者只需要熟悉MCS-51单片机编程即可。该系统具有开发周期短,开发成本低的特点,也可以作为探索AD9854功能的一种方法,它的电路原理图见图2。

系统主要由DDS芯片AD9854、单片机AT89C51、看门狗定时器X25045和LED显示驱动芯片MAX7219组成。在这个系统中提供了8位七段LED显示器,其中前五位为输出频率值,显示范围为00.000~99.999MHz,后三位为幅度显示位,显示范围为0~999,表示幅值从零幅度到满幅度的变化。

ad9854相关文章:

ad9854应用电路图大全(五款ad9854信号发生/频率发生器/正交信号源电路)

ad9854相关下载:

-

AD9854的中文资料2013-08-30 0

-

AD9851和AD9854资料2013-09-01 0

-

ad9854引脚图及功能2017-11-03 4193

-

基于AD9854产生MSK调制信号详细说明2018-05-16 4443

-

16位单片机对AD9854控制的探讨2018-05-16 6159

-

ad9854应用电路图大全(五款ad9854信号发生/频率发生器/正交信号源电路)2018-05-16 8512

-

ad9854单片机程序详细说明(ad9854结构框图及电路)2018-05-17 20915

-

一文看懂ad9852与ad9854区别2018-05-17 9041

-

stm32驱动ad9854程序分享_ad9854构成信号发生器电路2018-05-17 15032

-

基于FPGA控制AD9854产生正弦波2018-05-17 6272

-

基于AD9854的正交扫频信号源设计2018-05-18 4147

-

AD9854参考代码2021-03-18 674

-

AD9854评估板原理图2021-04-23 510

-

AD9854/AD9852评估板说明2021-05-11 468

全部0条评论

快来发表一下你的评论吧 !