74ls192计数器应用电路图大全(五款电子骰子/计时/定时电路)

IC应用电路图

描述

74ls192计数器应用电路图一:电子骰子电路

电子骰子是为那些经典游戏设计的一个电路。电路由定时器、计数器和几个LED构成。当开关被按下时,555定时器在非稳态模式送出脉冲,74LS192计数器产生序列输出,点亮了一系列的LED连接到模拟骰子。两个与门被用于每当计数器输出是7重置计数回1。因此,该电路不是真正随机的,但自然弹跳存在于一个按钮,操作更慢则振荡器的正常人类能力使电路的输出好像是随机的。

配件:

R1,R5,R6 22K 1/4W电阻

R2 10K 1/4W电阻

R3 4.7K 1/4W电阻

R4 150K 1/4W电阻

R7 - R13 330欧姆1/4W电阻

C1 1uF的电解电容

C2 4.7uF的电解电容

D1 1N4148信号二极管

D2 - D8 红色/绿色/黄色LED

Q1 2N3904 NPN晶体管

U1 555定时器IC

U2 74LS192 4位计数器IC

U3 74LS08四与门集成电路

S1 单刀单掷瞬时按键开关

备注:

按下并按住S1导致LED的快速循环。释放该按钮锁定模式,并显示从1数到6的一个数。

在构建电路,确保如图所示在原理图上定位的LED。否则,骰子图案会显得怪异。

两个电路当然可以,双骰子。

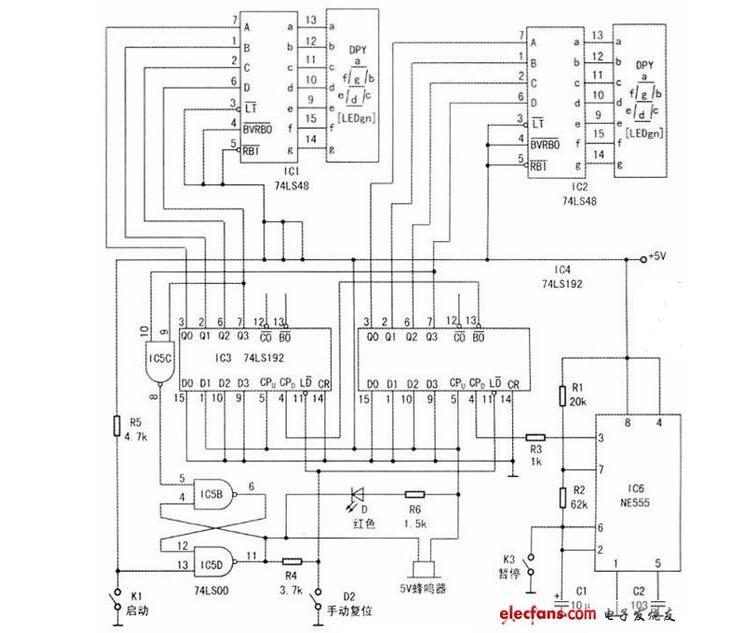

74ls192计数器应用电路图二:计时电路

本设计采用555作为振荡电路,由74LSl92、74LS48和七段共阴LED数码管构成计时电路,具有计时器直接复位、启动、暂停、连续计时和报警功能。该电路制作、调试简单,采用普通器件,一装即成。

由555定时器输出秒脉冲经过R3输入到计数器IC4的CD端,作为减计数脉冲。当计数器计数计到O时,IC4的(13)脚输出借位脉冲使十位计数器IC3开始计数。当计数器计数到“00”时应使计数器复位并置数“24”。但这时将不会显示“00”,而计数器从“01”直接复位。由于“00”是一个过渡时期,不会显示出来,所以本电路采用“99”作为计数器复位脉冲。当计数器由“00”跳变到“99”时,利用个位和十位的“9”即“1001”通过与非门IC5去触发RS触发器使电路翻转,从11脚输出低电平使计数器置数,并保持为“24”,同时D发光二极管亮,蜂鸣器发出报警声,即声光报警。接下K1时,RS触发器翻转11脚输出高电平,计数器开始计数。

若接下K2,计数器立即复位,松开K2计数器又开始计数。

若需要暂停时,按下K3,振荡器停止振荡,使计数器保持不变,断开K3后,计数器继续计数。

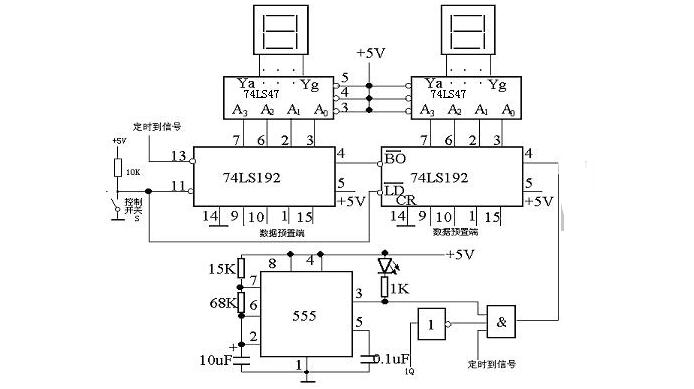

74ls192计数器应用电路图三:定时电路

由节目主持人根据抢答题的难易程度,设定一次抢答的时间,通过预置时间电路对计数器进行预置,计数器的时钟脉冲由秒脉冲电路提供。可预置时间的电路选用十进制同步加减计数器74LS192进行设计,具体电路如下图所示。

原理及设计:该部分主要由555定时器秒脉冲产生电路、十进制同步加减计数器74LS192减法计数电路、74LS48译码电路和2个7段数码管即相关电路组成。具体电路如图3所示。两块74LS192实现减法计数,通过译码电路74LS48显示到数码管上,其时钟信号由时钟产生电路提供。74192的预置数控制端实现预置数,由节目主持人根据抢答题的难易程度,设定一次抢答的时间,通过预置时间电路对计数器进行预置,计数器的时钟脉冲由秒脉冲电路提供。按键弹起后,计数器开始减法计数工作,并将时间显示在共阴极七段数码显示管DPY_7-SEG 上,当有人抢答时,停止计数并显示此时的倒计时时间;如果没有人抢答,且倒计时时间到时, 输出低电平到时序控制电路,控制报警电路报警,同时以后选手抢答无效。下面结合图4具体讲一下标准秒脉冲产生电路的原理。

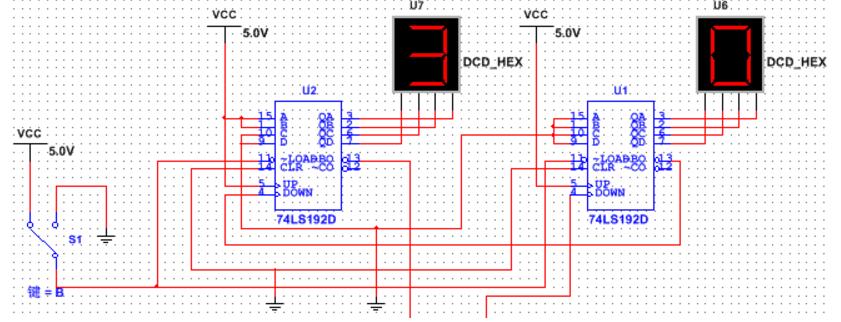

74ls192计数器应用电路图四:30进制计数器电路

本实验采用74LS192芯片作为计数器,74LS192是同步的加减计数器,其具有清除和置数的功能。本实验选择两片74LS192作为分别作为30的十位和个位。本实验中将作为十位的计数器输入端置为0011而将个位的输入端置为0000。将两片74LS192的置数端连出来与开关B相连,开关B控制置数端与高电平还是低电平,从而实现当30倒计时到00时,通过手动操作开关B而可以重新开始倒计时,计数器的电路连接如下图所示:

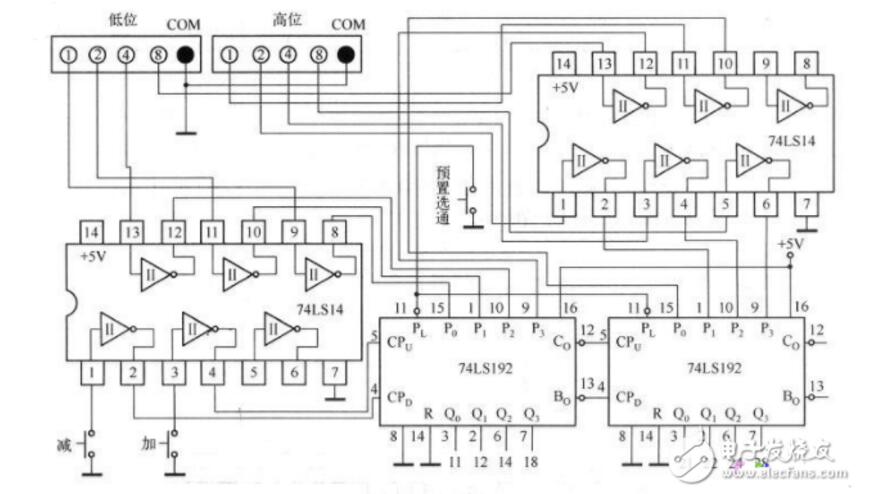

74ls192计数器应用电路图五:两位十进制计数器

下面以两个74LS192级联构成两位十进制计数器控制实现0.0~9.9V的切换为例。低位计数器输出Qo、Qi、Q2、Q3分别提供0.1V、0.2V、0.4V、0.8V的控制信号;高位计数器输出Qo.Qi、Q2、Q3分别提供1V、2V、4V、8V的控制信号。采用按键作为步进加、步进减的控制按钮;为了防止在按钮过程中出现振铃现象,在计数器加计数、减计数时钟脉冲端与加、减计数按钮之间接入施密特触发器74LS14,以消除振铃现象。

预置数选通端可以接拨码开关,以实现预置数的设置;用开关控制预置数选通端的选通状态,开关闭合时预置数选通端为低电平,选通端有效,预置数送到输出端;开关断开时预置数选通端为高电平,选通端无效,不能将预置数送到输出端。

由两个74LS192级联构成两位十进制计数器的电路如下图所示。

在图中,1V以下的计数器74LS192的时钟可以由“+”、“-”两键分别控制输出电压步进增减,1V以上的计数器74LS192的加、减计数时钟则由低位的进、借位输出提供。

如果需要3位以上的减计数和预置数,则可以在图中的基础上继续级联192、相应的拨码开关及相应的74LS14,直到满足要求为止。

74LS192的输出接驱动继电器激磁线圈的晶体管基极,如下图所示。

为了使晶体管与TTL电平匹配,需要在74LS输出与晶体管基极之间串联适当的电阻,如15~20kΩ的电阻,同时在晶体管基极与发射极之间并联lOkΩ的电阻,以确保在74LS192输出低电位时晶体管处于关断状态。

-

jf_99514853

04-22

0 回复 举报感谢分享 收起回复

jf_99514853

04-22

0 回复 举报感谢分享 收起回复

-

如何去实现基于74ls192芯片和与非门的进制加法计数器设计呢2021-11-02 0

-

74LS192中文资料pdf2008-03-18 6498

-

十进制可逆计数器74LS192引脚图管脚及功能表2011-05-19 121459

-

74LS161计数器及显示应用电路图2007-12-02 12386

-

74ls192和74ls160的区别有哪些2017-12-21 32285

-

74ls192工作原理详解_使用说明_内部逻辑图及应用电路2017-12-21 252418

-

利用74ls192的倒计时计数器2017-12-21 103615

-

基于74LS192的任意进制计数器的设计2017-12-21 95760

-

基于74ls192设计4/7进制计数器详解2018-01-31 56473

-

红绿灯控制电路图大全(555\74LS192\计数器74LS160)2018-05-07 146103

-

74ls163应用电路图大全(N进制计数器\分频电路\时钟脉冲)2018-05-08 60638

-

74ls161分频电路图大全(脉冲分频电路\同步加法计数器)2018-05-08 103515

-

74ls190应用电路图大全(五款74ls190不同进制计数器电路)2018-05-28 56415

-

74ls192的功能及原理2024-01-22 3104

-

74LS192/74LS193计数器数据手册2024-02-18 235

全部0条评论

快来发表一下你的评论吧 !