74ls107引脚图及功能表详解

芯片引脚图

描述

本文首先介绍了74ls107引脚图及引脚功能、74ls107功能表,其次介绍了74ls107极限值、推荐工作条件及逻辑图,最后介绍了74ls107静态特性和动态特性,具体的跟随小编一起来了解一下吧。

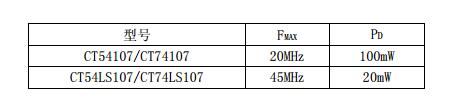

74ls107为带清除端的两组 J-K 触发器,其中 54/74107 是主从触发,54/74LS107 是下降沿触发,其主要电特性的典型值如下:

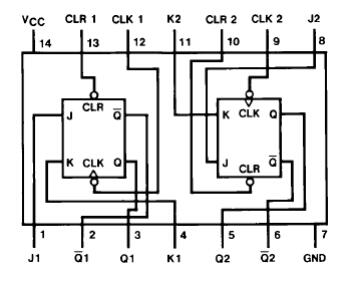

74ls107引脚图及引脚功能

引脚功能

CLK1、CLK2————时钟输入端

J1、J2、K1、K2————数据输入端

Q1、Q2、/Q1、/Q2————输出端

CLR1、CLR2————直接复位端(低电平有效)

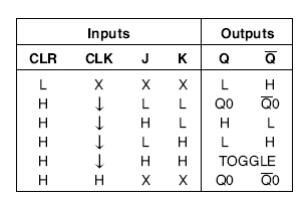

74ls107功能表

说明

H-高电平

L-低电平

X-任意

↓-高到低电平跳变

Q0-稳态输入建立前 Q 的电平

/Q0-稳态输入建立前/Q 的电平

74ls107极限值

电源电压------------------------------------------------7V

输入电压

54/74107-----------------------------------------5.5V

54/74LS107---------------------------------------7V

工作环境温度

54×××------------------------------ -55~125℃

74×××------------------------------------0~70℃

贮存温度-------------------------------------- -65~150℃

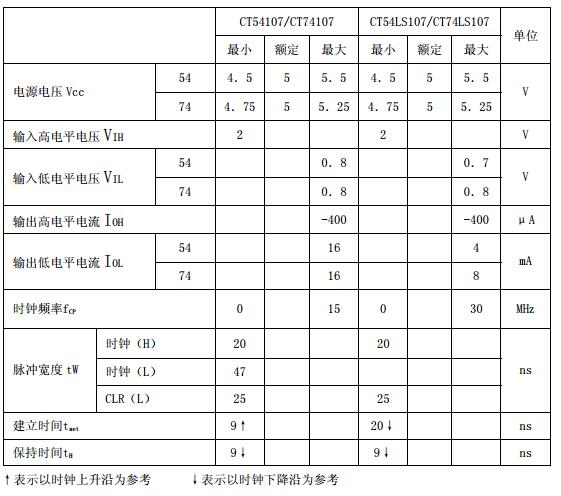

74ls107推荐工作条件

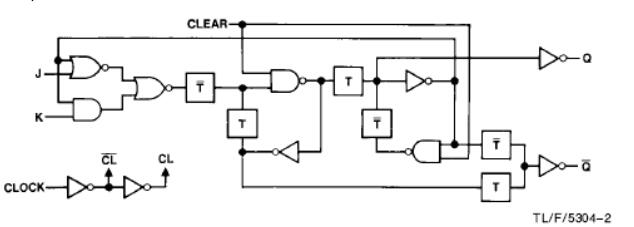

74ls107逻辑图

74ls107静态特性(TA 为工作环境温度范围)

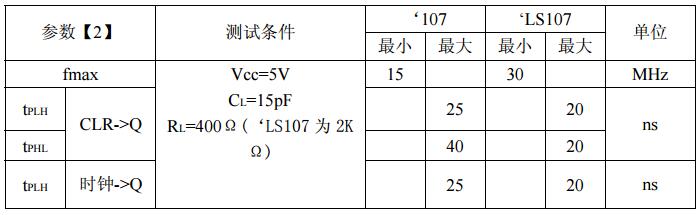

74ls107动态特性(TA=25℃)

fmax-最大时钟频率

tPLH-输出由低到高电平传输延迟时间

tPHL-输出由高到低电平传输延迟时间

推荐下载:《74ls107中文资料》

- 相关推荐

- 触发器

-

ST6378引脚功能表资料下载2021-03-25 0

-

stm32f407引脚功能表2021-08-09 0

-

74ls190引脚图管脚图及功能表2008-08-06 112398

-

74ls92引脚图及功能表2008-12-01 24079

-

74LS系列功能表2017-01-01 4969

-

74ls194引脚图及功能_74ls194功能表_74ls194应用电路2017-12-22 334611

-

74ls75引脚图及功能表介绍2018-04-28 61996

-

74ls121中文资料汇总(74ls121引脚图_功能表及应用电路)2018-05-02 37608

-

74ls137中文资料_74ls137引脚图及功能表_特性参数2018-05-04 11223

-

74ls174是D触发器吗?74ls174引脚图及功能表_逻辑图及特性2018-05-08 36557

-

74ls92中文资料汇总(74ls92引脚图及功能表_逻辑图及工作原理)2018-05-29 45845

-

计数器74ls93中文资料汇总(74ls93引脚图及功能表_逻辑图及工作原理)2018-05-29 41015

-

四位全加器74ls83引脚图及功能表_参数2018-05-31 98210

-

74ls32引脚图及功能表2021-07-08 35170

-

74ls163引脚图及功能表2021-07-08 80149

全部0条评论

快来发表一下你的评论吧 !