74ls112应用电路图大全(模七计数器/抢答器电路)

IC应用电路图

描述

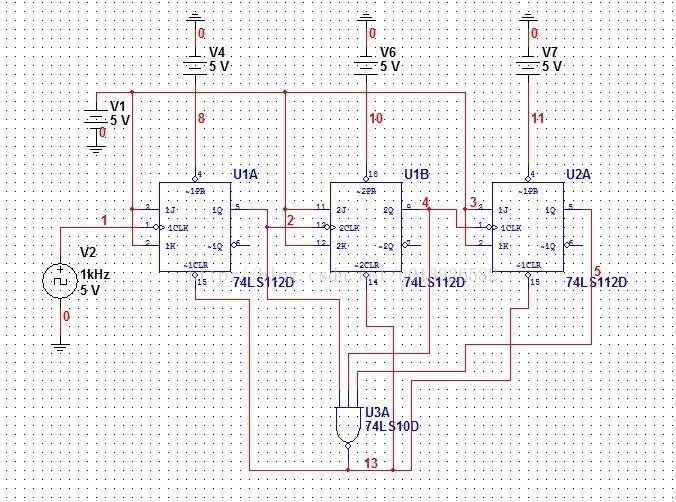

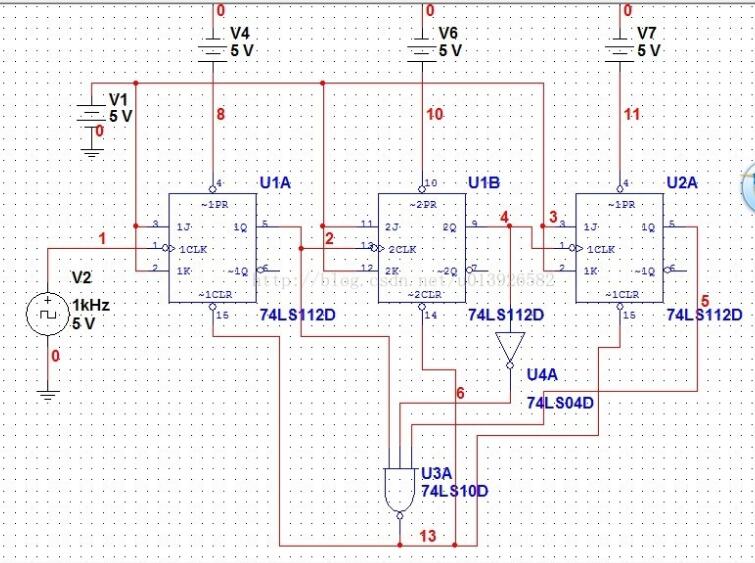

74ls112应用电路图一:

使用74LS112(或74LS74)构成一个十四分频器(模七计数器)。

用JK触发器,D触发器,做2的幂数的分频器是很简单的,只要学过数电基本上都会。2分频,4分频,8分频,16分频,堆叠触发器即可。但是稍有变化,要得到其他倍数的分频器,孩纸们都纳闷了。其实,触发器堆叠起来组成分频器有个特点,把靠近初始信号源的触发器视作低位,远离时钟源的末尾信号源视作高位,看成一个二进制数。

例如是8分频器,有3个JK触发器。3个触发器的Q输出端排列成的数字随着信号源的上升沿(下降沿)不断产生,这个二进制数是:(末端)000(前端),001,010,011,100,101,110,111,回到000是一个八进制计数器。我现在要组成十四分频,只要得到了七分频,再二分频就可以了。因此,问题归结为得到一个七进制的计数器。七进制的本质是什么呢?当这个三位二进制数达到110时,再进一位不出现111,而是自动归零。废话少说,如何实现?只要把三个分频器的输出端,与非后,送入三个触发器的CLR端,清空三个触发器的Q存储端,就达到了这样的效果。这就是一个模七计数器。如下图所示:

图一 模七计数器

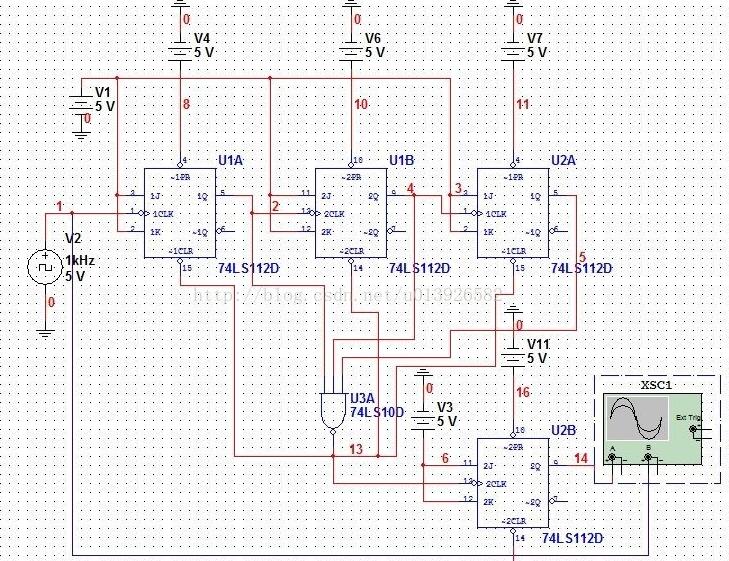

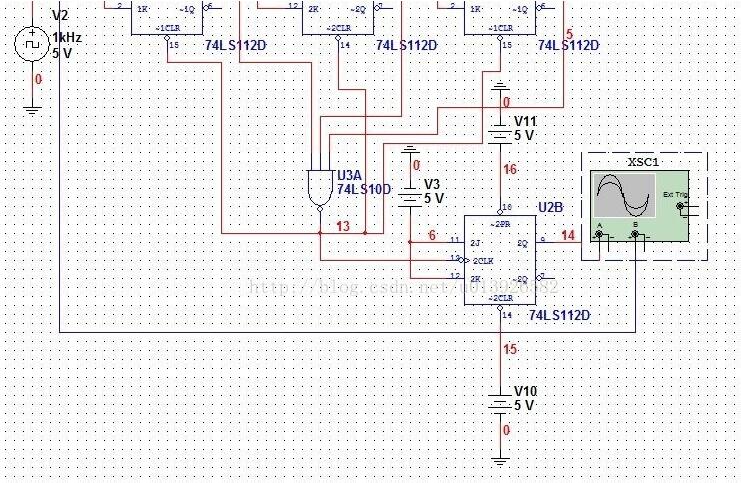

基于这个模七计数器(七分频器),再加上一个二分频,就得到我们想要的十四分频器啦!如下图所示:

十四分频器2

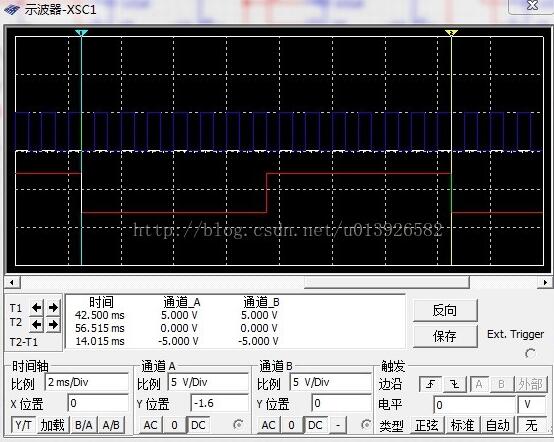

图四 输出端信号示波器(我的初始信号是1kHz,周期1ms,结果T2-T1为14ms)

以此类推,假如我要产生十分频器该如何设计电路呢?

很简单,只要设计出模五计数器即可,而5的二进制数是101。在中间的一Q输出加个反相器,输入给三与非门,再将与非门输出端输出给三个JK触发器的CLR端。如下图四所示:

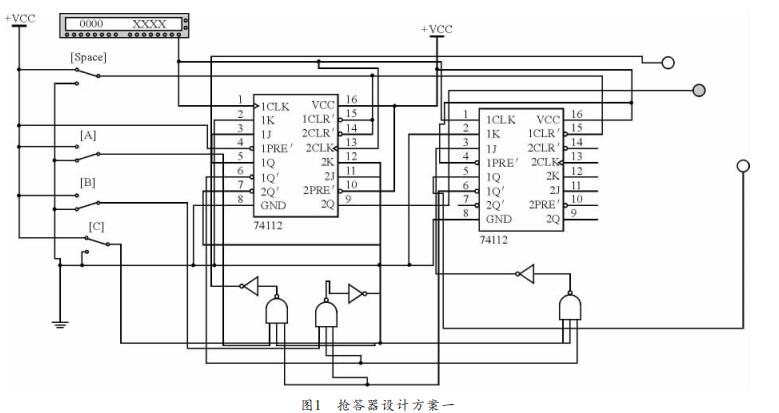

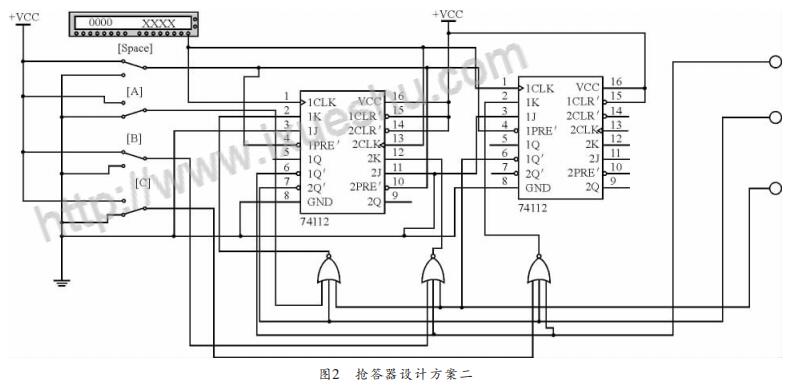

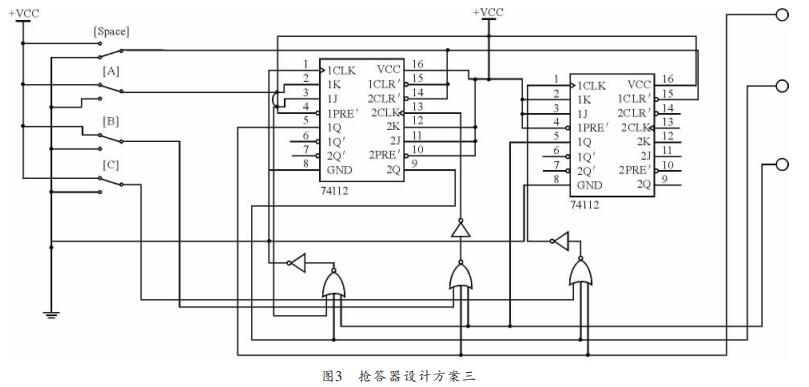

74ls112应用电路图二:

根据JK触发器在每个时钟脉冲作用时间内,其状态只变化一次,而且不同引脚都可以使触发器状态发生改变的特性,给出了用JK触发器来设计抢答器的设计方法及仿真,同时给出了用74LS112JK触发器设计抢答器的最优设计方法及思路。本文以74LS112触发器设计三人抢答器为例,给出了其设计方法。

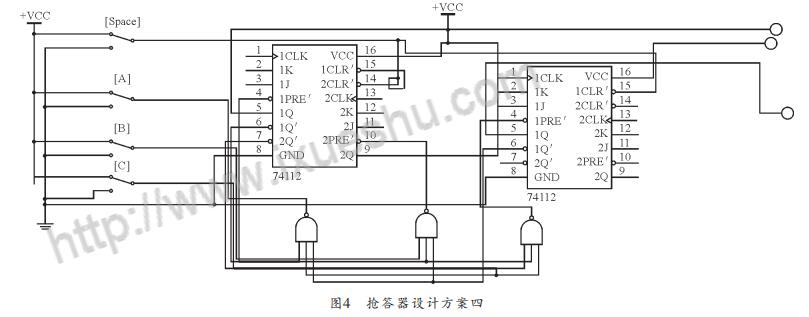

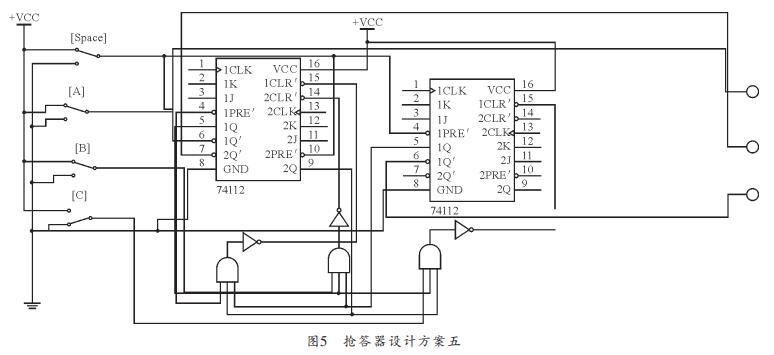

抢答器设计具有多种方案, 下面给出的几种方案的设计电路:

-

数字抢答器设计2009-03-20 0

-

8路抢答器电子设计2013-08-18 0

-

74LS161计数器及显示应用电路图2007-12-02 12378

-

一文看懂74LS112和74LS76的区别2018-04-28 72750

-

74ls138应用电路图大全(五款74ls138全加器电路/抢答器电路/三人表决器电路)2018-05-04 99575

-

74ls148应用电路图大全(优先编码器\抢答器)2018-05-07 37952

-

74LS171四路抢答器电路设计详情2018-05-08 24221

-

74ls163应用电路图大全(N进制计数器\分频电路\时钟脉冲)2018-05-08 60615

-

74ls161分频电路图大全(脉冲分频电路\同步加法计数器)2018-05-08 103497

-

74ls192计数器应用电路图大全(五款电子骰子/计时/定时电路)2018-05-28 125998

-

锁存器74ls373应用电路图大全(四款抢答器/单片机接口/信号发生器电路)2018-05-28 20885

-

74ls190应用电路图大全(五款74ls190不同进制计数器电路)2018-05-28 56389

-

74ls112引脚图及功能详解 74ls112的功能及原理2018-05-29 285741

-

74ls112引脚图及功能表2021-06-29 100612

全部0条评论

快来发表一下你的评论吧 !