FPGA学习系列:7. 串并转换

描述

设计背景:

Verilog语法中很多情况都用到了串并转化的思想,旨在与提升运算和芯片运行的速度,串行转并行已经成为设计中不可缺少的一种思维。

设计原理:

本次的设计主设计一个8位的串并转化,意思就是当输入8个数据的时候,我们把这8个串行数据转化为8位的并行数据然后输出出来。也就是需要一个8位的寄存器,来一个数据存到对应的位上,然后输出出来就完成了本次设计。

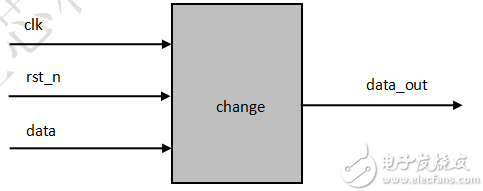

设计架构图:

设计代码:

设计模块

0 module study(clk, rst_n, data, data_out); //端口列表

1

2 input clk, rst_n; //时钟,复位输入

3 input data; //输入数据

4

5 output reg [7:0] data_out;

6

7 reg [3:0] count;

8 reg [7:0] temp;

9

10 always @ (posedge clk) //时序逻辑

11 if(!rst_n)

12 begin

13 data_out <= 0;

14 temp <= 0;

15 count <= 0;

16 end

17 else if(count < 8) //计数表示只接8个数据

18 begin

19 temp <= {temp[6:0],data}; //移位寄存器

20 count <= count +1'b1;

21 end

22 else

23 begin

24 data_out <= temp; //接到后输出

25 end

26

27 endmodule

测试模块

0 `timescale 1ns / 1ps //时标

1

2 module tb();

3

4 reg clk, rst_n;

5 reg data;

6

7 wire [7:0] data_out;

8

9 study study_dut( //设计例化

10 .clk(clk),

11 .rst_n(rst_n),

12 .data(data),

13 .data_out(data_out)

14 );

15

16 initial begin

17 clk = 1;

18 rst_n = 0; //复位

19 data = 0;

20 #200 rst_n = 1; //不复位

21 data = 1; //模拟数据输入

22 #20 data = 0;

23 #20 data = 1;

24 #20 data = 0;

25

26 #20 data = 0;

27 #20 data = 1;

28 #20 data = 0;

29 #20 data = 1;

30

31 #200 $stop;

32 end

33

34 always #10 clk =~clk; //模拟晶振时钟

35

36 endmodule

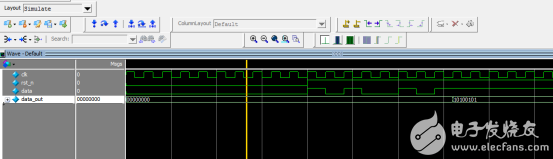

仿真图:

在测试中模拟数据输入时1010 0101,然后输出是一个并行数据,那么通过看仿真时序,清楚的看到输出是8位的并行数据,本次设计正确.

同样大家可以自己推理设计出并转串的逻辑电路来。

-

FPGA设计思想与技巧之串并转换和流水线操作2012-02-10 0

-

串并转换74hc1642013-10-12 0

-

求串并转换74hc164应用实例2013-10-14 0

-

用VERILOG编写SDI的均衡,恢复,解码(编码),串并转换代码2014-05-01 0

-

1to8串并转换2015-03-09 0

-

请问用labview怎样实现信源的串并转换?2015-06-18 0

-

FPGA串并转换实现问题2015-07-08 0

-

简单的串并转换怎样实现,不用移位寄存器。2015-12-14 0

-

求问,简单的串并转换怎样实现,不用移位寄存器。2015-12-14 0

-

至芯昭哥带你学FPGA之FPGA_100天之旅_串并转化2017-08-10 0

-

IO扩展(并转串)学习2021-12-06 0

-

FPGA串/并转换的思想相关资料推荐2022-02-23 0

-

基于FPGA的多路高速串并转换器设计2010-09-22 807

-

并串转换和串并转换2016-04-27 2339

-

(18)FPGA串/并转换的思想2021-12-29 252

全部0条评论

快来发表一下你的评论吧 !