展平式设计是集成电路设计中最基本的一种方法

描述

所有芯片的设计跟普通的产品一样,需有一个标准规范化的流程(flow)。然后工程师们按照流程,运行和调试参数来得到一个合格的结果。

随着EDA软件的不断发展,新的技术不断涌现,flow的选择性也呈现出多元化的趋势。所以了解新知识,新技术对于我们来说,是相当有必要的。

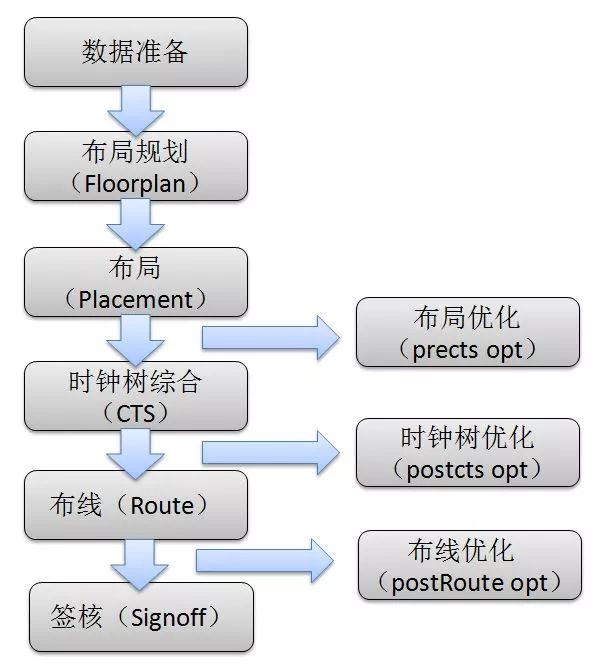

从设计的大方向上讲,flow分为传统的展平式设计(flat flow)和层次化设计(hierarchical flow)。展平式设计是集成电路设计中最基本的一种方法,芯片在全局范围内进行优化,通过布局绕线实现物理设计,提取RC参数进行时序分析,最后产生GDSII文档完成全部过程。简单的可以参考如下flat flow示意图:

展平式设计通常能取得更好的时序结果,但是却要花费极长的设计周期。随着电子技术的极速发展,单个芯片上的逻辑单元已经从几万们增加到几千万门,甚至几亿门。这对EDA工具,工程师,甚至计算机硬件都是一个极大的挑战。这时候就产生了层次化设计方案(hierarchical flow,简称Hier flow)。

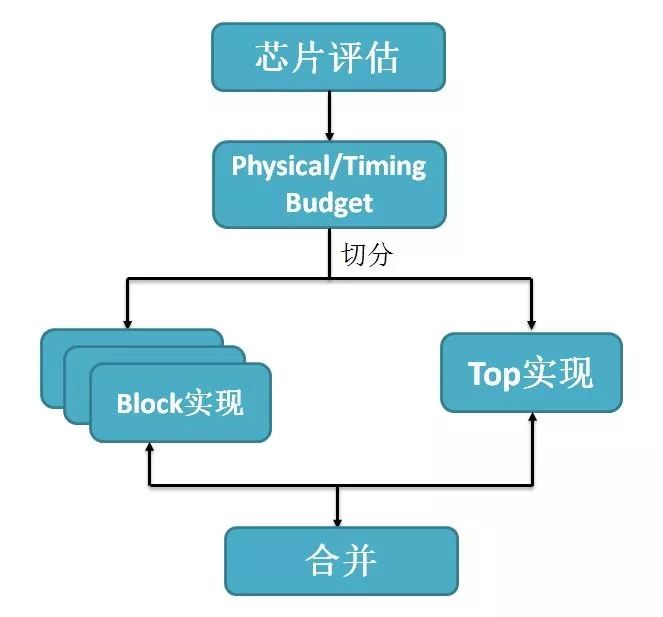

层次化设计是指对一个普通设计,在逻辑上定义出层次化器件(hinst),在物理上给予层次化器件一个物理约束(physical constraint),然后将具有物理约束的层次化器件定义为一个划分(partition),再将各个划分切出整个设计,剩下的部分保存为顶层设计(top),而各个划分则单独保存,对于顶层而言,切出去的划分视为黑盒(black box),而对于单个划分而言,在做分块实现(blockimplementation)的时候则视为片级设计(chip level design)。在完成分块实现以及顶层实现(top implementation)之后,最后将各个划分合并(assemble)到一起,完成全芯片(full chip)的签收(sign off)。简单的示意图如下所示:

层次化设计的方案的最大优点是它将很大的设计化成多个小设计,如果有时序问题可能存在于个别模块,再去重点解决,则复杂性变小,而且是局部的。同时,每个工程师分担的工作量也变小,完成设计的周期会缩短,从而加快了设计收敛。

当然,层次化设计也有许多不可避免的缺陷,最突出就是来源于时序预估时产生的误差。这种误差往往使得做划分的物理实现时,时序难以收敛。或者尽管划分满足时序收敛条件,在全芯片合并后,会发现一些时序路径又会变得极差无比。在手工ECO无效时,这种情况可能需要重做时序预估和划分的物理实现,最坏可能导致重新调整布图规划的风险。为了解决这些问题,传统的层次化设计方法也提出了许多更为先进的设计理念来提高时序精度,这些方法应用于层次化设计中的各个步骤中。从时序收敛的角度,展平化设计要比层次化设计精准很多。所以当设计的规模没有达到无法采用展平的设计方法完成时,设计者会偏向采用展平的设计方法来实施。

-

一种有效的集成电路块拆卸方法2010-03-30 0

-

集成电路应用电路识图方法2013-09-05 0

-

一个搞模拟集成电路设计的菜鸟之谈2013-10-10 0

-

电子元器件基础:集成电路应用电路识图方法2015-08-20 0

-

集成电路应用电路识图方法分享2018-07-13 0

-

集成电路应用电路图的功能和识图方法2018-08-28 0

-

一种通用的集成电路RF噪声抑制能力测量技术介绍2019-07-04 0

-

电路设计静电保护的几种方法?2021-03-17 0

-

介绍一种嵌入式系统仿真方法2021-11-08 0

-

一种全定制集成电路设计电压降分析方法2010-08-03 746

-

拆卸集成电路的几种方法2009-12-03 643

-

集成电路设计方法概论2011-05-23 549

-

集成电路设计导论2011-08-28 1234

-

介绍一种集成电路设计自动化的方法2022-08-22 923

全部0条评论

快来发表一下你的评论吧 !