PCB布线设计原则及对布线设计的工艺要求

描述

(一) 布线设计原则

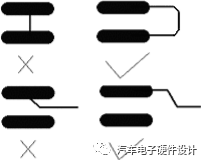

1.线应避免锐角、直角。采用45°走线。

2.相邻层信号线为正交方向。

3.高频信号尽可能短。

4. 输入、输出信号尽量避免相邻平行走线,最好在线间加地线,以防反馈耦合。

5.双面板电源线、地线的走向最好与数据流向一致,以增强抗噪声能力。

6. 数字地、模拟地要分开,对低频电路,地应尽量采用单点并联接地;高频电路宜采用多点串联接地。对于数字电路,地线应闭合成环路,以提高抗噪声能力。

7. 对于时钟线和高频信号线要根据其特性阻抗要求考虑线宽,做到阻抗匹配。

8. 整块线路板布线、打孔要均匀,避免出现明显的疏密不均的情况。当印制板的外层信号有大片空白区域时,应加辅助线使板面金属线分布基本平衡。

(二) 对布线设计的工艺要求

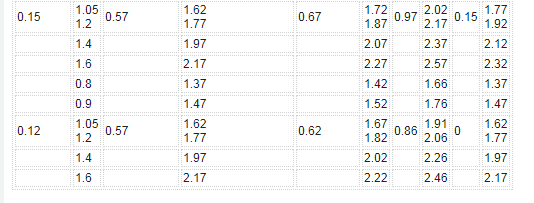

1.通常我们布线时最常用的走线宽度、过孔尺寸:

注意:BGA 封装元件下方的过孔,根据加工工艺的要求,需要在其正、反两面用阻焊层覆盖。

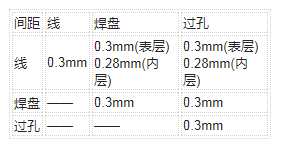

1)当走线宽度为 0.3mm 时

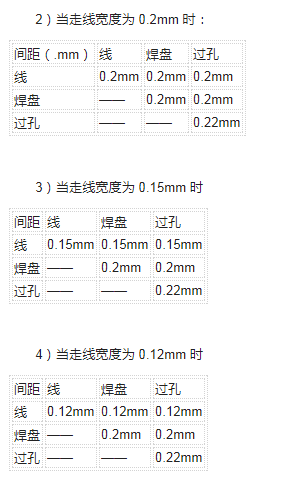

值得注意的是,BGA 下方的焊盘和焊盘间过孔焊盘的间距也为线宽。且由于工艺方面的难度,不推荐使用 0.12mm 的线宽。

5)当线宽小于等于 0.12mm 时,过孔焊盘需要加泪滴,表中的 T 即代表需要加泪滴。当板子的尺寸大于 600mm 时,过孔的焊盘宽度需要增大 0.1mm。表中单位:mm

对于非孔化孔,阻焊窗直径(the solder resist window)应该比孔的直径大0.50mm。而表层隔离区宽度也由孔的尺寸决定,当孔的直径小于等于 3.3mm 时,其范围是 “孔径+2.0” ;当孔的直径大于 3.3mm 时,其范围是孔径的1.6 倍。内层的隔离区范围是 “孔径+2.0mm”

2.具体的布线原则:

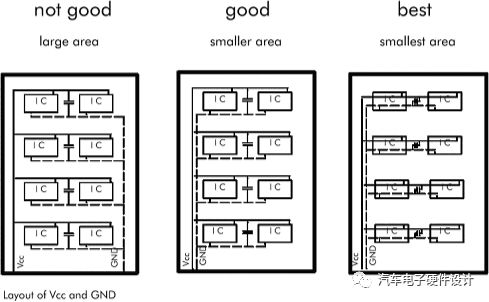

1)电源和地的布线

尽量给出单独的电源层和底层;即使要在表层拉线,电源线和地线也要尽量的短且要足够的粗。

对于多层板,一般都有电源层和地层。需要注意的只是模拟部分和数字部分的地和电源即使电压相同也要分割开来。

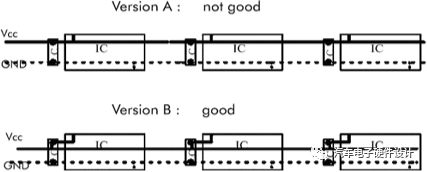

对于单双层板电源线应尽量粗而短。电源线和地线的宽度要求可以根据 1mm的线宽最大对应 1A 的电流来计算,电源和地构成的环路尽量小。

如下图:

为了防止电源线较长时,电源线上的耦合杂讯直接进入负载器件,应在进入每个器件之前,先对电源去藕。且为了防止它们彼此间的相互干扰,对每个负载的电源独立去藕,并做到先滤波再进入负载。

如下图:

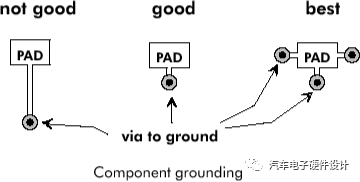

在布线中应保持接地良好。如下图:

2.特殊信号线布线

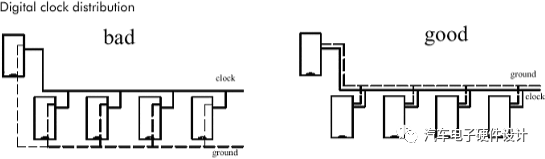

A.时钟的布线:

时钟线作为对 EMC 影响最大的因素之一。在时钟线应少打过孔,尽量避免和 其它信号线并行走线,且应远离一般信号线,避免对信号线的干扰。

同时应避开板上的电源部分,以防止电源和时钟互相干扰。

当一块电路板上用到多个不同频率的时钟时,两根不同频率的时钟线不可并行 走线。

时钟线还应尽量避免靠近输出接口,防止高频时钟耦合到输出的 cable 线上并 沿线发射出去。

如果板上有专门的时钟发生芯片,其下方不可走线,应在其下方铺铜,必要时 还可以对其专门割地。

对于很多芯片都有参考的晶体振荡器,这些晶振下方也不应走线,要铺铜隔离。 同时可将晶振外壳接地

B.成对差分信号线走线

成对出现的差分信号线,一般平行走线,尽量少打过孔,必须打孔时,应两线 一同打孔,以做到阻抗匹配。

C.相同属性的一组总线,应尽量并排走线,做到尽量等长。

D.一些基本的走线原则。

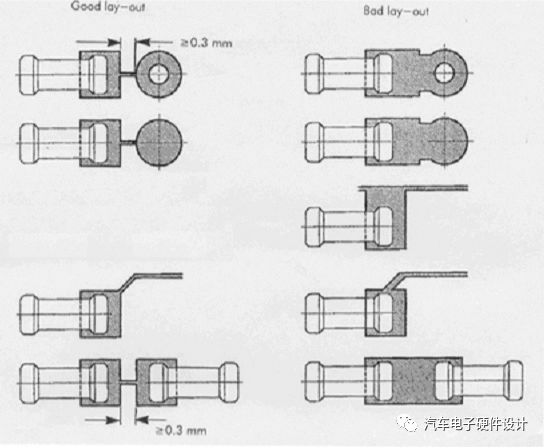

考虑到散热,避免连焊等因素,尽量采用下图所示的 Good lay-out,避免 Bad lay-out。

两焊点间距很小(如贴片器件相邻的焊盘)时, 焊点间不得直接相连。

从贴片焊盘引出的过孔尽量离焊盘远些。

3)敷铜的添加

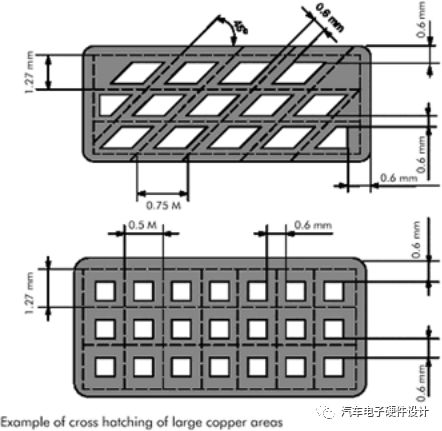

多层板内层敷铜,要用负片(Negative) 。外层敷铜如要完全添实,不应有 一丝空隙,最好用网格形式敷铜,其网格最小不得小于 0.6mm X 0.6mm, 建议使用 30mil X 30mil 的网格敷铜。如图

-

高速PCB布局/布线的原则2025-05-28 1902

-

pcb设计布局布线原则及规则2024-01-22 3205

-

pcb布线原则分享 PCB电源布线的技巧2023-03-14 12761

-

浅谈高速电路PCB的布线设计原则2022-11-15 2488

-

pcb布线 pcb布线的基本原则2021-07-21 27475

-

PCB布线工艺的要求有哪些2020-06-16 4660

-

PCB双层板的布线原则2019-05-30 2516

-

pcb自动布线设置_设置线间距与宽度设置_pcb布局布线技巧2018-01-31 37200

-

PCB板布局原则、布线技巧(图解)2016-05-17 2122

-

PCB板基础知识、布局原则、布线技巧、设计规则2016-05-11 1629

-

PCB设计布线2016-04-18 1003

-

PCB板布局原则、布线技巧2014-05-02 18976

-

PCB板布线原则2012-10-02 4573

-

PCB布线原则2008-07-23 2418

全部0条评论

快来发表一下你的评论吧 !