FPGA工程师的成长轨迹分析

电子说

描述

第一部分:FPGA工程师的成长

第一阶段:入门 -> 熟练克服心理恐惧– 代码这么写可以编译通过– 下载程序不会烧毁电路板建立思维定势– “事非经过不知易”学会了便是“自古华山一条路”

没用过便是“乱花渐欲迷人眼

第二阶段:提高 -> 精通EDA工具——从感性认识到理性认识– 站在EDA工具的角度理解FPGA开发流程EDA工具各个流程的意义,各个阶段的输入输出EDA工具输出的报告:Infor和warningHDL语言——积累设计模式– 跨时钟域处理电路– 有限状态机电路– 特定领域的数据通路电路– 片上总线FPGA芯片——从逻辑特性到物理特性

– 搞定时序分析和约束– 看懂RTL视图和Technology视图第三阶段:从业 -> 专业从产品需求出发认识你的芯片– 芯片之内深刻理解FPGA底层结构与应用场合的对应关系– 芯片之外FPGA外围支持电路以及高速接口FPGA与软件接口的设计和调试做出你的产品– 公司业务– 项目流程– 领域知识

个人的成长+成功的项目给刚刚从业的FPGA工程师的几点忠告– 珍视你的第一份工作从工作中学习,在工作中成长记工作日志,写博客– FPGA工程师学点软件,学点“不可综合语句”数据的分析和可视化工具之间的“胶水”– 使用Linux OS 脚本

免费工具开源精神

第二部分:FPGA开发中的敏捷实践FPGA开发本质上是敏捷的– 相对于芯片开发:灵活 + 快速 = 敏捷

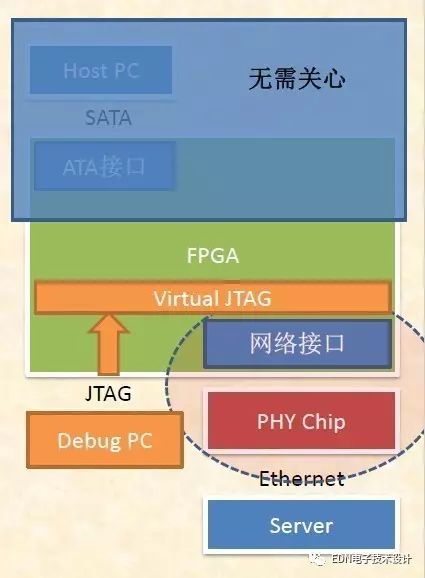

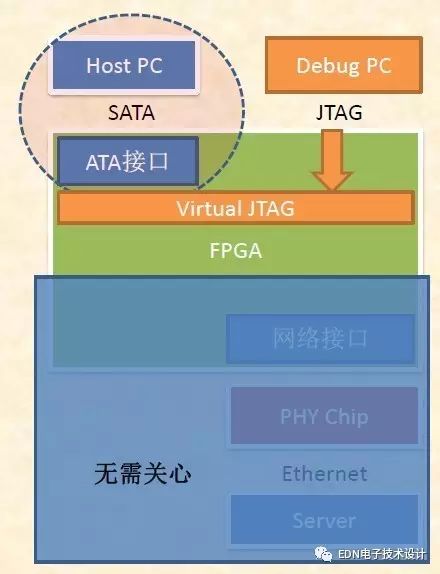

可以随时更新– 更短的迭代周期可以上板验证 – 更快的反馈速度敏捷开发的思想需要结合FPGA的自身特点– 相对于软件开发:上板调试代价更高 – 仿真验证的必要性距离真实世界更近 – 开发验证、调试工具的必要性» 验证、调试工具不是最终产品的一部分» 开发工具、积累工具,合理重用刻意地模仿芯片或者软件开发都是不可取的案例分享案例一:用Virtual JTAG加速上板验证

– 问题1:缺少外部芯片的仿真模型。– 解决1:用VJ虚拟出一个“串口控制台”,通过接口逻辑层,向外部芯片发送“写”和“读”命令。验证接口逻辑层,积累操作外部芯片的脚本。 通过这一接口,把最终产品中需要用状态机来实现的控制电路,暂时替换为可以用PC机软件来实现的脚本;把FPGA上的硬件调试转化为了PC端软件调试,加速了调试过程。– 敏捷思想: 把项目中的风险,在早期的迭代中加以解决。

– 问题2:外部设备行为复杂,测试向量覆盖率不够、仿真速度慢。– 解决2:用VJ设计一个真实行为捕获模块,丰富测试向量。用VJ虚拟未实现的关键逻辑模块,上板测试调试。– 敏捷思想:反思回顾,发现开发瓶颈,持续改进方法、工具。提早集成、提早测试。案例二:FPGA开发中引入回归测试和持续构建

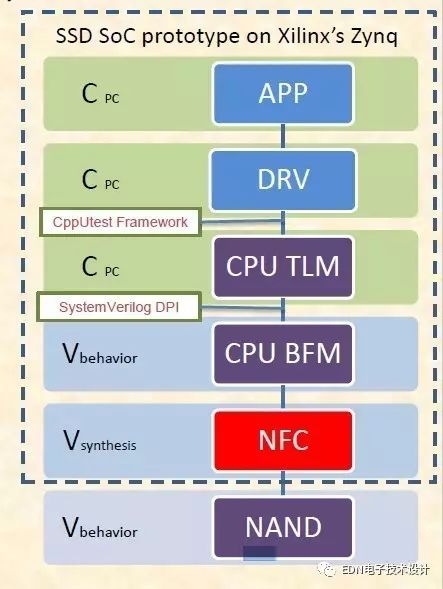

– 问题1:软件的驱动层(C)和FPGA的接口层(V)需要测试和调试FPGA需要回归测试来保证持续开发的质量– 解决1:用SystemVerilog DPI连接C和Verilog用CppUtest测试框架搭建FPGA回归测试环境– 敏捷思想:回归测试

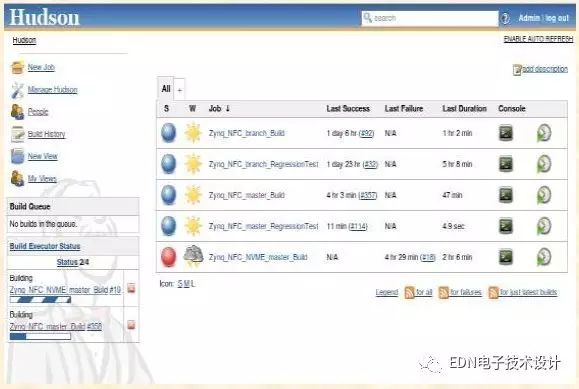

– 问题2:多人协作开发中代码的质量保证FPGA需要自动构建来实现及时发布– 解决2:用Tcl脚本实现项目编译、仿真的自动化用Hudson CI来实现多个仿真、编译工程的自动构建和健康度报告– 敏捷思想:每日构建

-

#FPGA 本科生也能成为FPGA研发工程师明德扬助教小易老师 2023-09-23

-

#人工智能 #FPGA 怎么成为一个合格的FPGA工程师?明德扬助教小易老师 2023-12-18

-

《Altera FPGA工程师成长手册》暨-【论坛送书活动预告】2012-05-08 0

-

清华大学Altera-FPGA工程师成长手册2012-09-13 0

-

诚招FPGA、硬件、模拟电路工程师2013-08-09 0

-

诚聘FPGA、硬件与模拟电路工程师2013-08-09 0

-

设计教训如何成就称职的FPGA资深工程师?2013-08-20 0

-

招聘:软件工程师(数字信号处理方向-FPGA)、硬件工程师2015-04-25 0

-

FPGA工程师兼职2015-07-02 0

-

诚聘FPGA软件工程师2017-02-17 0

-

诚招“FPGA工程师、嵌入式系统开发工程师”2018-01-13 0

-

求FPGA开发工程师、硬件开发工程师各一名2019-10-22 0

-

嵌入式Linux开发工程师的成长过程2021-11-05 0

-

嵌入式软件开发工程师与FPGA开发工程师的区别是什么?2021-11-22 0

-

FPGA工程师需要具备哪些技能?2023-11-09 0

全部0条评论

快来发表一下你的评论吧 !