怎样在先进工艺节点下实现无源器件的精确建模及仿真?

描述

时间&地点

日期:2018年6月25-27日

地点:旧金山, 美国

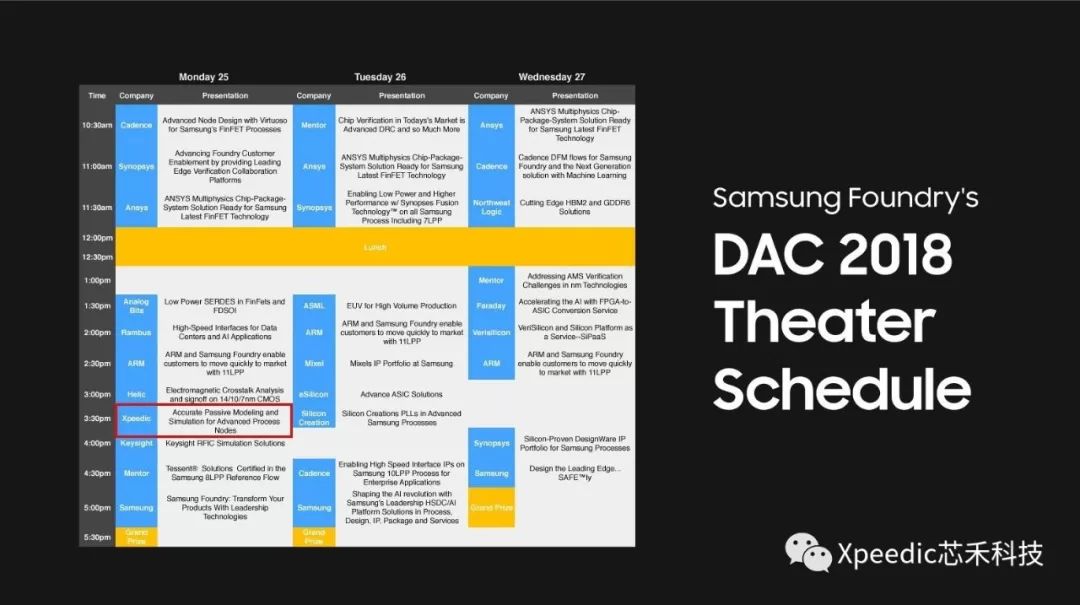

芯禾科技作为三星半导体的重要合作伙伴之一,受邀将参加下周一在美国旧金山举行的DAC2018三星展区演示活动。CEO凌峰博士届时将发表题为“先进工艺节点下的无源器件建模及仿真”的技术演讲。

作为行业里普遍的观点,先进工艺节点下无源器件和互连结构的建模和仿真越来越成为半导体工程师的挑战。而要解决这些挑战,以下几个技术是最常被探讨的:

一个整合的设计环境,使电磁仿真工具能够无缝接入现有的设计平台中

在设计阶段中实现快速无源器件建模和合成

在签核sign-off 阶段实现精确验证,同时能把封装的影响考虑进来

在此次现场演讲中,芯禾科技将演示一套集成的IRIS设计流程,它能无缝接入到Cadence Virtuoso设计平台中,从而完全的解决半导体工程师遇到的以上热点问题。通过此流程,工程师不仅能在设计阶段使用芯禾科技的IRIS和iModeler工具快速和精确地完成无源器件仿真和合成,还能在签核阶段通过与Ansys公司的合作把HFSS集成进来实现精确验证以及芯片封装联合仿真。

除此之外,芯禾科技在DAC展会上也设有专属展位(展位号2041),并将带来多项现场演示,包括针对封装领域的IPD与SiP设计电磁仿真解决方案以及针对高速系统的信号完整性分析解决方案。

我们期待与您在现场交流讨论。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

无源器件怎么定义#电子元器件李皆宁讲电子 2021-12-21

-

此“源”非彼“源”——有源和无源器件的“源”2012-03-09 0

-

有源器件与无源器件的区别2014-10-17 0

-

Saber软件功率MOSFET自建模与仿真验证2017-04-12 0

-

工艺设计套件推进创新2018-10-26 0

-

集成无源器件的作用是什么?2019-07-31 0

-

业界领先的半导体器件SPICE建模平台介绍2020-07-01 0

-

概伦电子先进的建模软件平台MeQLab介绍2020-07-01 0

-

通信网络中射频无源器件的应用2020-08-20 0

-

Simulink建模与仿真的流程是怎样的?2021-06-22 0

-

在40-nm工艺节点实现世界上最先进的定制逻辑器件2010-02-04 1236

-

一种用于先进工艺节点中的无源器件建模和验证的IRIS-HFSS整合流程2018-11-20 3697

-

芯和的先进封装建模仿真平台Metis2021-12-17 2725

-

元器件建模与仿真挑战2023-09-21 2779

全部0条评论

快来发表一下你的评论吧 !