一招教你实现通用模拟输出设计

描述

在这一系列上两篇帖子中,我谈到了3线模拟输出的演进以及如何保护3线模拟输出。在这篇帖子中,我们将用一些解决几个特定应用问题的解决方案来完成3线制模拟输出的讨论。

工业应用领域的一个不断增长的趋势是让模拟输出模块提供单个端子块上的电压和电源输出。这样做为制造商节省了昂贵的接头和电缆连接费用。此外,他还增加了单模拟输出模块在几乎任何需要模拟输出的应用中的使用灵活性。

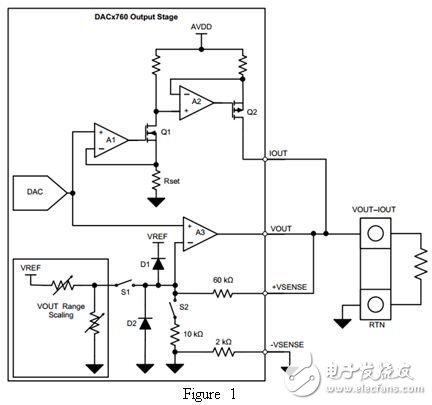

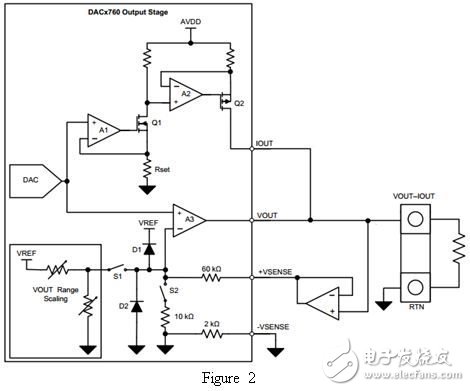

上方图1中的全集成方法使用DAC8760,其中VOUT和IOUT端子被直接互连并连接到输出端子。

当电压输出被启用而电流输出被禁用时,IOUT端子进入高阻抗状态。由于IOUT引脚处于高阻抗,输出电流的绝大部分将流入负载,从而使电压输出表现为数据表中的额定值。

然而,当电流输出被启用,而电压输出被禁用时,电压输出缓冲器 (A3) 暂停工作,而开关S1和S2打开。这使得输出电流在负载高端上产生的电压电势高于VREF之前按照数据表中的额定值执行。当这一情况发生时,二极管D1被正向偏置,并且开始导电,减弱负载中的电流,并生成针对电流输出的额外误差。

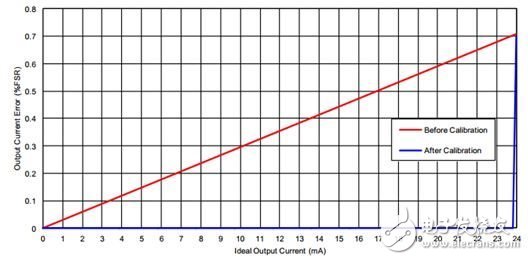

对这一问题的数字解决方案是将DAC8760电压输出设定为“间隔断电”模式,此模式将关闭S2,并防止D1导电。关闭这个开关会生成针对电流输出的增益误差,但是这个增益误差可使用内部校准寄存器消除掉。下方图表显示了这个数字解决方案的已校准和未经校准结果。

此数字解决方案在电流输出传递函数的绝大部分上消除了引入到电流输出的误差,但是这个纯数字校准技术有其局限性,就是会在满量程时导致端点误差。

另外一个模拟解决方案是在共用VOUT和IOUT连接与+VSENSE连接之间放置一个单位增益缓冲器。在这个情况下,当负载高端上的电压达到VREF或者更大时,DI仍将导电,但是缓冲器将拉出这个电流而不是IOUT,从而使得电流输出达到额定值。电压输出将受到缓冲器输入偏移电压的轻微影响,但是仍将保持良好性能。与这个模拟方法相关的更多信息,其中也包括测得的性能,请查看TIPD119。

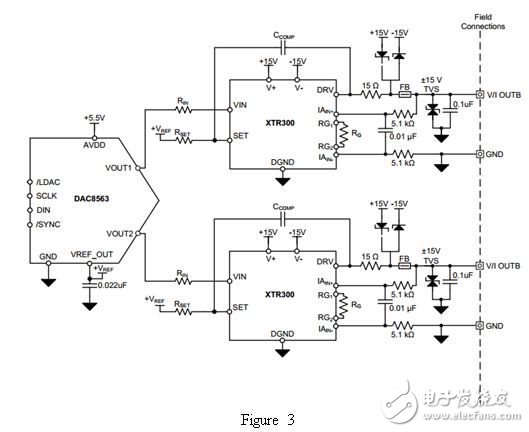

另外一个实现共用电压和电流输出的简单方法是一个使用XTR300和一个DAC的离散方法。在图3中显示了这一方法的两通道示例。根据数字输入重新配置了XTR300内部电路的电压或电流输出,从而实现共用电压和电流输出端子的本地支持。在TIPD155中讨论了这个设计的全部细节。

-

转载:每天学一招:设计Q&A2011-07-15 0

-

通用模拟输出的设计2018-09-12 0

-

【微信精选】5分钟教你轻松实现通用模拟输出设计2019-09-28 0

-

教你一招如何分辨PCB板层数2021-04-23 0

-

教你一招如何去实现傅立叶变换算法?2021-04-30 0

-

教你一招怎样去选择合适的CPLD2021-05-06 0

-

教你一招分分钟实现频谱仪带宽的正确设置2021-05-07 0

-

教你一招定时器中断该怎么办?2021-05-14 0

-

教你一招如何通过手机的芯片来判断手机的价格?2021-05-24 0

-

教你一招如何去选择射频滤波器?2021-05-28 0

-

教你一招RK31885.1蓝牙MAC怎样才能从模组中获取MAC地址2022-02-18 0

-

如何设计通用模拟输出2017-04-18 457

-

如何构建环路供电的模拟输出2022-01-28 1235

-

工业 DAC:3 线模拟输出的演进2022-11-04 193

-

模拟输出及架构概览2022-11-04 236

全部0条评论

快来发表一下你的评论吧 !