电压控制电路中几种FET的使用方法

电子说

描述

LIS公司生产各种FET(场效应晶体管),特别值得一提的是他们有各种匹配双器件产品,这种匹配器件封装有其独特优势。例如,如果您在设计一个双声道立体声音频产品,那么在同一个封装中包含两个或四个器件就可以使两个音频通道匹配更加紧密。

本文将探讨如何在电压控制电路中使用FET,分四部分连载,重点介绍几种FET的使用方法:

FET用作压控电阻;

FET用作电压控制放大器和有源混频器;

FET用作压控移相器来处理音乐;

FET用作压控带通滤波器。

我们还将探讨减少非线性或失真并自动偏置FET的方法。

FET电压控制电阻

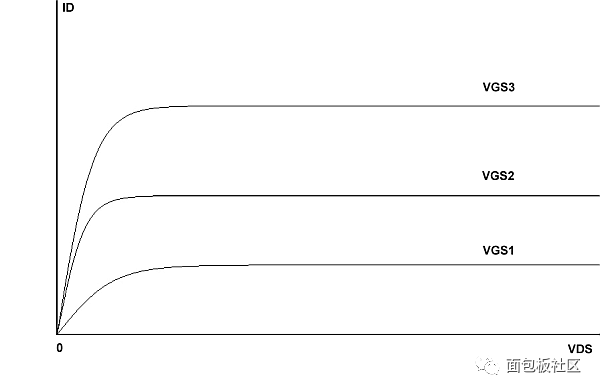

图1显示了一个N沟道FET的典型电流-电压关系。

图1:在不同的栅极至源极电压VGS1/VGS2/VGS3下,典型的N沟道FET的I/V曲线。

FET一般有两个区域:饱和区包括曲线的水平部分,这时FET用作电压控制电流源;另一个区域包括倾斜的“弯曲部分”,称为三极管或欧姆区,此时FET用作压控电阻。如果仔细观察,我们会注意到图1中的三极管区域显示了非负的漏源电压(VDS)。

注意:FET中的三极管或欧姆区有时称为线性区。FET作为压控电阻(VCR)工作在这个区域。理想情况下,VCR模式下的FET漏极和源极端子之间不存在DC电压。

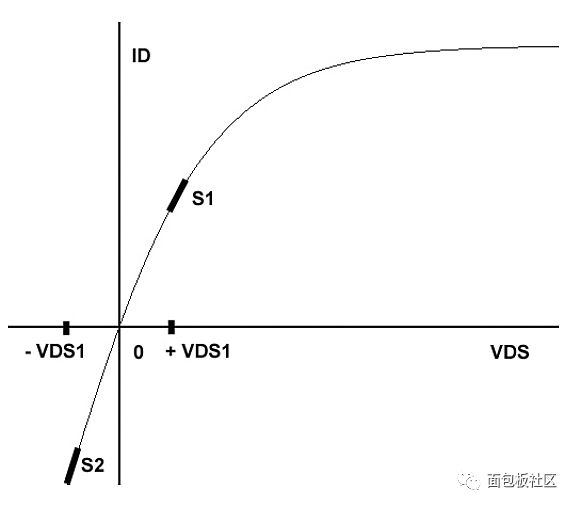

如果我们将针对特定栅-源电压的VDS电压范围扩大,使其略包含负电压,我们看到仍然存在电阻效应(图2)。

图2:FET的三极管区扩展到负VDS电压(- VDS1)仍然表现出电阻效应。

斜率定义为:

斜率=ΔID / ΔVDS= gds = 漏极和源极间的电导

漏极和源极之间的电阻是电导的倒数:

Rds = 1 / gds =ΔVDS/ΔID

我们看一下表示gds的两个斜率S1和S2,会发现它们大致相同。但是如果仔细看,就会看出它们实际上有一点不同,S2的斜率比S1的斜率更陡一些。斜率越陡,电导率越高,电阻越低。例如,S2或-VDS1的高斜率区域附近的电阻低于S1或+ VDS1附近的电阻。电阻从+VDS1逐渐变化为-VDS1会导致失真,幸好失真可以减到很小。

例如,当漏极和源极两端的小AC信号 < 500mV峰-峰值时,谐波失真可以保持在“合理的”低水平。如果漏极和源极之间的交流信号电压在 - 250mV与+250mV之间,谐波失真将会“很小”,通常 < 3%。

这时你也许会问,有没有FET只用作电压控制电阻的?答案是肯定的(比如VCR11)。事实上,任何其它FET(比如JFET和MOSFET)都可用作电压控制电阻。

基本的压控电阻(VCR)电路

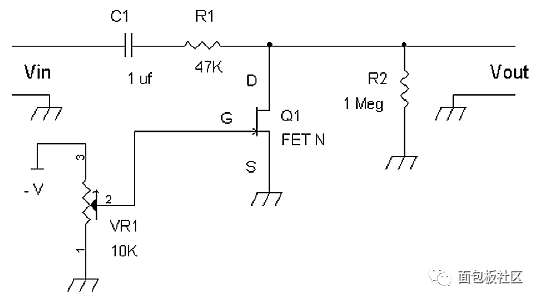

电压控制电阻最简单的一种用途是电子控制衰减器或“音量控制”。在图3、图4、图5和图6中,基本电路构成一个分压器。

在每一个电路中,FET(Q1/Q2/Q3/Q4)的漏极和源极端子提供电压控制电阻。当频率大于20Hz时,C1的阻抗可被视为AC短路。

图3:N沟道JFET衰减器电路。

在图3中,将Q1的栅极电压设置为0V或接地可实现最大衰减。R2将为Q1的漏极建立直流接地路径。如果用导线代替C1,并且输入信号源没有明显的DC偏置电压(即 < 10mV DC),同时输入信号源有一个直流接地路径,它就可以被忽略。

当Q1栅极的负电压导致Q1处于切断状态(即当栅极电压→Vp时的夹断电压)时,发生最小衰减(即“贯通”)。

衰减器的传递函数是:

Vout/Vin = [Rds || R2] / [R1 + ( Rds || R2 )]

请注意,Rds是给定栅源电压的漏源电阻。

如果Rds << R2,那么:

Vout/Vin = [ Rds] / [R1 + Rds ]

例如,如果Rds = 10kΩ,那么:

Vout/Vin = [10kΩ] / [47kΩ + 10kΩ] = 10kΩ/57kΩ = 10/57 = 0.1754

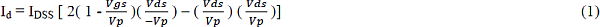

“耗尽型”N沟道JFET的漏极电流由Sedra和Smith的《微电子电路》给出:

其中,IDSS是Vgs = 0时的漏极电流。这一“最大”漏极电流在产品规格表中给出。

Vgs是N沟道器件的栅极到源极电压,是非正电压。

Vp 是夹断电压或切断电压。这是施加到栅极和源极以提供零漏极电流的电压。产品规格表中给出了N沟道JFET的夹断电压Vp ≤ 0。而且,当Vgs = Vp时,漏极到源极电阻是无限的,因为没有电流流入FET的漏极。

Vds是漏源电压。这可以是漏极和源极之间的交流电压,如图3、图4、图5和图6中的Vout。

对于欧姆、三极管或线性区的N沟道JFET,公式(1)至(5)仅在Vp≤Vgs≤ 0V时有效。

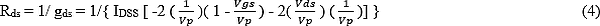

电导gds是通过求Id关于Vds的导数得到的。

电阻Rds是电导gds的倒数:

公式(4)显示Rds是基于固定参数IDSS、Vp和固定栅源电压Vgs的非线性电阻,与漏极和源极两端的(AC信号)电压Vds有关。

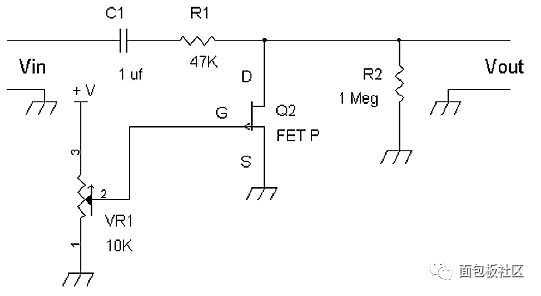

对漏极和源极两端小信号初步近似,当Vds→0时:

公式(5)则是固定参数IDSS、Vp和固定栅源电压Vgs的函数。电压控制的“线性”电阻可由Vgs电压设置。

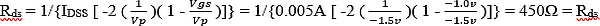

例如,如果Vp = -1.5V, Vgs = -1.0V, 且IDSS = 0.005A = 5 mA,则:

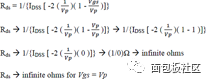

根据公式(5),如果我们设定Vgs = Vp,那么漏源电阻将无穷大(即开路):

对于N沟道JFET,若想通过设置Vgs = 0V来得到最小电阻值,会发生什么呢?

若Vgs = 0V,公式便简化为:

Rds = Vp/[-2IDSS]

例如,如果Vp = -1.5V,IDSS = 0.005A = 5mA, 且Vgs= 0V,那么:

Rds=-1.5v/[-2(0.005A)]=-1.5v/[-0.01A]=1.5v/0.01A=150Ω

Rds =150Ω

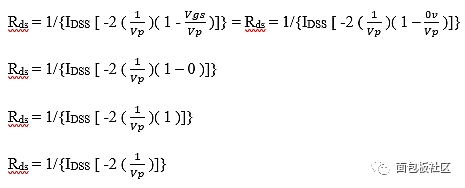

图4示出了一个P沟道FET衰减器电路。它的工作方式与图3相似,只是栅极的控制电压为正值,切断Q2获得最小衰减。同样,当栅极电压为零或接地时,得到最大衰减。

图4:P沟道JFET衰减器电路。

MOSFET用作电压控制电阻

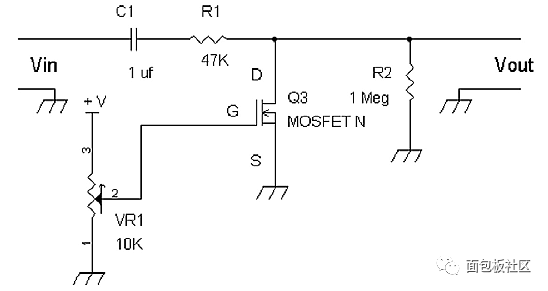

MOSFET也可被用作电压控制电阻,如图5所示。目前大多数MOSFET都是“增强型”,这意味着开通漏极电流以降低其Rds所需的栅极偏置电压为正电压。因此,如果栅极电压为0V,则MOSFET关断。

图5:N沟道MOSFET衰减器电路。

采用N沟道增强型器件Q3,在0V电压时,衰减器将输入信号以最小衰减传递至Vout。如果将VR1设置为大于阈值电压Vth的正电压,那么Q3的漏源电阻将开始下降。请注意,对于N沟道MOSFET,阈值电压Vth> 0V。

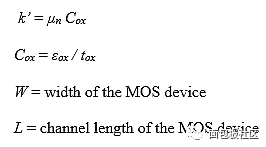

根据Gray和Meyer的《模拟集成电路的分析和设计》,N沟道MOSFET的漏极电流由公式(6)表征:

其中:

应该注意的是,大多数分立MOSFET产品规格表不会列出k’ = μnCox,Cox = εox/ tox,W 和L,而只是给出典型的IV曲线和阈值电压范围图。

N沟道JFET的公式(1)跟公式(6)非常相似。请注意,它们都包含“ - (Vds)(Vds)”项,这会导致非线性电阻。

重申一下,N沟道JFET的公式是:

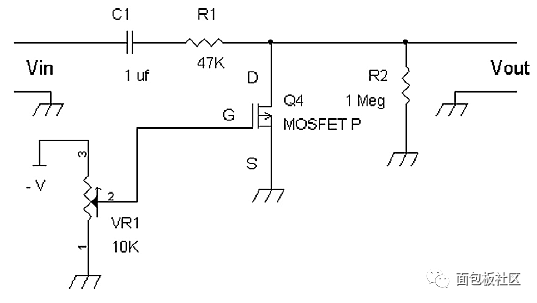

图6示出了一个P沟道MOSFET电压控制电阻电路。

图6:P沟道MOSFET衰减器电路。

对于P沟道增强模式器件Q4,在零电压时,衰减器将输入信号以最小衰减传递至Vout。如果VR1设置为比阈值电压Vth更负的电压,那么Q4的漏源电阻将开始下降。注意,P沟道MOSFET的阈值电压是负电压(Vth< 0V)。

一般来说,图5和图6所示的衰减器电路允许小信号有适当的谐波失真,Vout的峰峰值 电压 < 500mV。如果有失真,主要就是二次谐波失真。

平衡或推挽式VCR电路

我们可以利用图7所示的推挽电路进一步线性化或显著减少二次失真。特别是双配对FET(比如VCR11N、LSK489和LSK389等),可以消除偶次失真。

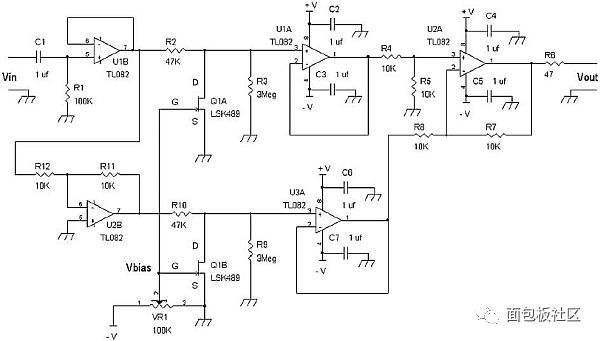

图7:一个N沟道平衡配置示例,使用双配对FET LSK489的Q1A和Q1B来降低失真。

推挽或平衡VCR衰减器电路可以消除或减少二次失真。在图7中,U1B缓冲输入信号Vin,并用Q1A(双FET封装的一半)驱动第一个电压控制衰减器电路。

Vbias是可变DC负电压,可以改变Q1A的漏源电阻,通过串联电阻R2提供电压控制分压电路。电压跟随放大器U1A缓冲Q1A漏极端子的电压控制衰减信号。

请注意,FET输入运算放大器(如TL082、TL062、LF353和AD712等)通常与高阻抗输入电阻器(如R3和R9)一起使用。

运算放大器电路R12、R11和U2B构成一个反相放大器,通过R10发送一个反相信号到第二个压控衰减器电路。Q1B的栅极有相同的Vbias信号,允许Q1A和Q1B的漏极和源极具有匹配的衰减特性。电压跟随器U3A通过Q1B的漏极对电压控制的衰减反相信号进行缓冲。由U2A、R4、R5、R7和R8组成的差分放大器从U1A和U3A中减掉输出,通过Vout消除二次失真。

至此,同相的Q1A和Q1B的漏极都有二次失真,二次失真意味着一个x2函数。

应注意的是,对负信号平方和对正信号平方得到的结果相同,即:

(- x)2 = (+ x)2

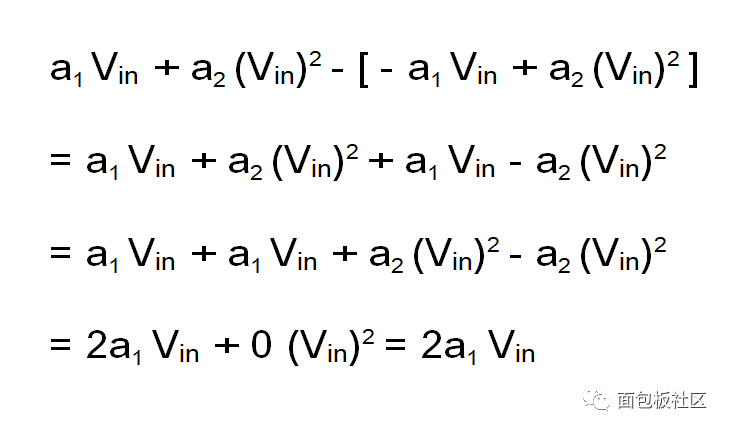

输出信号可表征如下:

a1 = 线性分压系数a2 = 二次失真系数

对于非反相信号:

U1A pin 1 = a1 Vin + a2 (Vin)2

对于反相信号:

U3A pin 1 = a1 (- Vin) + a2 (- Vin)2

注意:(Vin)2 = (- Vin)2

所以,对反相信号,我们有:

U3A pin 1 = - a1 Vin + a2 (Vin)2

差分放大器U2A从U1A引脚1和U3A引脚1中减去同相和反相信号后,得到:

注意,a2 (Vin)2 - a2 (Vin)2 = 0

因此,差分放大器电路U2A引脚1的输出 = 2a1 Vin,注意不存在二次失真项。这意味着我们得到一个放大了2倍的电压控制衰减信号,并且没有二次失真。

注意,图7显示了一个N沟道JFET的例子,但推挽或平衡操作的基本原理可以应用于图4、图5和图6中所示的P沟道JFET、N沟道MOSFET和P沟道MOSFET电压控制衰减器电路。

或者,我们可以向基本的电压控制电阻电路施加反馈来消除二次失真。当我们应用这个反馈时,输出信号会对称地失真,这是由奇次失真引起的。

-

控制电机的几种控制电路原理图2017-01-20 0

-

看电气控制电路图的方法2020-11-01 0

-

看电气控制电路图的方法 2020-11-01 0

-

电脑控制电路的检测方法2021-09-08 0

-

介绍几种常见的运用PLC编程Y-△减压起动控制电路的方法2021-09-30 0

-

常见主电路及控制电路故障处理方法2021-11-16 0

-

晶体三极管的应用晶体三极管的应用之几种传感控制电路的设计2009-11-12 542

-

电压比较器与控制电路2009-03-09 2333

-

极限电压控制电路图2009-06-20 500

-

移动的电压控制电路图2009-06-23 466

-

一种再生制动控制电路的设计2009-07-15 1123

-

J-FET开关电路工作原理2010-05-24 2938

-

介绍几种常用的PLC控制电路2022-08-17 6667

全部0条评论

快来发表一下你的评论吧 !