如何判断是否需要使用分立式晶振和振荡器呢?

描述

你在解决系统计时问题时,是不是需要使用分立式晶振和振荡器呢?对于大多数硬件设计师来说,这看起来的确是一个显而易见的方法,又有谁会到互联网上费时费力地搜寻那些包括时钟发生器IC和缓冲器/分布器件的经优化时钟树解决方案呢。虽然节省时间,但是这个使用分立式晶振和振荡器的方法经常会导致物料清单 (BOM) 成本的增加,并且会降低整个系统的性能。WEBENCH® Clock Architect(时钟架构师)是业内首款时钟和定时工具;这个工具建议用户使用一个包含TI广泛计时产品库中器件的系统时钟树解决方案。这个已获专利的多部分推荐算法—这款工具的精髓所在—为那些寻找高性能、灵活计时解决方案的设计师们提供快速解决方案,以及顺畅的使用体验。

除了推荐经优化的时钟树解决方案,这款工具特有先进锁相环 (PLL) 滤波器设计功能和相位噪声仿真功能,从而使你能够仿真并优化时钟树设计,以满足系统的需求。我们来一起看一看最近升级后的某些新特性。

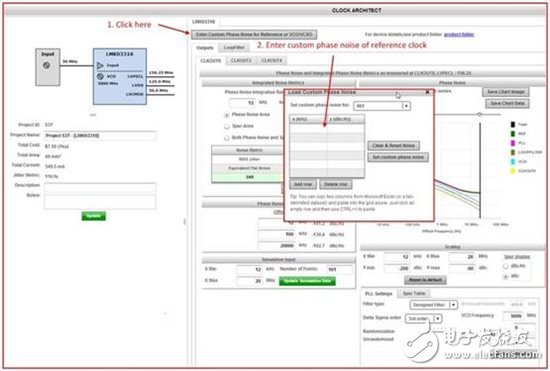

现在你可以输入与外部基准有关的定制相位噪声系统配置,比如说晶体振荡器 (XO)、压控晶体振荡器 (VCXO) 和压控振荡器 (VCO)。外部基准源的准确建模可以极大地提升器件输出时钟相位噪声/抖动仿真结果的精度。请见图1。

图1.输入与基准时钟有关的定制相位噪声

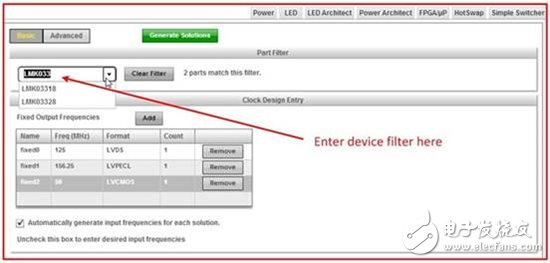

WEBENCH Clock Architect让你从一个下拉列表中选择一个特定的TI计时器件(或者使用常规表示法的多个器件)。图2是你在选择所需器件、敲入输入和输出频率、并且设计一个环路滤波器或仿真相位噪声时的屏幕截图。

图2:器件过滤器

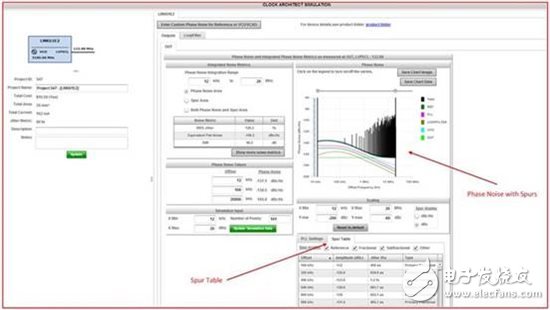

在这款工具中得出的相位噪声仿真值与实际芯片性能进行紧密匹配。然而,直到最近,分数倍分频锁相环 (fractional-N PLL) 的相位噪声仿真并不包含杂散。对WEBENCH Clock Architect的最近一次升级包括PLL相位检测器的建模, 以及针对大多数器件的分数、次分数和其它部件特有杂散的建模。我们一直努力提高这款工具的杂散建模水平,并且不断升级与特定产品相关的功能。图3显示的是一个分数倍分频锁相环的示例,以及它所生成的带有杂散的输出时钟相位噪声曲线图。

图3:带有杂散的输出时钟相位噪声曲线图

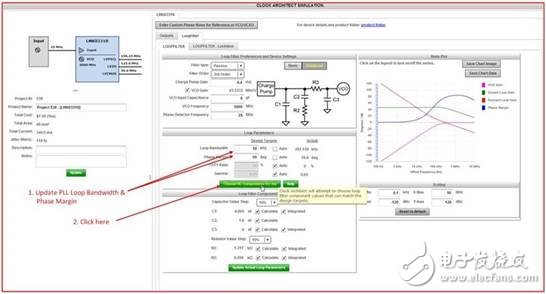

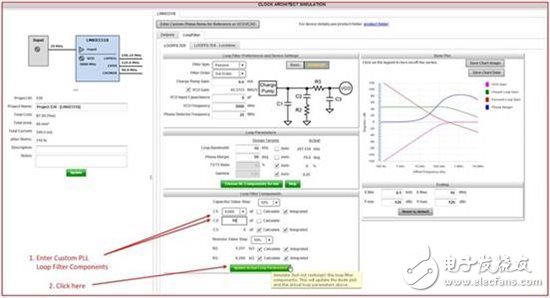

我们也对PLL滤波器设计功能进行了某些升级。在最近发布的版本中,如图4的屏幕截图中所示,高级用户能够定制PLL带宽、相位裕量和gamma值等环路滤波器参数。你可以输入定制环路滤波器组件值或者从一个整数值列表中选择(如果这款器件提供这些数据的话),然后通过仔细查看波特图来检查环路稳定性(图5)。由于包含有PLL锁定时间建模功能,你可以验证环路滤波器设计策略对于PLL锁定时间(以及相位噪声)的影响,并考虑必要的设计均衡与取舍(图6)。

图4:定制环路参数选择

图5:定制环路滤波器组件选择和仿真

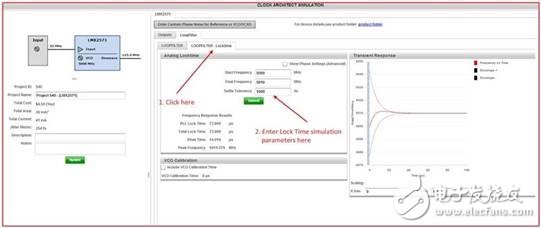

图6:锁定时间仿真和估算

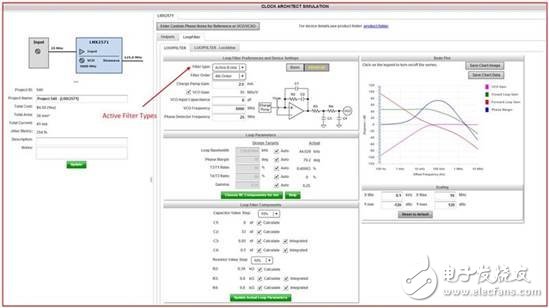

直到近期,WEBENCH Clock Architect还只能够支持无源环路滤波器设计。现在,由于最新的一次升级,这个工具支持有源环路滤波器设计(在Advanced(高级)设置下)。相对于有源环路滤波器,无源环路滤波器通常由于其低成本、简单性和带内相位噪声等因素而受到用户欢迎。不过,在特定情况下—当VCO需要的调谐电压高于PLL电荷泵所能提供的电压时,或者当VCXO的输入阻抗不足时—就必须使用有源滤波器了。请见图7中的下拉菜单。

图7:有源环路滤波器选型和仿真

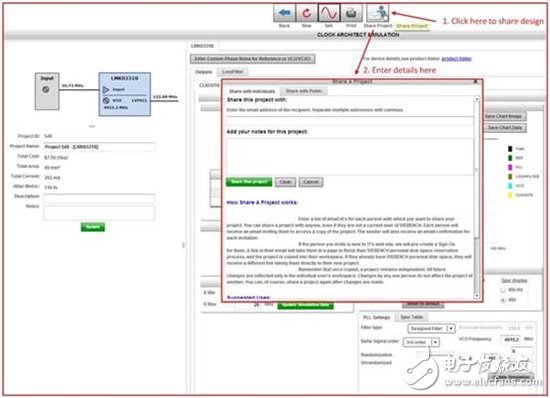

对WEBENCH Clock Architect的最后一个重大升级就是可以与其他用户分享设计。只需单击图8中显示的Share Project(分享项目)按钮,你就可以生成一个包含所有设计细节的PDF格式的报告。

图8:分享设计

为了满足应用的严格要求,TI具有一个健康的产品库,其中包含灵活且高性能时钟发生器、时钟抖动消除器、射频 (RF) PLL/合成器、时钟缓冲器和振荡器。

我所中意的时钟发生器和可编程振荡器分别是LMK03328和LMK61E2。这些器件具有超低RMS抖动性能(典型值100fs)、灵活性(集成EEPROM和ROM),以及丰富特性(支持频率裕量设定)。当你的下一个设计使用这些器件以及TI.com内所提供的很多其它器时,你可以用WEBENCH Clock Architect来仿真这个设计的相位噪声。

-

晶振时钟怎么校正振荡器频率2015-09-28 0

-

MEMS振荡器是什么?跟我们常说的石英晶振比有什么特别的呢?2016-06-04 0

-

晶振,多谐振荡器和信号发生器2016-11-14 0

-

【转】有源晶振—压控振荡器2018-07-21 0

-

想知道分立式3运算放大器仪表放大器是否需要任何补偿电容?2019-03-09 0

-

分立式逆变器的挑战2019-05-13 0

-

集成压控振荡器的宽带锁相环真的能取代分立式解决方案吗?2019-07-31 0

-

如何进行分立式设计?2022-11-23 0

-

电源变换器集成式和分立式的作用特点2018-08-02 3224

-

PowerLab 笔记:如何进行分立式设计2022-11-07 297

-

集成压控振荡器的宽带锁相环能取代分立式解决方案吗2023-11-22 83

全部0条评论

快来发表一下你的评论吧 !