东芝和日本半导体擦出火花,新技术为模拟电源IC提高可靠性

描述

低电压模拟电源IC、物联网和电动汽车领域发挥着越来越重要的角色,由于工业机械和车辆的运行都需要很长的时间,这就对工业和车载中所用的IC提出了更高的可靠性要求。

提高IC的可靠性能,这是一项听似简单但操作起来十分棘手的工艺技术。不少半导体公司为此开发出了N通道LDMOS,它能为电机控制IC和电源管理IC提供低的RON特性和高可靠性,应用前景被广泛看好。

但就在这个时候,东芝的研究发现N通道LDMOS有一个负面特性,即其关断状态的泄漏电流(“IOFF”)因长时间使用而急剧增加。增加的IOFF有什么危害呢?它将导致电路运行故障,增加待机功耗!所以,改进N通道LDMOS的关键在于找到抑制IOFF的方案。

如何抑制IOFF?

在研发相关技术的过程中,东芝与其制造子公司——日本半导体擦出了强烈的火花。

东芝凭借着在晶体管设计方面的专有知识,加上日本半导体在车载模拟IC业务中所积累的工艺技术,利用TCAD仿真和实验数据,分析了IOFF的机理,并确定了两种可抑制IOFF增加、具有卓越容差的结构。

它们分别是具有扩展STI的结构和阶梯式氧化物结构:

3个N通道LDMOS结构的截面图

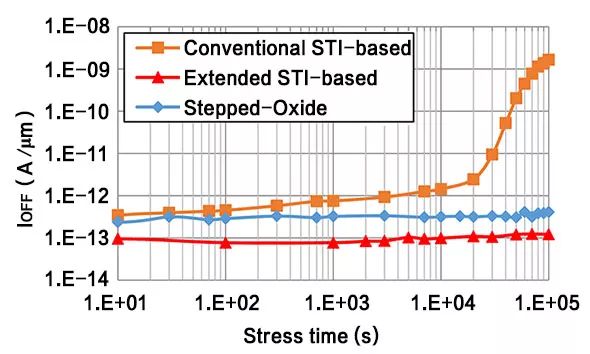

两个新结构与传统结构中的IOFF比较

第一种结构适合于LDMOS只占芯片总面积一小部分的模拟电路,比如电机控制IC,因为它不需要附加的工艺步骤但RON仍会增加。第二种结构更适用于LDMOS占芯片总面积较大部分的模拟电路,比如电机驱动器IC和DC-DC转换器,因为它即便采用附加的工艺步骤仍具有较低的RON且具有成本效益。

针对以上异同,我们可以在芯片设计或应用中选择合适的LDMOS结构。

总言之,通过TCAD仿真的阶梯式氧化物结构设计优化将使得LDMOS比传统LDMOS更有效地降低RON,从而实现更强的可靠性。LDMOS的寿命提高了5倍,大大提高了模拟电源IC的寿命。

东芝和日本半导体共同研发的这项新技术目前已被广泛认可,并在5月16日于芝加哥举行的2018年功率半导体器件和IC国际研讨会(ISPSD 2018)上被详细报告,它有望在明年被引入模拟电源IC中。

接下来,东芝和日本半导体在半导体工艺研发上还会擦出怎么样的火花呢?芝子表示敲期待的!

-

提高开关电源可靠性的技巧2018-10-09 0

-

提高电源可靠性设计的建议2018-10-09 0

-

可实现高可靠性电源的半导体解决方案2018-10-17 0

-

提高PCB设备可靠性的技术措施2018-11-23 0

-

SiC-SBD关于可靠性试验2018-11-30 0

-

集成电路在高可靠性电源的应用2019-06-11 0

-

电源突破性的新技术2019-07-16 0

-

基于集成电路的高可靠性电源设计2019-07-25 0

-

【PCB】什么是高可靠性?2020-07-03 0

-

什么是高可靠性?2020-07-03 0

-

为什么华秋要做高可靠性?2020-07-08 0

-

【PCB】为什么华秋要做高可靠性?2020-07-09 0

-

如何实现高可靠性电源的半导体解决方案2021-03-18 0

-

实现高可靠性电源的半导体解决方案2017-10-20 9460

全部0条评论

快来发表一下你的评论吧 !