资料下载

×

通过调节稳压器优化DSP功率预算的详细方法资料概述

消耗积分:0 |

格式:rar |

大小:0.18 MB |

2018-07-18

系统级节电与功率预算优化是许多应用的关键。例如,数据中心运营商努力控制能耗,便携式设备设计人员力图降低流耗实现更长的电池使用寿命,而通信系统则需要降低工作温度提高稳定性。电源设计主要规范的当前着眼点是:

1)在整个负载电流范围内最大限度提高效率;和

2) 根据负载需要自适应缩放输出电压

使用电压识别(VID) 调节输出电压是满足这些需求的方法之一。当然,在英特尔和AMD 提供的众所周知的自适应电压缩放(AVS) 规范基础上,VID 可编程性已经在微处理器应用的DC/DC 内核电压稳压器中得到了广泛使用。然而,这些VID 控制器建立在多相位降压拓扑基础之上,在特性上专门围绕超大电流需求进行了定制。

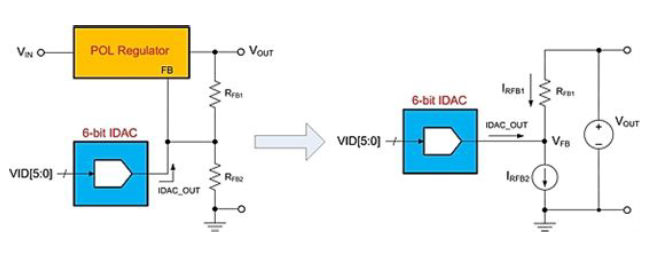

DSP、FPGA 以及ASIC 现在具有类似的功能,可根据器件活动、电源及时钟域配置、工作模式以及工作温度,实现最大限度的功耗降低。虽然支持VID[1] 的数字化脉宽调制器(PWM) 控制器解决方案可用来满足这一需求,但确实也需要对无处不在地模拟控制负载点(POL) 稳压器进行输出电压数字化调节。在调节过程中,可轻松调整模拟电源实施(或许已经完成设计或已经通过测试台测试),满足其它方案无法实现的系统级功率预算与成本目标要求。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。 举报投诉

评论(0)

发评论

- 相关下载

- 相关文章