半加器和全加器的原理及区别(结构和功能)

电子说

1.4w人已加入

描述

半加器

半加器+半加法和全加法是算术运算电路中的基本单元,它们是完成1位二进制相加的一种组合逻辑电路。一位加法器的真值表见表1.1;由表中可以看见,这种加法没有考虑低位来的进位,所以称为半加。半加器就是实现表1.1中逻辑关系的电路。被加数A加数B和数S进位C0000011010101101

表1.1一位半加法器真值表

全加器

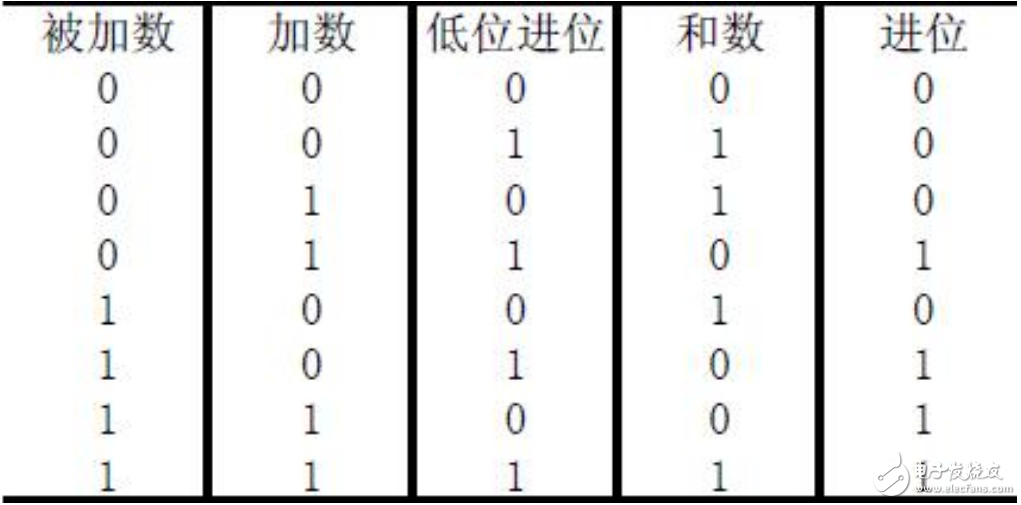

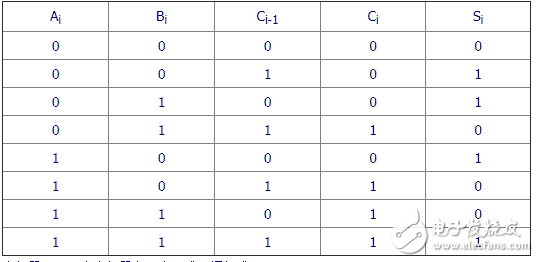

全加器能进行加数、被加数和低位来的进位信号相加,并根据求和结果给出该位的进位信号。根据它的功能,可以列出它的真值表,如表1.2所示。

半加器和全加器的区别

1、半加器

在数学系统中,二进制加法器是它的基本部件之一。

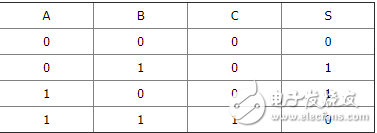

半加器(半加就是只求本位的和,暂不管低位送来的进位数)的逻辑状态表

其中,A和B是相加的两个数,S是半加和数,C是进位数。

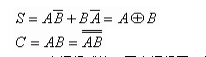

由逻辑状态表可写出逻辑式:

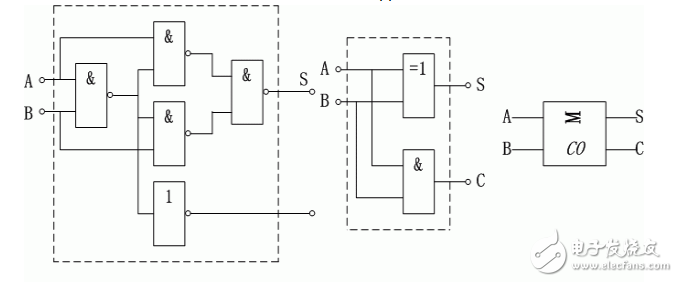

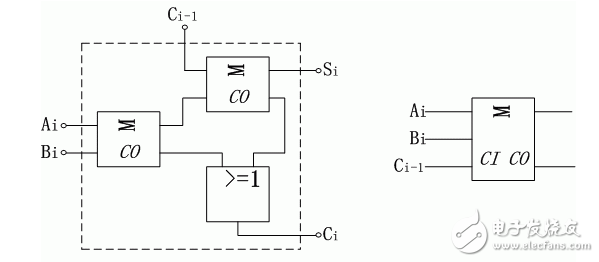

由逻辑式就可画出逻辑图,如下图(a)和(b)所示,由一个“异或“门和一个”与“门组成。半加器是一种组合逻辑电路,其图形符号如下图(c)所示。

2、全加器

当多位数相加时,半加器可用于最低位求和,并给出进位数。第二位的相加有两个待加数和,还有一个来自前面低位送来的进位数。这三个数相加,得出本位和数(全加和数)和进位数。这种就是“全加“,下表为全加器的逻辑状态表。

全加器可用两个半加器和一个“或“门组成。

如上图(a)所示。和在第一个半加器中相加,得出的结果再和在第二个半加器中相加,即得出全加和。两个半加器的进位数通过”或“门输出作为本位的进位数。全加器也是一种组合逻辑电路,其图形符号如上图(b)所示。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

半加器和全加器的功能特点2024-10-18 5543

-

请用Verilog分别实现1位半加器和1位全加器2023-06-26 4572

-

层次化设计构成全加器2023-05-22 2495

-

基于FPGA层次化设计构成全加器2023-05-14 2598

-

FPGA入门——1位全加器设计 精选资料分享2021-07-26 1537

-

全加器逻辑表达式_全加器的逻辑功能2020-04-23 134478

-

全加器是什么?全加器和半加器的区别?2018-07-25 76338

-

什么是一位全加器,其原理是什么?2010-03-08 78209

全部0条评论

快来发表一下你的评论吧 !