数字电路中最简单的混频知识

电子说

描述

混频就是把两个不同的频率信号混合,得到第三个频率。在模拟电路中经常见到的就是把接收机接收到的高频信号,经过混频变成中频信号,再进行中频放大,以提高接收机的灵敏度。

数字电路中最简单的混频便是两个信号做乘法,可以得到它们的和频信号与差频信号。数字混频在通信的调制、解调、DUC(数字上变频)、DDC(数字下变频)等系统中应用广泛。通常把其中一个信号称为本振信号(local oscillator),另一个信号称为混频器的输入信号。

程序设计

程序设计系统时钟5MHz,625kHz的输入信号与625kHz的本振信号做混频,根据混频原理会得到1.25MHz的和频信号与0Hz(直流),将直流滤除掉得到1.25MHz的有效信号。

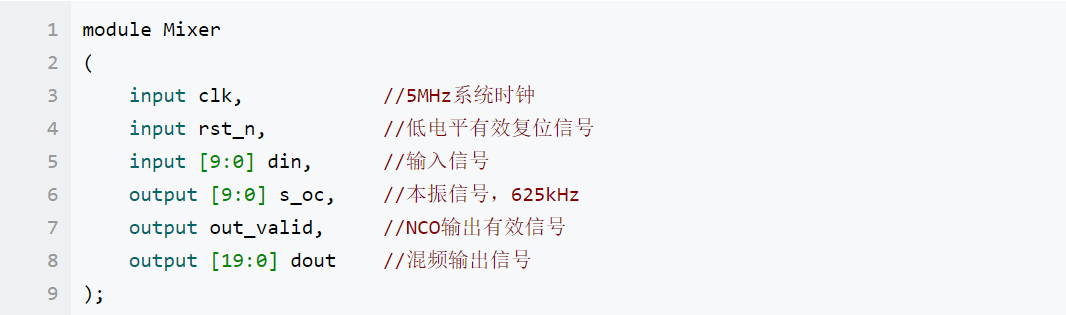

设计的顶层模块接口如下所示:

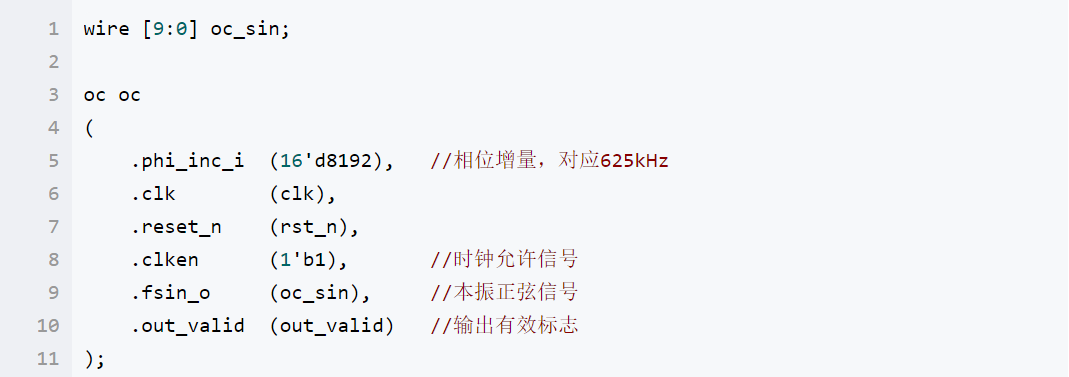

程序中首先生成本振信号。Quartus和Vivado中都提供了类似功能的IP核:Vivado中叫DDS(Direct Digital Synthesizers)Compiler;Quartus中叫NCO(Numerically controlled oscillators)。下面以实例化NCO为例,具体的设计方法在下文讲解。

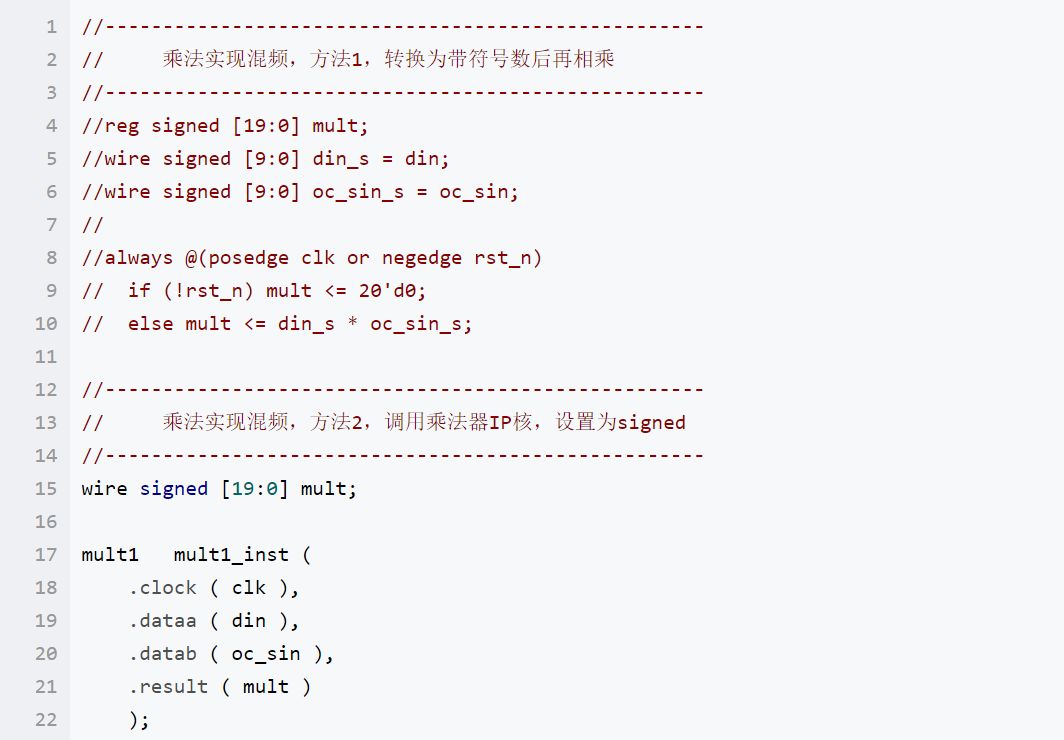

接下来用乘法进行混频。我们都知道计算机中有带符号数signed和无符号数unsigned,还知道计算机经常以二进制补码的形式的表示带符号数。

在FPGA设计中,不管是Altera还是Xilinx,它们的IP核几乎都是采用二进制补码带符号数,也有很多的ADC、DAC芯片的数据接口也采用的是二进制补码。因此,在设计中,我们要清楚什么时候用什么数值表示法。比如NCO的输出为带符号数二进制补码,假设混频的输入信号也是带符号数二进制补码,则在整个混频程序设计中都要保持这个数值表示方法,否则就会出错。

在下面的方法1中,再定义一个带符号的寄存器将输入信号转换为带符号数是很有必要的:“wire signed [9:0] din_s = din;”。如果不这样做,直接使用乘法运算符“*”,会被综合为无符号数乘法,得到的就是错误的结果。

当然也可以用方法2,乘法器IP核可以选择计算方式是“signed”还是“unsigned”,将乘法器设置为signed也可以完成正确的计算。

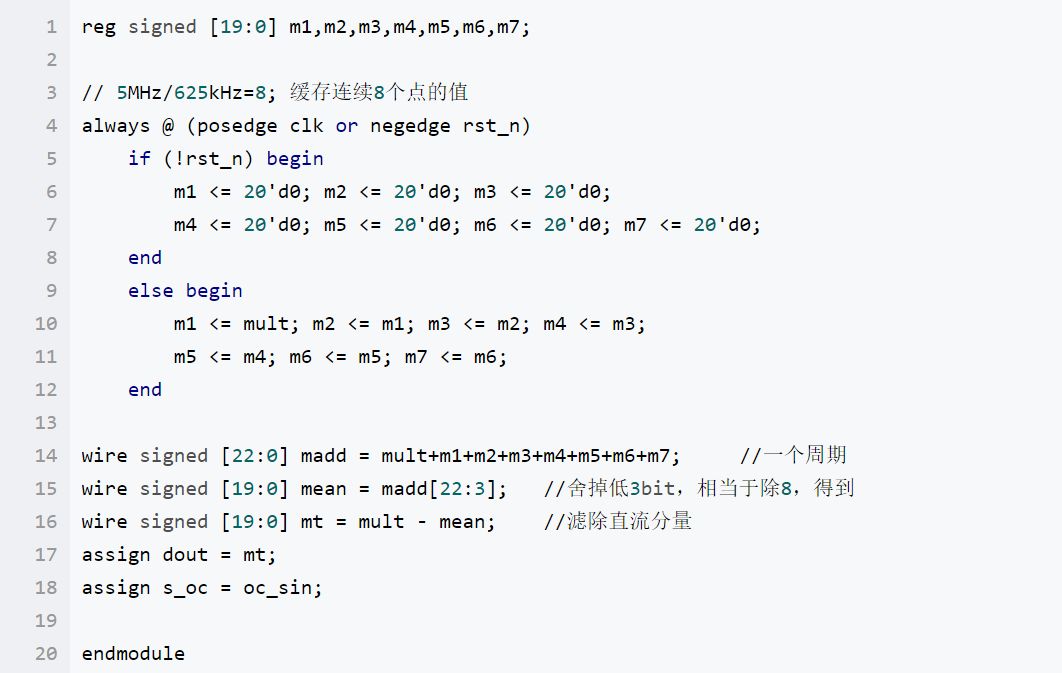

接下来滤除混频后的直流信号。由于乘法的运算结果为带符号数,接下来的计算使用到的寄存器都应申明为signed。需要强调的是,signed和unsigned的申明只是告诉设计的运算如何看待这个寄存器中的数,并不能改变寄存器的值。比如“11”这个值,如果申明为signed,运算将其视作-1,如果申明为unsigned,运算将其视作3。因为有符号数和无符号数的运算法则是不一样的,所以错误的申明会导致结果计算错误。

上面滤除直流分量的方法并不通用,由于5Mhz的系统时钟是625kHz信号的8倍,所以连续8个点的平均值便是直流分量。不过程序设计思路还是可以学习,比如依次移位缓存数据、截高位做除法这些小技巧。

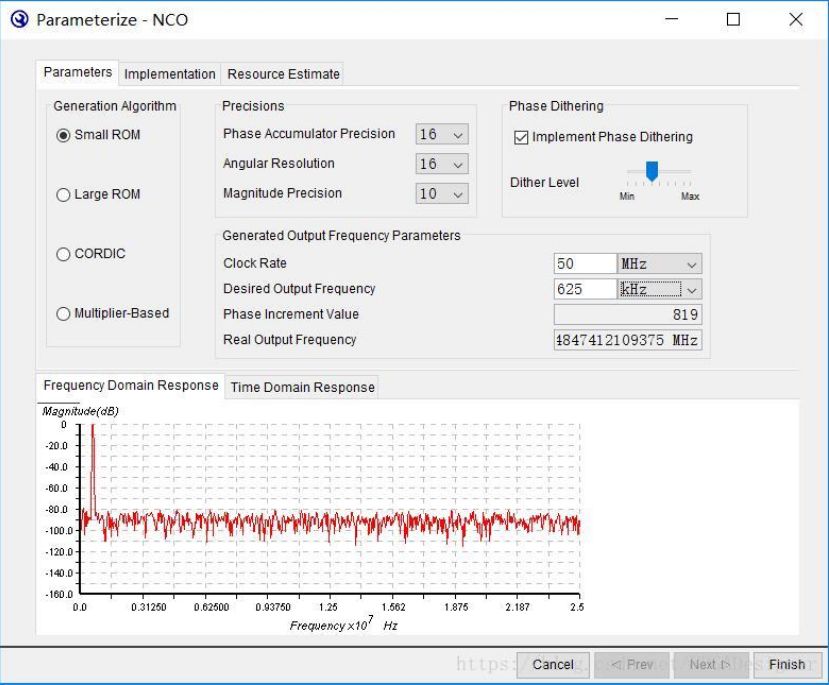

NCO IP核的使用

在Quartus中打开该IP核,配置界面如下。后面的Quartus版本中将IP核集成到了qsys中,配置界面略有不同,但设置的参数之类的基本一样。

设定好相位累加器精度、角度分辨率、幅度精度、系统时钟和输出信号频率,便可以得到一个相位增量值(phase increment value),在实例化NCO模块时传入的便是这个值。实际的输出频率和设定的频率会存在一定误差,下方便展示了输出信号的频域和时域图形。总体来说设置比较简单。

如果需要仿真,在生成IP核前一定要在“Set up simulation”中选中“Generate Simulation Model”和“Generate netlist”,如下图所示。否则在导入ModelSim时会失败,无法进行仿真。

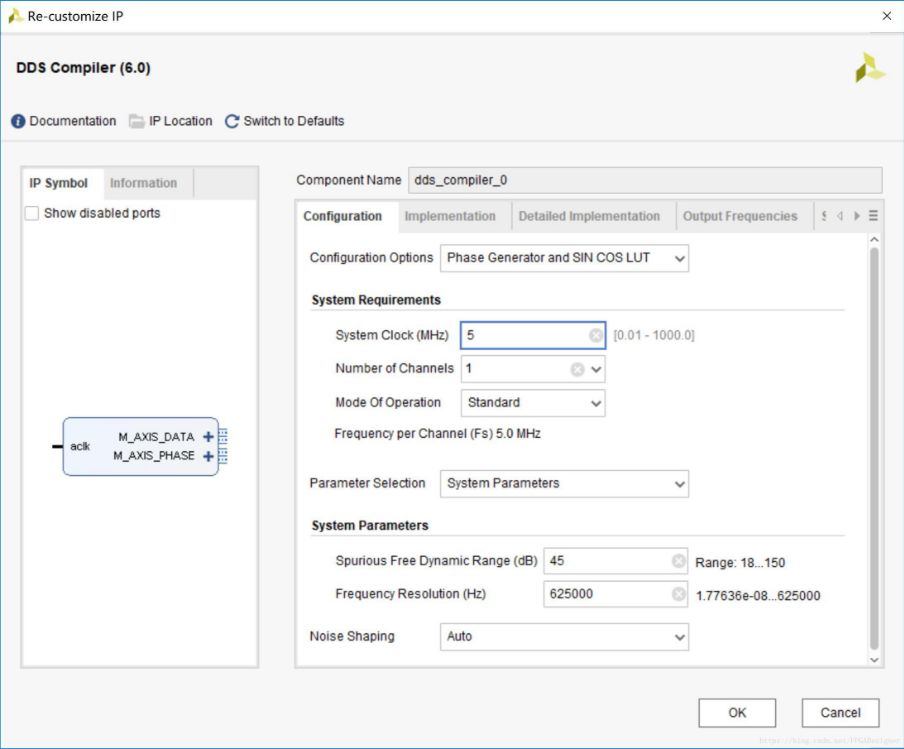

DDS Compiler IP核的使用

01

基本配置

在Vivado中打开DDS Compiler IP核,配置界面如下:

同样设定系统时钟,Parameter Selection选择“System Parameters”,这种设计方式可以直接设置无杂散动态范围、频率分辨率、输出频率等系统级的参数,和Quartus的NCO IP核很像。另外一种“Hardware Parameters”设计方式需要自己设定输出数据和相移的位宽,输出频率、相位偏移等值需要自己计算对应的二进制数值。这两种设计方式向不同需求的设计者提供。

总线位宽与系统参数之间的转换关系公式参考Xilinx官方文档pg141。

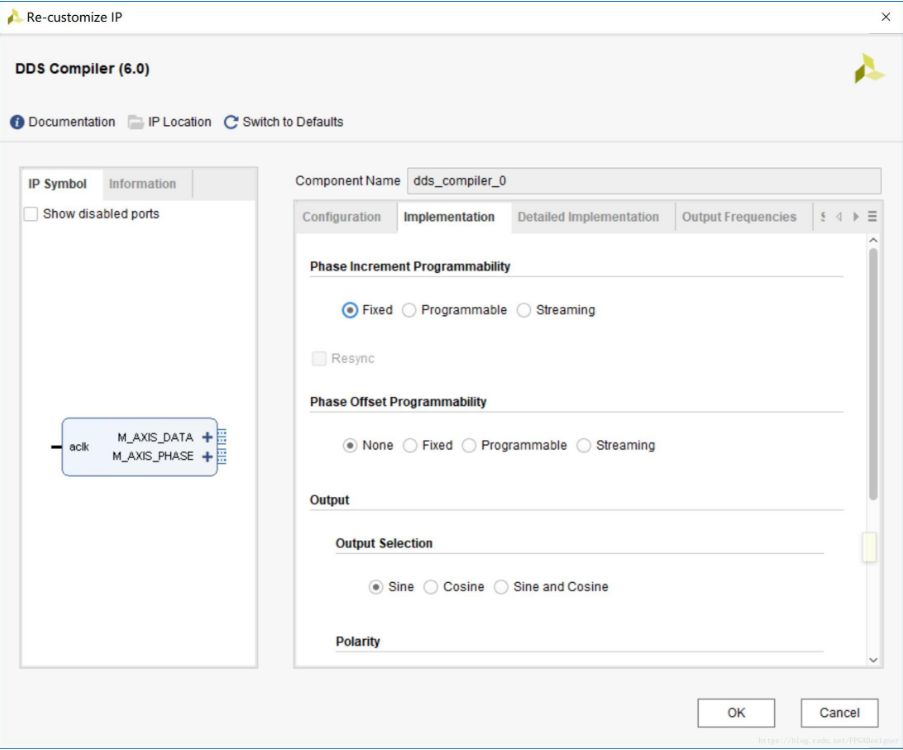

相位增量和相位偏移都可以设置为可编程的“Programmable”和“Streaming”方式,本设计只需要产生625kHz固定频率的本振信号,设置为“Fixed”即可(所需资源少)。在“Summary”中可以看到整个DDS系统的详细信息。

02

位宽问题

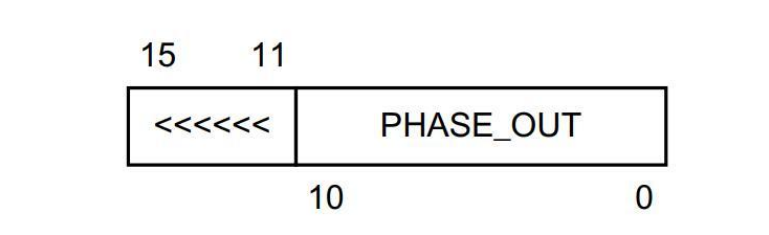

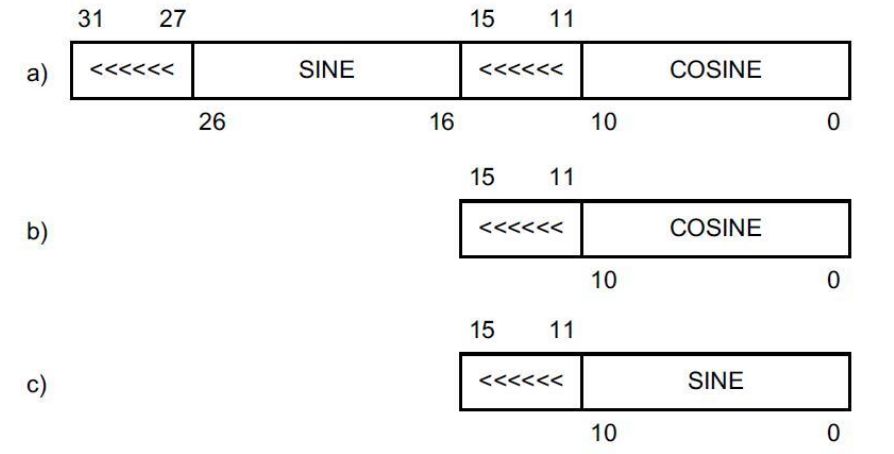

需要提醒的是系统最终的实际信号位宽和总线接口位宽并不一致。IP核的位宽只会是8的倍数,多余的位数会移符号为填充,如下图所示。

更直观的感受,看一个DDS Compiler IP核的仿真:

可以看到相移虽然有16bit的位宽,但是有效的只有低10bit,高位都是符号为。为了更好的观察相位值,新建一个“virtual bus“,将低10bit加到bus中,如下图所示:

可以清楚的看到相位和幅度之间的关系。

03

产生sin与cos信号

很多系统中需要sin和cos信号(如解调系统中的本振信号),在DDS中设置为“Sine and Cosine”输出时,sin和cos信号会共用数据总线,sin使用高字节,cos使用低字节,格式如下:

04

产生带有相位偏移的信号

如果需要生成带有可调初始相位(也叫相位偏移Phase Offset)的信号,在DDS中将“Phase Offset Programmability”设置为“Streaming”,IP核端口会增加一个PHASE输入通道,该通道数据总线的有效位宽与设置的频率分辨率(Frequency Resolution)有关,可以在Summary界面中看到位宽(Phase Width)。该数据总线与360°相位之间线性对应。比如Phase Width为16Bits,则0对应0°,FFFF对应360°,7FFF对应180°,以此类推。

NCO和DDS是经常用到的IP核,在后面的“FPGA数字信号处理“系列介绍的其它系统中,也会经常出现,因此需要熟悉掌握这两个IP核的使用。

-

模拟和数字电路基础知识汇总2016-12-26 0

-

新编数字电路与数字逻辑2018-10-28 0

-

模拟电路与数字电路的基础知识详解2022-01-25 0

-

数字电路及其应用2009-04-07 3353

-

数字电路图2009-07-17 1469

-

数字电路基础知识2011-04-01 4892

-

看懂数字电路的四个必备知识2016-11-16 16559

-

数字电路基础知识与要点2017-09-19 1424

-

数字电路中最基本的门电路2022-09-16 2598

-

17个图解数字电路基础知识2023-01-14 9443

-

数字电路的基础知识2023-02-23 17467

-

数字电路基础知识分享12023-05-04 741

-

数字电路知识点总结2023-05-30 2955

全部0条评论

快来发表一下你的评论吧 !