通过C代码和Intel手册详细理解cache参数

描述

Cache的容量一般都很小,即使是最大的三级 Cache(L3)也只有20MB ~30MB。cache加快了CPU对内存的读写速率,CPU第一次执行需要将数据时候需要从主存-->L3 Cache--->L2 Cache -->L1 Cache传递到CPU的计算单元。cache分成多个组,每个组分成多个行,linesize是cache的基本单位,从主存向cache迁移数据都是按照linesize为单位替换的。下面通过C代码和Intel手册详细理解cache参数。

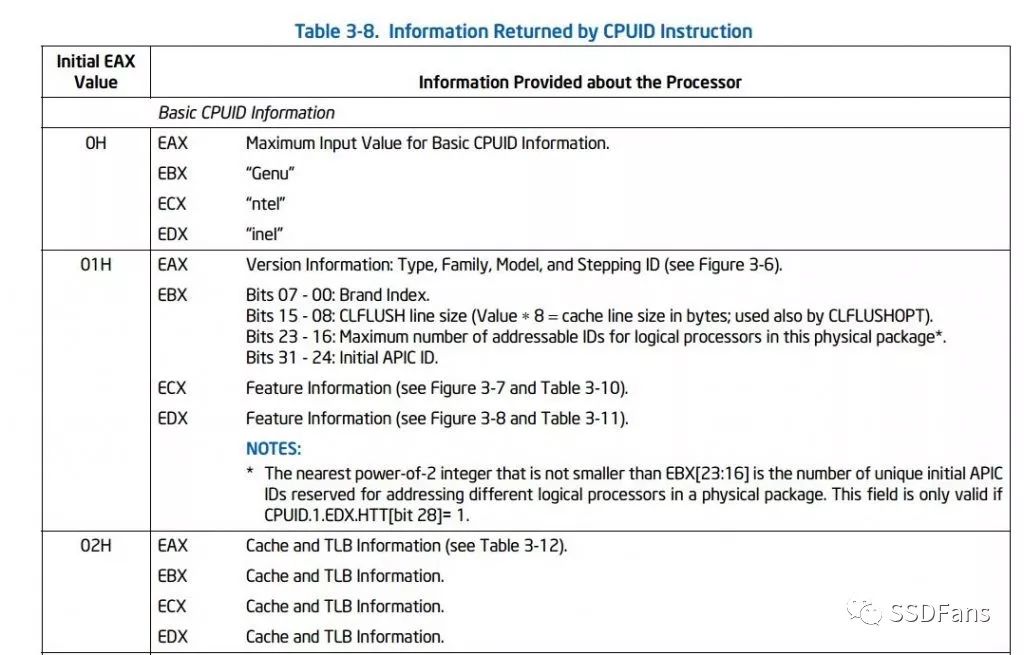

Intel CPU可以通过CPUID命令获取cpu相关信息,查询Intel可以获取到相应的指令信息,获取cache 参数有下面两种方法:分别是当CPUID指令Initial EAX Value为0x02和0x04时候,由于方法一种CPUID指令的入口参数存放在EAX寄存器中,所以获取cache信息需要给EAX寄存器赋值为0x02,然后分别读取EAX、EBX、ECX、EDX四个寄存器得到Cache and TLB Information。查看Intel手册(图1)得到方法一的指令码。

图1

参考Linux内核中header.c文件中的cpuid函数实现获取cache代码函数,图2有两种方式实现获取cache函数,原理都是一样,赋值然后读取值。

图2

本次试验采用gcc 4.7.2版本编译程序并且运行得到如下结果:

d_eax : 55035a01

d_ebx : f0b2de

d_ecx : 0

d_edx : 9ca212c

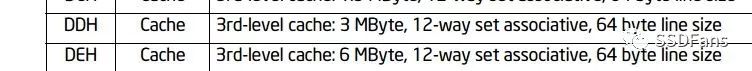

查看intel 手册可以得到每个字节的解释,ebx寄存器中低八位查表得到如图3所示相关信息,3级cache 容量6M,12路组相连(每组有12个line),每个line大小为64 字节。其它信息查表得到如下:

EAX:

(55h) Instruction TLB: 2-MB or 4-MB pages, fully associative, 7 entries

(03h) Data TLB: 4-KB Pages, 4-way set associative, 64 entries

(5Ah) Data TLB0: 2-MB or 4-MB pages, 4-way associative, 32 entries

(01h) Instruction TLB: 4-KB Pages, 4-way set associative, 32 entries

EBX:

(F0h) 64-byte Prefetching

(B2h) Instruction TLB: 4-KB pages, 4-way set associative, 64 entries

(DEh) 3rd-level cache: 6-MB, 12-way set associative, 64-byte line size

EDX:

(09h) 1st-level Instruction Cache: 32-KB, 4-way set associative, 64-byte line size

(CAh) Shared 2nd-level TLB: 4-KB pages, 4-way set associative, 512 entries

(21h) 256KB L2 (MLC), 8-way set associative, 64-byte line size

(2Ch) 1st-level data cache: 32-KB, 8-way set associative, 64-byte line size

从上面信息得到当前CPU的cache信息如下:

L1 Cache : 32KB , 8路组相连,linesize为 64Byte 64个组

L2 Cache:256KB 8路组相连,linesize为 64Byte 512个组

L3 Cache:6MB 12路组相连,linesize为 64Byte 8192个组

图3

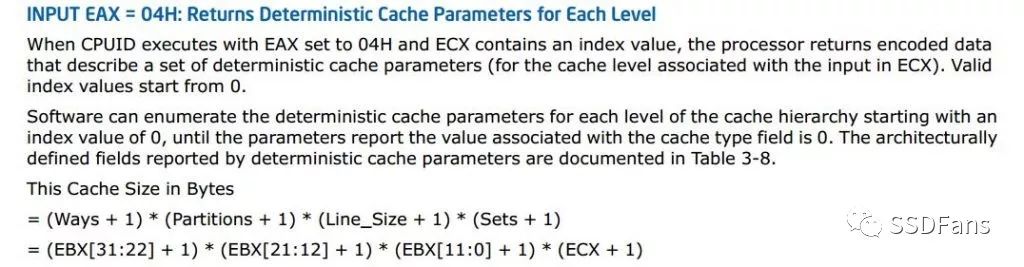

获取cache参数的另外一种方法,查阅Intel手册(图4)得到当CPUID的Initial EAX Value为0x04时得到cache十六进制数,在根据图4中的编码信息获取cache详细参数,执行该CPUID命令时还需要设置另外一个入口参数ECX,ECX寄存器设置我们需要查询哪一个cache ,ECX的输入与cache对应如下:

0:L1D

1:L1I

2:L2

3:L3

图4

执行CPUID Initial EAX Value 等于0x04时,返回的EAX、EBX、ECX、EDX寄存器值得位信息如图5所示。

图5

EAX[4:0]=1,表示这是一个数据Cache。EAX[7:5]=1,表示该Cache的级别为1,即为L1D。EAX[8]=1表示该Cache处于自初始化的Cache层(Seache Level)。EAX[9]=0,表示此Cache不是全相联Cache。EAX[25:14]=1表示能够共享此Cache的最大线程数为2。EAX[31:26]=15,表示这个处上,最多支持16个核心。EBX[11:0]=63表示Cache LineSize为64字节。EBX[21:12]表示此Cache不支持硬件Cache Line分区。EBX[31:22]=7,表示此Cache为8路组相联

7表示此Cache的组数为8组。

获取L3 cache详细参数代码如图6所示:

图6

代码运行结果如下:

d_eax : 163

d_ebx : 2c0003f

d_ecx : 1fff

d_edx : 6

计算L3 cache容量公式如下:

Size = (Ways + 1) * (Partitions + 1) * (Line_Size + 1) * (Sets + 1)

= (EBX[31:22] + 1) * (EBX[21:12] + 1) * (EBX[11:0] + 1) * (ECX + 1)

=(0x2c0003f>>22+1)*((0x2c0003f&0x003FF000)>>12+1)*(0x2c0003f&0x00000FFF+1)*(0x1fff+1)

= 6291456 B=6144 K=6M

获取其它cache 只需要修改传入cpuid的ecx参数,如果需要获取CPU的其它信息,可以查看Intel 指令手册修改传入EAX参数的值

-

C6678芯片CACHE设置问题2018-06-21 0

-

cache 问题2018-06-21 0

-

如何理解C6678中关于cache的描述?2018-06-21 0

-

请问C6748CACHE操作的寄存器在哪个文档里面有详细的解释?2018-08-01 0

-

关于C6747的cache2018-08-02 0

-

关于芯片数据手册参数理解的问题2019-12-16 0

-

C64x+与C64x CACHE的区别是什么2020-12-14 0

-

系统级动态二进制翻译中的代码Cache索引2009-04-11 560

-

cache对写好代码真的有那么重要吗2021-07-26 1545

-

Page Cache是什么 一文带你深入理解Linux的Page Cache2021-10-20 5411

-

从三个方面阐述Cache2021-11-21 2179

-

什么是 Cache? Cache读写原理2022-12-06 1262

-

宋宝华:深入理解cache对写好代码至关重要2022-12-06 493

-

深入理解Cache工作原理2023-05-30 462

-

Cache内容锁定是什么2023-10-31 366

全部0条评论

快来发表一下你的评论吧 !