1394b数据传输有什么特点?如何利用FPGA设计一个1394b双向数据传输系统?

可编程逻辑

描述

引言

随着时代和技术的发展,对于数据总线带宽的要求越来越高,现有的总线标准越来越难以满足实际应用中对高总线速率的要求。先进的总线技术对于解决系统的瓶颈,提高系统性能起着至关重要的作用,同时为了实现批量数据的传输,IEEE又公布了支持更高传输速率的IEEE Std 1394b-2002(简称1394b)串行总线标准,高速可升级性可支持高达800 Mb/s下的数据传输速率,并且能够向后兼容先前的1394-1995和1394a标准。由于1394b是一种数据传输速率更高的串行总线标准,支持异步传输和等时传输两种传输方式。分层的软件和硬件模型可使其通信建立在事务层、链路层和物理层协议的基础之上。本文充分利用FPGA和DSP芯片的硬件资源,基丁1394b传输协议和规范的基础上,介绍139 4b数据传输系统的硬件设计结构、系统的工作流程和总线的配置过程。

1 1394b的特点

1394b双向数据传输系统的主要特点如下:

(1)高速可升级:支持100 Mb/s、200 Mb/s、400 Mb/s和800 Mb/s的传输速率,使用塑料光纤时可以提高到3.2 Gb/s;

(2)支持点到点传输:各个节点可脱离主机自主执行事务;

(3)即插即用:可以在任何时候向1394b网络添加或移除设备,既不用担心会影响数据的传输,也不需要进行重新配置,总线会重新枚举,节点也可以自动配置,无需主机干预;

(4)热插拔:无需将系统断电就可以加入或移除设备;

(5)传输距离:采用CAT-5UTP5线(5类非屏蔽双绞线)时,可以保证传输速率在100 Mb/s的前提下将传输距离延长至100 m,使用玻璃光纤时可在3.2Gb/s的前提下延长至50 m;

(6)支持两种传输方式:包括等时(Isochronous)和异步(Asynchronous)数据传输方式;

(7)拓扑结构:设备间采用树形或菊花链拓扑结构,每条总线最多可以连接63台设备;

(8)可提供电源:一些低功耗设备可以通过总线取得电源,而不必为每一台设备配置独立的供电系统;

(9)公平仲裁:等时传输具有较高的优先级,同时异步传输也能获得对总线的公平访问;

(10)提高系统性能:将资源看作寄存器和内存单元,可以按照CPU内存的传输速率进行读/写操作,因此具有高速传输能力。

2 1394b数据传输系统的硬件实现

由于1394b链路层芯片必须通过PCI总线接口与FPGA进行相连,实现数据的传输。如果只用FPGA和DSP来实现对PCI外设的控制,需要设计复杂的接口逻辑,在1394b高速数据传输系统中不仅会影响FPGA本身的性能,而且会给FPGA之外的电路或者系统带来诸多问题。因此这里采用PCI9054总线接口芯片配合FPGA和DSP来实现1394b双向数据传输系统,将对复杂的PCI总线接口的控制转换为对相对简单的本地总线接口的控制,不仅对PCI协议有着良好的支持,而且提供给设计者良好的接口,大大减少了设计者的工作量。PCI9054芯片在PCI总线端支持32位/33 MHz,当本地总线端采用32位数据总线时,其数据传输速率可达132 MB/s,故能够满足1394b总线上800 Mb/s的数据传输速率要求。

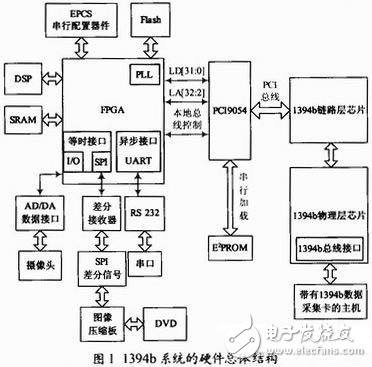

本设计中的主控芯片采用Altera公司的EP2C70F672C6型FPGA主流芯片,DSP选用TI公司的TMS320C6415 DSP芯片,1394b套片选用TI公司的链路层芯片TSB82AA2和物理层芯片TSB81BA3,PCI9054采用PLX公司的32位33MHz的PCI总线通用接口芯片。1394b双向数据传输系统的硬件总体结构图如图1所示,主要由现场可编程门阵列(FPGA)模块、DSP模块、AD/DA数据转换接口模块、SPI数据输入/输出接口模块、串口(UART)通信模块、SRAM存储模块、EPCS串行配置器件模块、FLASH存储模块、PCI9054模块以及1394b套片模块组成。

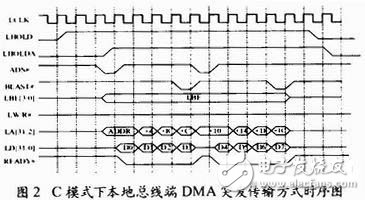

由于PCI9054内部可编程FIFO存储器的存在,数据可以大批量突发传输而不丢失,这样不仪满足实时性要求,同时可以根据用户的需要采用与PCI时钟异步的本地端时钟,PCI9054本地总线工作在C模式时,通过芯片内逻辑控制,将PCI的数据线和地址线分开,很方便地为本地端总线工作时序提供各种方式。图2所示为PCI9054在C模式下与FPGA相连的本地总线数据突发DMA传输方式的时序图,其中,LCCLK为输入时钟信号,从图2中可以看出,在本地端总线上读写数据时,可以不间断地进行突发传输,当数据不能连续传输时,则可以插入等待状态,这样可以大大提高数据的吞吐量。

3 1394b数据传输系统的数据流向

由于1394b总线标准支持等时子事务和异步子事务两类子事务,因此,其传输的数据类型分为等时数据和异步数据,等时传输将数量不定的数据按照规定的时间间隔向某个地址发送,对实时性要求较高,不需要返回确认信号;而异步传输是将数据传送到特定的地址,对数据传输的准确性要求较高,需要接收端以多次握手的方式发送返回确认信号。在本系统中由DVD播放器发送的数据经图像压缩板压缩后由SPI口传入FPGA,或者由摄像头发送的数据经过A/D转换,再由FPGA的通用I/O口送入FPGA,两者均为等时数据;而一些控制命令等异步数据则由串口送入FPGA,并经过DSP进行处理,DSP和FPGA相结合可以提高数据传输的效率。FPGA实现数据的串并转换以及数据的拼接并对数据打包成符合1394b协议的数据包类型以及配置数据包的包头信息,经过读/写FIFO并在外部的SRAM进行缓存,通过DMA仲裁模块进行仲裁处理,用DMA这一快速数据传输机制将数据写入PCI9054的FIFO中。PCI9054作为一种桥接芯片,在本地总线和PCI总线之间提供信息传递,通过PCI9054芯片将本地端数据总线标准转换成能被1394b链路层芯片传输的PCI总线数据标准,再通过1394b的链路层芯片实现对等时和异步数据包的地址和信道号的解码、数据校验、数据分析等,最后由物理层芯片通过仲裁逻辑实现对总线的存取,并对本地节点要发送的数据进行编码,由物理层芯片提供的电气和机械接口将数据位发送到与之相连的1394b线缆上去,最终送入接有1394b板卡的主机进行DVD发送的数据解压缩和播放,以便对摄像头发送的视频进行播放以及异步数据的显示等操作。读出的数据则由接有1394b板卡的主机发送,并通过1394b物理层芯片、1394b链路层芯片、FPGA、外部SRAM等进行数据处理,根据数据包类型由相应的端口送出去,在这期间与发送数据相比进行了相反的操作,这样就实现了1394b双向数据传输系统。

FPGA作为整个系统的控制管理模块,主要完成以下任务:

(1)对SPI端口、UART端口和AD/DA端口数据的发送和接收;

(2)将待发送的数据进行串并转换和数据拼接;

(3)将数据进行打包、解包处理并通过SRAM进行数据的缓存;

(4)与PCI9054芯片进行通信,以完成数据的传送。

本系统中DSP的主要功能是:

(1)与PCI9054芯片和1394b链路层芯片通信实现设备的自举和身份的确认;

(2)发送和接收一些控制命令,控制数据的传输;

(3)实现异步数据的发送和接收功能,根据异步请求数据的类型对其进行相应的处理;

(4)为等时传输申请等时信道和带宽,传输后释放所申请的信道和带宽。

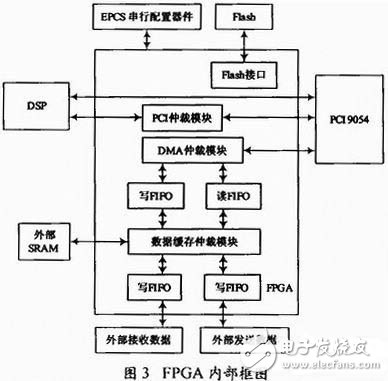

图3所示是系统中FPGA的内部框图,由于数据传输速率较快,数据的处理需要一定的时间,不能将每一组数据无间断的传输,且FPGA内部FIFO容量有限,采用SRAM与FPGA相结合完成输入输出数据的缓存;DSP实现一些辅助的操作如对异步数据的处理、配置PCI9054芯片的内部寄存器和1394b链路层寄存器等操作以及PCI的传输控制、设备识别、为等时传输申请信道和带宽等;EPCS串行配置芯片实现配置数据的存储,使系统上电后将配置数据自动下载到FPGA内部,同时可以用FLASH存储器存放DSP用户代码,在DSP上电工作后,利用DSP提供的boot机制,再将程序下载到DSP RAM中,使本系统实现脱机工作。

4 1394b的系统工作流程

1394b总线的配置是自动进行的,它不受任何设备和主机的干扰。总线配置过程主要有三个步骤:

(1)总线初始化;

(2)自标识;

(3)树标识。

在这三个过程之后,整个系统在逻辑上形成了树状拓扑结构,每个节点都被赋予了一个节点号并都发出节点说明信息。总线的初始化过程如下:

(1)设备识别:设备识别可通过E2PROM来完成;

(2)分配I/O空间和Memory空间;

(3)配置PCI9054的DMA寄存器;

(4)对1394b链路层和物理层芯片进行配置。

由于1394b OHCI(Open Host Control Interface Specification)协议是1394b串行总线链路层协议的一种实现方式。1394bOHCI协议规定1394b的等时传输和异步传输均为DMA方式,所以需要对PCI9054的DMA寄存器进行配置。PCI9054中有两个独立的通道采用DMA方式传输数据可以不受主机的干预,同时采用突发方式传输数据可以提高数据的传输速率,同时也可以充分发挥PCI总线的性能。

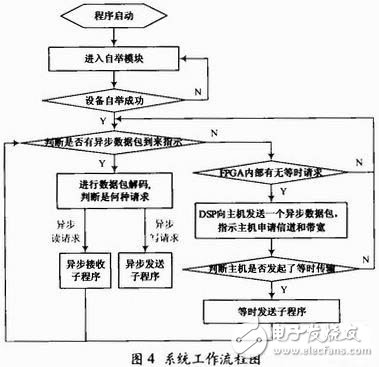

系统上电后,通常需要进行设备的自举,协助主机完成设备识别和设备身份的确认,设备的自举主要包括:初始化链路层寄存器;初始化配置ROM;判断电缆是否插入;强制根节点;响应根节点、读取配置ROM请求直到根节点调用相应驱动程序完成设备识别。图4所示为本系统的工作流程图。

设备自举完成以后,即可等待数据包的到来,根据数据包的类型,如果是异步数据包则进行相应的处理;如果是等时数据包则进行等时信道和带宽的申请,申请成功后则配置DMA寄存器以DMA方式进行等时数据的发送或等时数据的接收,等时数据传输完毕后释放其信道和带宽,这样完成一次数据的传输,接下来进行下一次数据的传输,如此循环完成整个数据的传输。

5 结束语

IEEE 1394b作为一种与平台无关的技术,可以同时应用在MAC和PC中,本文研究的主要内容是利用FPGA、DSP和PCI9054芯片实现1394b数据传输系统。现在国内基本上还停留在1394或1394a总线数据的传输上,本系统是在前人的基础上,实现1394b总线上的数据传输,同时本系统兼容1394a实现1394的传输,还可以将传输速率提高作为验证1394b协议的通用平台,1394b能提供800 Mb/s或更高的传输速度,虽然市面上还没有1394b接口的光储产品出现,但相信在不久之后也必然会出现在用户眼前,无论是在视频传输还是在计算机外设、网络互连等方而,都将有广阔的市场。

-

基于FPGA和DSP的1394b双向数据传输系统2012-05-14 0

-

基于FPGA的高速LVDS数据传输2014-03-01 0

-

无线数据传输模块的实际应用2019-06-18 0

-

USART数据传输模型怎么理解2020-04-23 0

-

如何实现基于1394b接口的车载嵌入式图像实时采集与显示系统设计?2021-12-27 0

-

DMA进行数据传输和CPU进行数据传输的疑问2023-05-25 0

-

数据传输的通信系统设计2009-06-13 488

-

基于消息中间件的农电数据传输系统2009-08-18 505

-

1394的传输速率是多少?2009-04-14 3720

-

Modem数据传输标准2009-12-28 921

-

什么是U盘的数据传输率2010-01-30 628

-

数据传输速率是什么意思2010-03-18 4940

-

数据传输中的成帧2010-03-18 3671

-

PIS车地无线双向数据传输方案设计2016-12-27 943

-

采用NIOSII处理器实现IEEE-1394b双向通信数据传输设计2019-01-08 1817

全部0条评论

快来发表一下你的评论吧 !