谈谈集成电路ESD保护的器件和电路

描述

各位群友,大家晚上好,我是黄晓宗,一直从事模拟和混合信号IC设计工作,对ESD保护设计有一定的心得,今天和大家谈谈集成电路ESD保护的器件和电路,在交流的过程中会分享一些实际的案例,希望能够为大家做一些基础知识的铺垫,也感谢大家在这里进行交流。

我将分为以下部分介绍,在完成背景介绍后,将在第二、三和四章针对基本器件、二极管、SCR器件提高维持电压的技术进行讨论。然后,通过工程案例和器件应用,分析和优化全芯片ESD保护设计;第五章将讨论SiP ESD中板级和片上协同保护的策略,提高系统的保护能力。

静电放电现象在日常生活中非常常见,干燥的冬天手指触碰到金属门把手,就会发生放电现象。不同物体的接触和分离就是最常见的静电产生方式,例如摩擦可产生静电。人体有感觉的静电放电电压在3000—5000V,这些静电对人体并不是致命的,但是对没有静电防护的电子产品来说可能会造成非常严重的后果。

电子产品离不开芯片,也就离不开ESD保护设计。以我们的手机为例,移动电话转向智能电话技术,智能手机按键被触摸技术替代,取消了按键接口,人机交互通过触摸屏完成。虽然目前的智能手机仍有耳机、电源充电、电源按键等端口外露,但是已经大大减少。对于未来发展,当“非接触技术”(类似手势控制)替代目前的“接触技术”,那么直接的人机交互将减少静电损伤的风险。芯片在生产、封装、测试、组装等过程中都受到ESD的威胁,所以保护设计也就贯穿整个芯片的始终。这是典型的ESD失效照片。

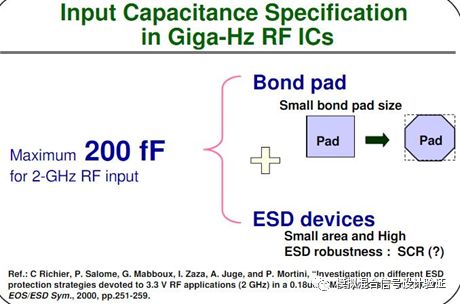

一般来讲,一颗芯片上都会有相应的ESD保护电路,其目标就是泄放电流和钳位电压,保护脆弱的内部电路。当然,RF电路为了性能的考虑,可能无ESD保护结构,其静电能力就可能200V-250V。

ESD对IC的损伤主要有两类,即大电流产生局部热量、高电场损伤绝缘层,都会导致电路或者器件功能性能的异常。ESD保护的基本原理就是并联保护器件,以此泄放大电流和钳位高电压,避免对内部电路造成损伤。

保护的原理已经非常清楚,那么在具体实施过程中,一种方式是减少静电的产生,例如静电手套、指套、离子风扇等中和静电,这样就减少了芯片受到的ESD威胁;另一种就是让自身变得更加强大,既然无法避免强大静电的产生,那么尽可能增强自身的抗ESD冲击能力,这可以通过系统级和片上保护来实现。

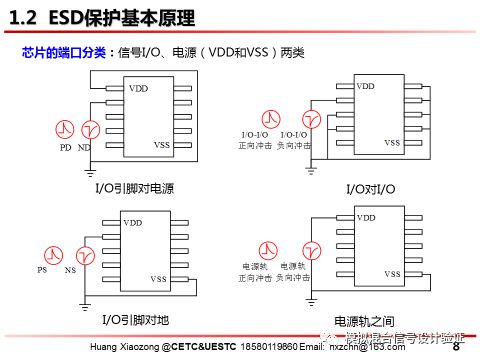

分析完这些ESD现象和保护原理,那么如何来评价一颗芯片的ESD能力呢?我们通常将芯片的引脚分为信号I/O、电源(VDD和VSS)两类。这些引脚可以形成不同的冲击组合,即PD/ND、PS/NS、I/O-I/O和电源轨之间进行ESD冲击,便于研究。

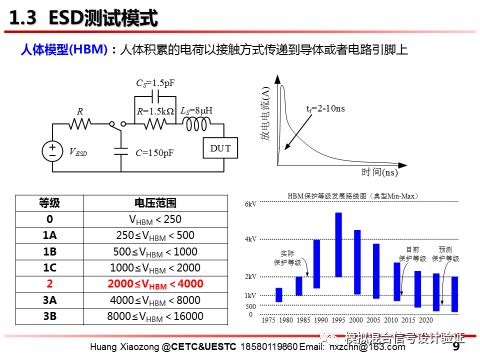

为了模拟芯片在不同场景下受到的ESD冲击,建立了一系列标准的、可重复的ESD脉冲,对待测试器件进行冲击。例如模拟人体积累电荷对器件放电的人体模型,这是最常用的一种模式。通常IC的HBM ESD能力都要求2000V以上,但是对于敏感电路,例如RFIC、超高速的信号端口等,ESD能力要求会降低。

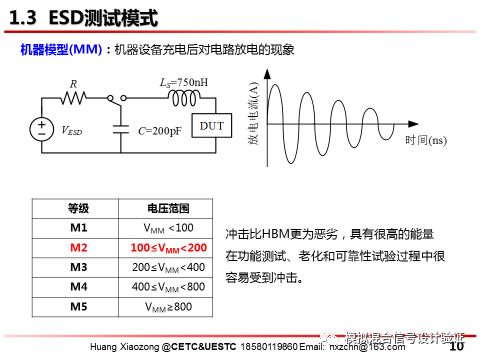

模拟充电金属机械手对器件冲击的机器模型,冲击能量比HBM更加恶劣。

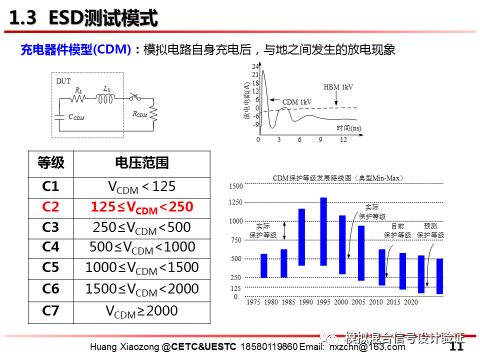

模拟器件自身充电,并对地放电的充电器件模型。CDM模式与HBM/MM模式显著的不同在于电荷产生的方式,CDM是由器件自身积累电荷,而通过引脚泄放到地,形成冲击电流,从而可能对电路造成损伤;HBM/MM则是外部(无论是人体还是机器)的电荷对电路造成损伤。

这些模型都是对独立芯片或者器件的ESD冲击。

当器件装配到系统中,仍需要对系统的ESD性能进行评价,那么就是通过电子枪对系统进行冲击的IEC系统级测试。然而,这些测试都只能对芯片的等级进行判定,并不能对器件特性进行表征,那么TLP测试模式就被引入了。

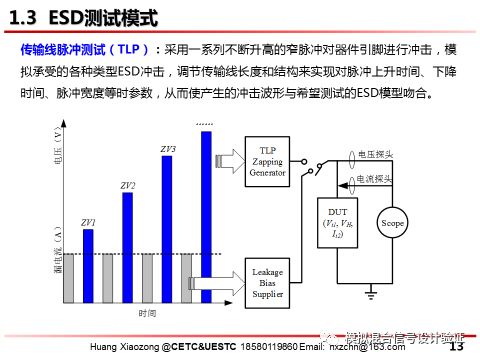

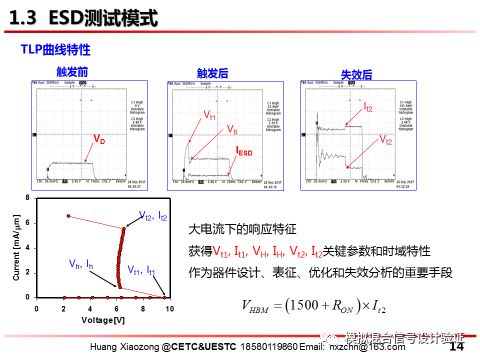

TLP是常用的分析手段,通过一系列窄脉冲对引脚进行冲击,并且可以调节时间参数,模拟不同冲击下的行为。

通过时域波形提取每次冲击下的电压、电流,并监测漏电流变化,从而获取关键参数,作为器件设计和优化的重要手段。

目前已有大量的TLP商用设备,我的研究主要基于Hanwa的TLP设备。TLP可以表征HBM/MM的等效特征,快速TLP(VeryFast TLP,vfTLP)通过调节传输线长度和结构实现了CDM冲击等效特征的模拟,产生脉冲宽度1ns-5ns,上升时间0.1ns-0.4ns,如此短暂的时间小于硅材料中热扩散时间常数,可以较好评估器件和电路在快速放电状态下的行为,但是因为vfTLP和CDM的电流泄放路径通常存在差异,所以并不能预测器件和电路的失效阈值。

下面我们对ESD基本保护器件的特性进行简单分析。

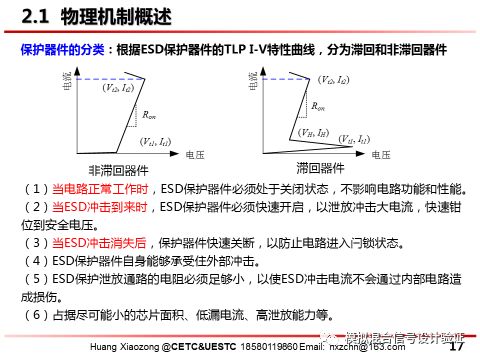

ESD保护器件主要有滞回和非滞回两类,都需要满足以下条件:

(1)当电路正常工作时,ESD保护器件必须处于关闭状态,不影响电路功能和性能。

(2)当ESD冲击到来时,ESD保护器件必须快速开启,以泄放冲击大电流,快速钳位到安全电压。

(3)当ESD冲击消失后,保护器件快速关断,以防止电路进入闩锁状态。

ESD保护器件就像一位优秀而强健的保镖,当有危险到来时,及时现身保护主人,当危险消失后,保镖也就默默地走到一旁。

(4)ESD保护器件自身能够承受住外部冲击。

(5)ESD保护泄放通路的电阻必须足够小,以使ESD冲击电流不会通过内部电路造成损伤。

(6)占据尽可能小的芯片面积、低漏电流、高泄放能力等。

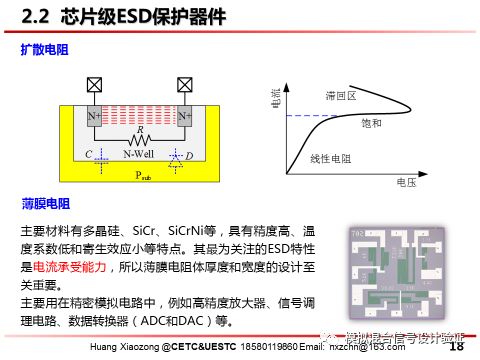

电阻在ESD保护中起到辅助作用,具有不同的行为特性。扩散电阻在冲击下具有饱和特性,这是因为半导体材料的电阻率是由载流子迁移率和浓度决定,当电场强度使得载流子迁移率饱和后,电阻率只与浓度相关,所以出现饱和特性;当电压进一步增大时,出现碰撞电离,雪崩产生大量载流子,从而出现滞回区。薄膜电阻则重点关注电流承受能力,后面将有所涉及。

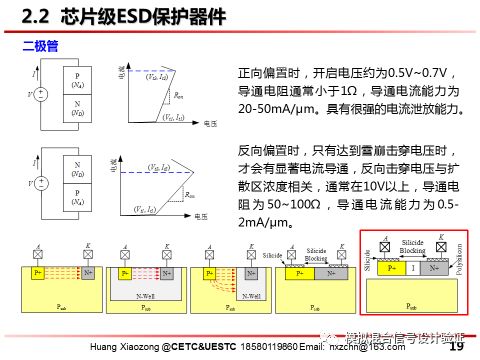

正向导通二极管具有很强的泄放能力,是重要的保护器件,在射频、数字端口保护中常用。但是反向二极管电流能力弱,若作为ESD保护,需要较大的芯片面积。

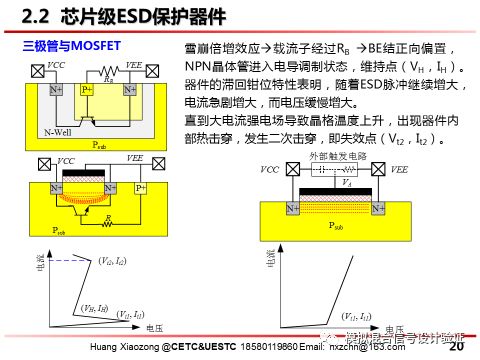

三极管和GGNMOS在反偏结击穿后,整体器件进入电导调制的滞回状态,形成S形滞回曲线,泄放电流。MOS管的栅极还可通过RC触发实现动态的沟道电流泄放能力。

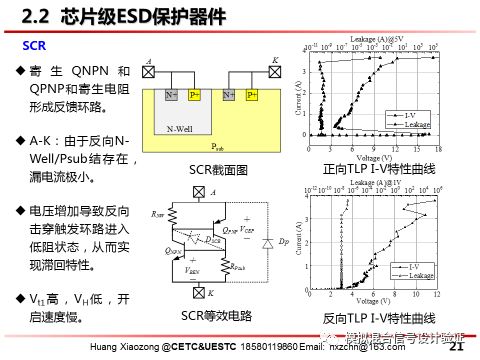

SCR是重要的ESD保护器件,通过PNPN结构形成反馈环路,这是典型的特性曲线,具有Vt1高,VH低,开启速度慢的特点。注意对于SCR来说,反向特性虽然也是一个二极管,但是串联了Rpsub和RNW,会影响导通电阻,直接影响钳位特性和导通电阻,所以通常并联一个Dp。第四章将针对其维持电压进行优化设计。

下面我们来讨论一下二极管在ESD保护中的应用及其优化设计的一些研究。

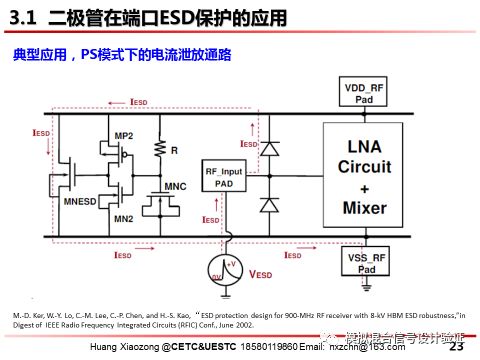

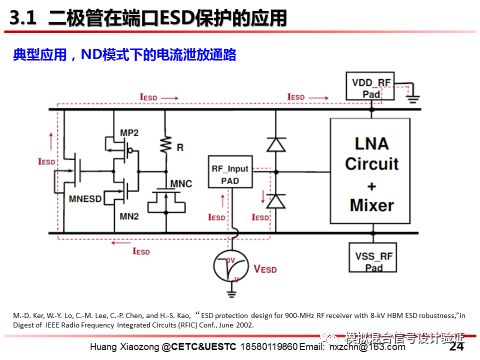

我们首先重温一下刚才讨论到二极管的情况,正向导通ESD保护能力强,开启电压低;每一个端口都有对电源轨、其他端口的ESD冲击模式。这里针对实际电路说明泄放通路。PS:反向二极管不易导通,那么正向二极管与电源轨之间的保护形成通道。

这是ND模式,对电源进行负压冲击,也有类似的电流泄放通路。

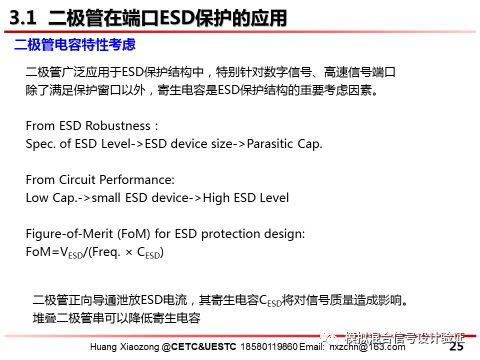

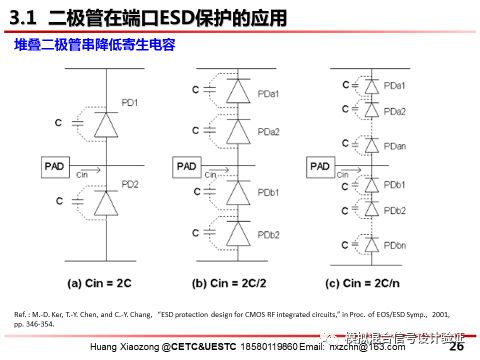

二极管结构简单,易于使用,广泛应用于ESD保护结构中,特别针对数字信号、高速信号端口。除了满足保护窗口以外,寄生电容是ESD保护结构的重要考虑因素。这里主要针对堆叠器件做一个说明。

可以看出,串联二极管的寄生电容随着串联数量增加而成比例减小,这对于高速信号端口来说是极其重要的特性,但是串联数量越多,也会导致其开启电压越高,导通电阻越大,会影响ESD保护性能。

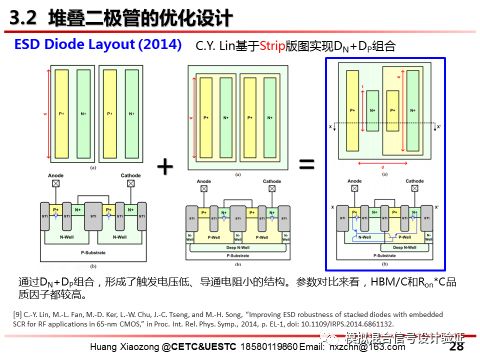

这是一个常规二极管的Layout,下面将针对堆叠二极管的版图优化进行介绍,说明Layout对ESD能力的影响。

我们通常看到的二极管就是两个相同二极管的堆叠,例如P+/Nwell或者N+/Pwell,但是只要将两种器件混合,就会出现新的机理,如右图的结构,形成了PNPN的SCR通路,而触发则是由二极管实现,具有低触发电压的特点。

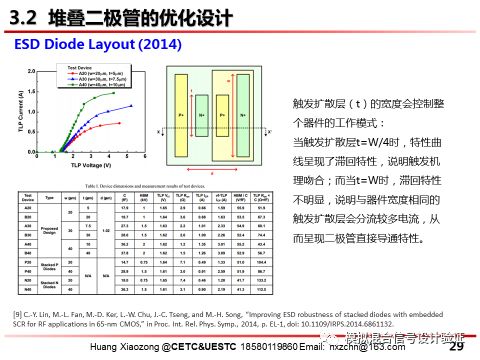

从测试的TLP特性可以看出,触发扩散层(t)的宽度会控制整个器件的工作模式:当触发扩散层t=W/4时,特性曲线呈现了滞回特性,这与SCR触发机理吻合,当t较小时,串联二极管上分流电流较少,剩余的电流将触发寄生的SCR通路;而当t=W时,滞回特性不明显,说明与器件宽度相同的触发扩散层会分流较多电流,从而呈现二极管直接导通特性。

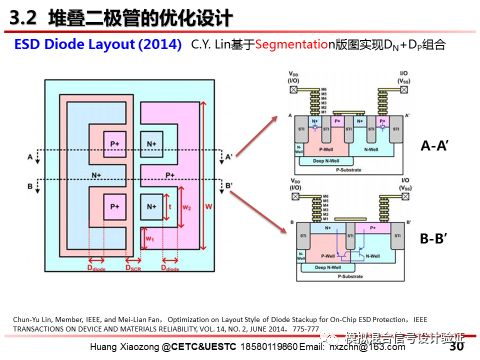

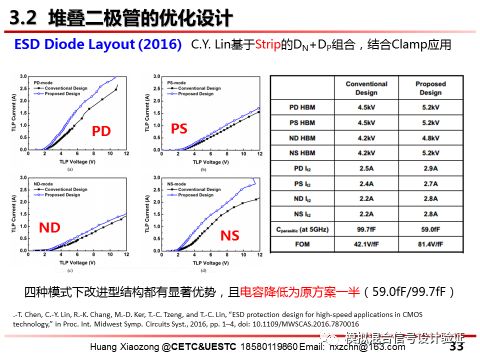

在同一年,该研究对版图进行优化,利用分割的方式实现了Dn+Dp的组合,从AA’和BB’截面可以看出,该器件具有两种路径,一种是串联的二极管,另一种是SCR通路。

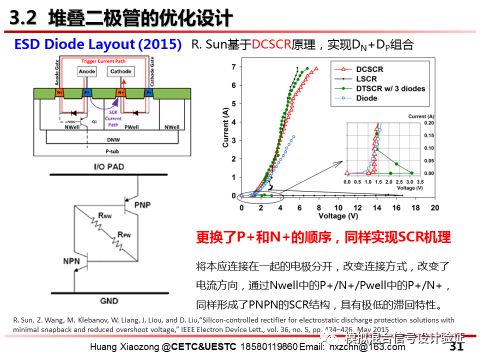

2015年这个结构将本应连接在一起的电极分开,改变连接方式,改变了电流方向,通过Nwell中的P+/N+/Pwell中的P+/N+,同样形成了PNPN的SCR结构,具有极低的滞回特性。

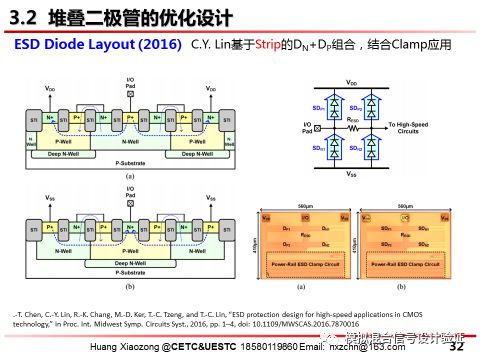

这里将前面的版图优化结构进行了工程应用,配合Power Clamp实现电路的保护,并对全芯片保护的特性进行了分析。

可以看出,在不同的冲击模式下,和传统的堆叠器件(传统器件就是2Dn或者2Dp)相比都有显著优势,ESD性能更高,电容降低为原方案一半(59.0fF/99.7fF)。

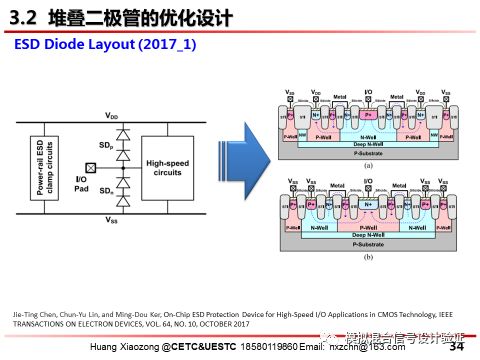

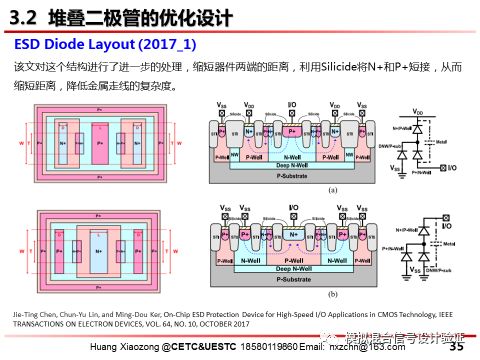

该研究对Dn+Dp的串联形式进行了进一步的优化,利用Silicide将N+和P+短接,从而缩短器件两端的距离,降低金属走线的复杂度。

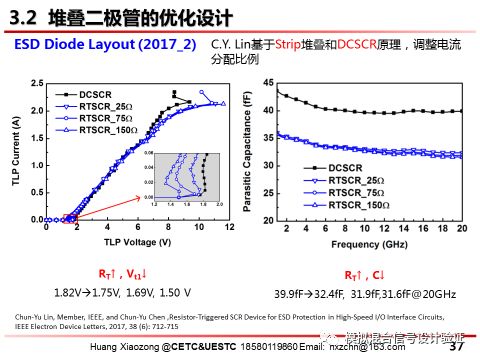

针对DCSCR,从A-K(Cathode-Anode),有PN二极管和P+/Nw/Pw/N+形成的SCR,二极管优先导通,并触发SCR通路,从Nw流出的电流,本质上开启了寄生的PNP晶体管(Nw是PNP的基极);进入Pw的电流,本质上开启了寄生的NPN晶体管(Pw是NPN的基极),实现更强的电流泄放能力,当然,这里的特性与二极管非常相似。

通过不同电阻值的对比测试可以看出,当串联电阻增大时,触发电压Vt1降低。在论文中对寄生电容进行了近似分析,其电容值也随着串联电阻的增大而减小。

SCR是重要的ESD保护器件,也是ESD研究领域的重要课题,这里简要介绍采用分割方式提高维持电压的技术。

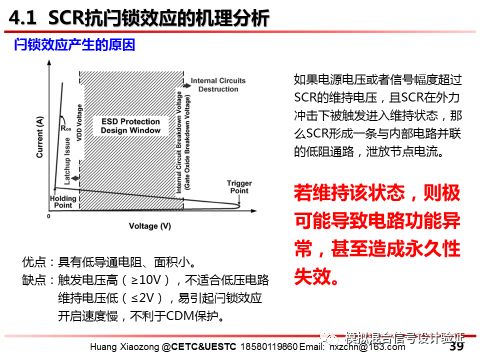

前面已提到,SCR具有低维持电压的特点。如果电源电压或者信号幅度超过SCR的维持电压,且SCR在外力冲击下被触发进入维持状态,那么SCR形成一条与内部电路并联的低阻通路,泄放节点电流。若维持该状态,则极可能导致电路功能异常,甚至造成永久性失效。

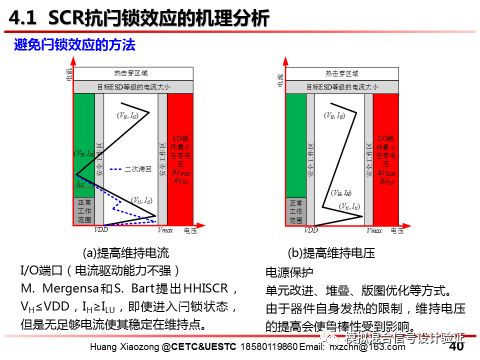

避免闩锁效应的方法之一,是提高维持电流到闩锁电流之上,这对电流驱动能力不强的I/O端口来说比较实用。但对于电源之间的保护,提高维持电压是更好的方式,业界已研究多种方式,但是鲁棒性会受到影响。M. Mergensa和S. Bart等通过增加外部并联电阻和版图优化提高维持电流,形成高维持电流SCR(High Holding Current SCR,HHISCR),当维持电压VH≤VDD,但是IH≥ILU,即使进入闩锁状态,因为无足够电流使其稳定在维持点,可使电路脱离闩锁状态。

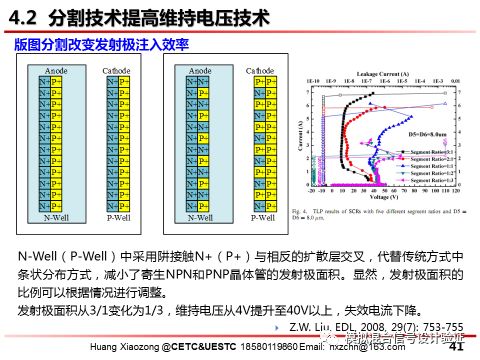

首先是通过版图分割技术,利用扩散层交叉的方式替代条状分布方式,调节发射极注入效率,可实现维持电压提升,但是由于发射极面积减小,失效电流下降显著,大家可以参考相应的文献。

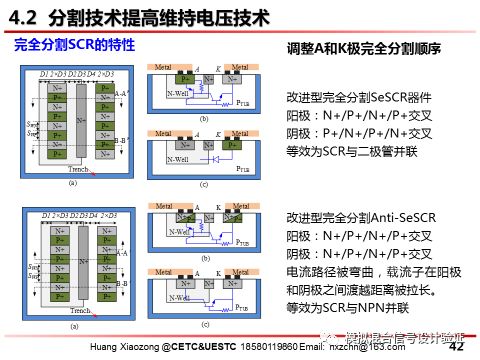

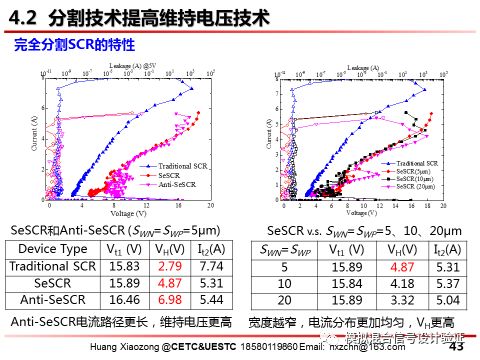

完全分割技术在单向SCR中可以进一步探讨,调整阴极和阳极的分割顺序,命名为SeSCR(阳极:N+/P+/N+/P+交叉、阴极:P+/N+/P+/N+交叉,等效为SCR与二极管并联)和Anti-SeSCR(阳极:N+/P+/N+/P+交叉、阴极:N+/P+/N+/P+交叉;电流路径被弯曲,载流子在阳极和阴极之间渡越距离被拉长。等效为SCR与NPN并联)。

Anti-SeSCR电流路径更长,维持电压可达到接近7V,SeSCR分割宽度越窄,电流分布更加均匀,所以VH更高。

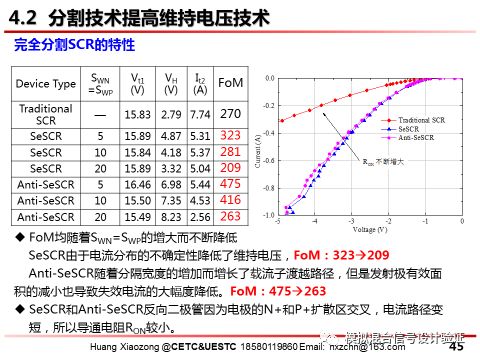

Anti-SeSCR随着分割宽度增加,维持电压显著增加,这是因为空穴向阴极N+扩展,不断复合,浓度降低,且随着∠α越大,载流子浓度越低,有效的发射极宽度为SWN_eff减小。同时伴随载流子渡越距离变长,维持电压就随之提高。

但是有效发射极面积减小,导致电流聚集效应显著,It2下降。

这里定义了品质因子FoM(VH×It2/Width),FoM均随着SWN=SWP的增大而不断降低。因为完全分割结构,使得反向二极管的电流路径变短,导通电阻RON更小。

上面的内容都是介绍独立器件的设计,单纯器件的特性并不一定能够满足全芯片ESD保护的要求,必须匹配相应的保护窗口。下面将对全芯片ESD保护设计技术进行案例说明。

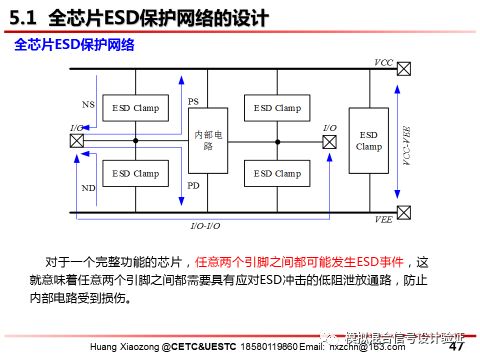

对于一个完整功能的芯片,任意两个引脚之间都可能发生ESD事件,需要相应的泄放通路。图中表示了各种冲击下的电流泄放路径。

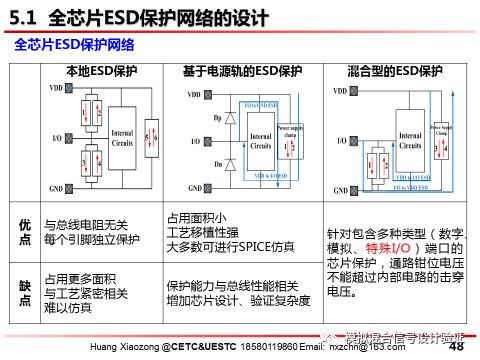

全芯片ESD保护网络通常可以分为以上三种情况,各有优缺点。针对引脚数量少的模拟电路,可以选用本地ESD保护网络,不需要借助总线,每个引脚均可独立实现保护;基于电源轨的ESD保护具有占用面积小,工艺移植性强的优点,但是增加了芯片设计和验证的复杂度;混合型ESD保护网络主要面向多种类型端口的芯片,例如带有RS485接口的混合信号IC。

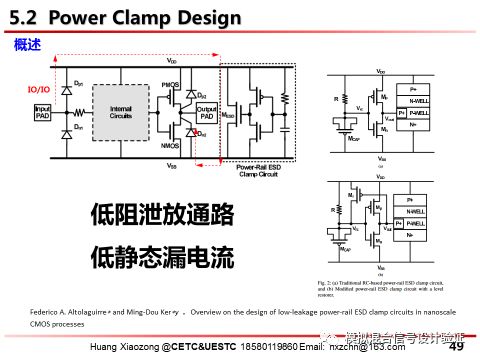

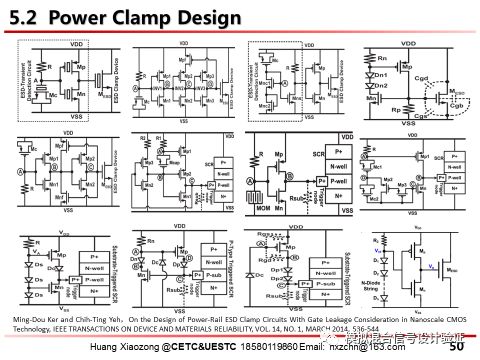

这里说明了PowerClamp在保护网络中的应用,对于基于电源轨的保护策略来说,Power Clamp的性能极其重要,需要具备低阻泄放通路、低静态漏电流等特点。这里仅对一些典型结构进行列举。

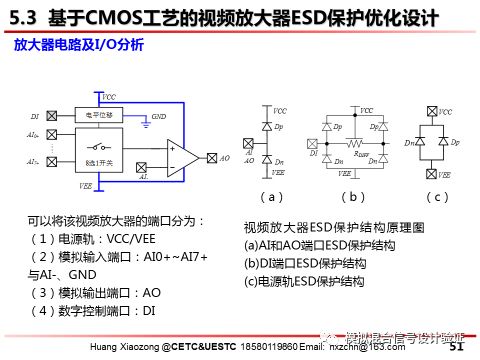

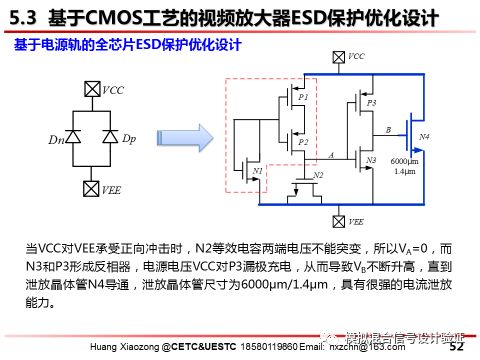

这里以一个基于CMOS工艺的视频放大器ESD保护优化设计的案例,说明基于电源轨的保护策略,如何通过优化PowerClamp达到提升整体ESD能力的目的。

原保护方案采用了左图反向二极管的方式,在ESD测试过程中,出现输出端损伤的情况。经过电参数测试和失效分析,确定了ESD损伤机理。更改为右图的有源泄放结构可以很好实现电流泄放。下面通过TLP对比测试来说明。

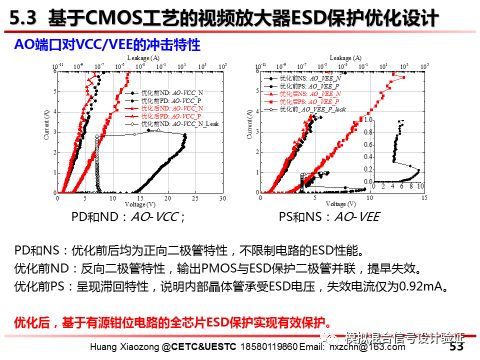

从测试曲线可以看出,PD和NS在优化前后均为正向二极管特性,不限制电路的ESD性能。优化前ND:反向二极管特性,输出PMOS与ESD保护二极管并联,提早失效。优化前PS:呈现滞回特性,说明内部晶体管承受ESD电压,失效电流仅为0.92mA。优化后,基于有源钳位电路的全芯片ESD保护实现有效保护。

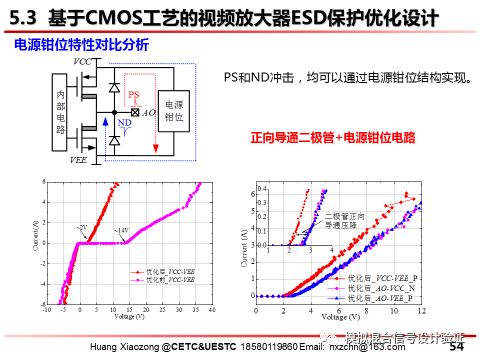

这一页的测试结果验证了有源泄放的Power Clamp作为公共总线泄放PS和ND的ESD冲击特性,PS和ND的特性均为一个正向导通二极管+电源钳位电路的I-V特性叠加,达到了提升全芯片ESD保护能力的目的。

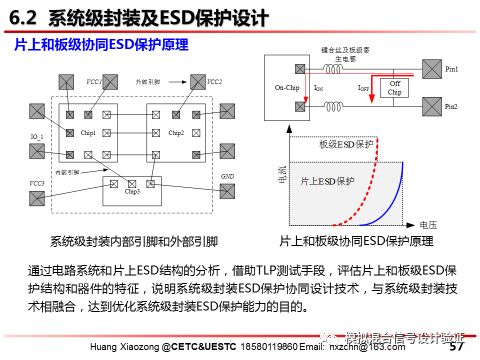

在全芯片ESD保护的基础上,我们对系统级封装的ESD保护进行了一定研究,说明片上和板级的协同保护策略。

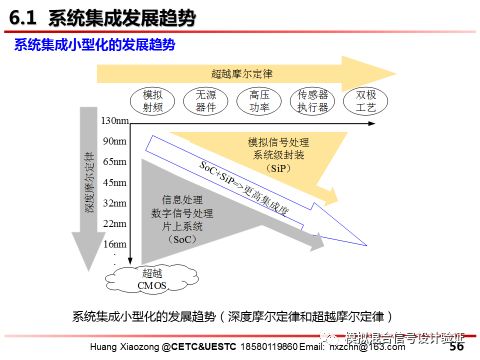

众所周知,集成电路的小型化发展沿着More Moore和More than Moore两个趋势发展,而随着More Moore对于成本要求不断提高,More than Moore成了重要的解决方案,通过不以小尺寸为目标的特种工艺设计模拟、射频和功率器件,通过SiP技术将不同功能的电路、甚至MEMS等传感器进行系统级封装,实现解决方案的小型化。

对于系统级封装的ESD保护,首先要区分封装内部引脚和外部引脚,通过电路系统和片上ESD结构的分析,借助TLP测试手段,评估片上和板级ESD保护结构和器件的特征,说明系统级封装ESD保护协同设计技术,与系统级封装技术相融合,达到优化系统级封装ESD保护能力的目的。

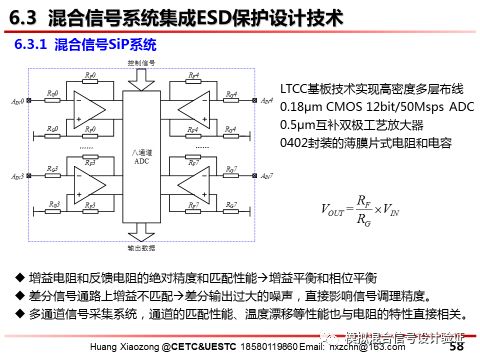

这是一个混合集成的多通道ADC产品,利用LTCC基板实现多层高密度布线,集成了不同工艺实现的芯片和若干电容和电阻,根据性能要求选择了低温度系数、高精度的薄膜电阻作为增益电阻。

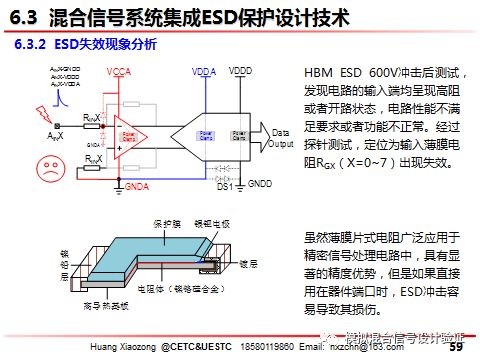

HBM ESD600V冲击后测试,发现电路的输入端均呈现高阻或者开路状态,电路性能不满足要求或者功能不正常。经过探针测试,定位为输入薄膜电阻RGX(X=0~7)出现失效。我们对端口的薄膜电阻进行了分析,其结构采用了镍铬硅合金作为电阻体,具有精度优势,但是其抗ESD冲击的能力较弱。

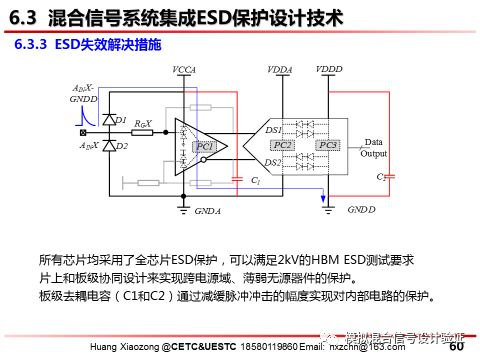

在板上增加D1和D2二极管,配合芯片的Power Clamp,泄放端口冲击的ESD电流,片上和板级协同设计来实现跨电源域、薄弱无源器件的保护。板级去耦电容(C1和C2)通过减缓脉冲冲击的幅度实现对内部电路的保护,优化后的方案可达到2000V以上。

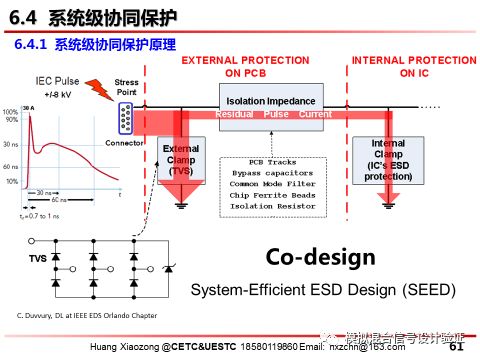

这就说明了片上和板级协同保护的基本原理,利用板级器件泄放主要的冲击电流,而片上的保护结构仅承受少量的残余冲击电流即可,从而保护端口不受损伤。

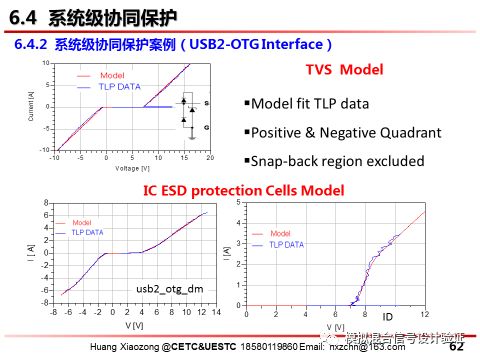

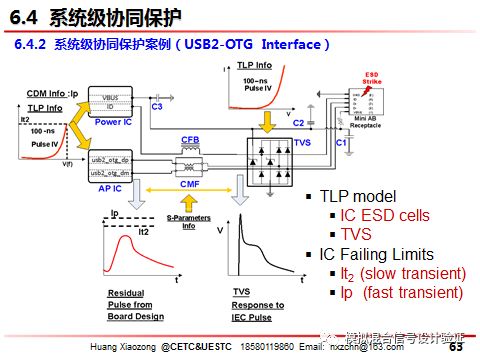

这里说明一个USB2-OTG接口的保护案例,首先要对备选的TVS器件和被保护芯片进行TLP分析和建模,确保两者的特性匹配,板级保护要优于片上保护,且优先开启。

这里说明了最终的保护原理图,利用了CMF、CFB、TVS等多种器件实现对芯片的保护,使其在热插拔等恶劣条件下具有充分的鲁棒性。

最终的方案可以看出,为了保护一颗芯片,板级采用了多种类型的保护器件来实现,这就是大批量、高可靠性产品需要的ESD保护设计。

这里展示了ADI公司的一款典型产品,采用了协同保护的理念对MEMS Switch进行了性能优化。MEMS靠静电力驱动,但是同时也要防止RF端口被静电损伤,间隙火花放电现象是主要的ESD事件。

通过在系统级封装中增加ESD外部器件,使得静电敏感的MEMS器件不受损伤,从而实现了高性能和高可靠性的创新产品。

感谢各位群友的聆听和交流,如果有不正确或者不全面的,欢迎大家批评指正,谢谢。

问答互动

模*:您说的薄膜电阻是Thin Film Resisitor么?我查了一下,好像ESD能力确实比较差,如果做在片内,并且做在输入端,这样还有办法提

高ESD能力么?

Answer:Thin Film Resisitor ESD能力比较低,在设计方面主要通过优化电阻的Layout上来实现。可以在电阻网络上增加ESD保护二极管,这都是在定制电阻网络的情况下可以实现的。刚才报告里面采用的是分立0402电阻,但是通常的电阻网络芯片可以定制,ESD能力取决于版图宽度和薄膜层厚度,需要工艺厂家一起协作。

模*:芯片都有ESD保护电路,这样Thin Film Resisitor是否在输入端或者哪里,是否应该不会受到ESD影响?如果有影响运放输入管的栅就很容易损坏了。

Answer:Thin Film Resistor在端口才会受到ESD冲击的损伤,内部就不用考虑其直接的ESD损伤,但是也要注意,如果该电阻在ESD电流的泄放通路上,也要考虑其承受电流的能力。

陈*:谢谢分享!,请问有低漏电的ESD结构么?

Answer:一般来讲,SCR和反向二极管的漏电都比较低,如果采用RC Clamp作为电源钳位,也有很多结构,那一页PPT里面可参考相应文献。

风*:ESD性能可以拿器件进行Spice 或者Spectre仿真吗(这样的仿真准确吗)?还是要进行专门的建模呢?特别是SCR这种ESD器件。这个应该可以仿真,但是我不会看,之前见过别人仿真,但是我实在看不出来,仿真(5v)和实际如何对比。

Answer:Modeling是个重要的课题,有不少人研究,可以用VerilogA写;SCR需要专门建模,通用器件在大电流下特性也会变化。ESD如果建模就可以跟电路一起仿真,但是我不太熟悉;ESD器件设计时通常会使用TCAD等EDA做器件特性仿真,预测特性。通用器件的spice仿真有意义,例如二极管、RC Clamp。

松*:CDM保护的一般结构和HBM有什么异同吗?

Answer:CDM放电速度远快于HBM,其脉冲上升时间<400ps,而HBM的上升时间约为10ns,并且CDM模式和封装尺寸有关,保护结构需要快速开启,需要速度快的结构。

孙*:ESD泄放电流都是A级别的瞬态电流。Metal的线宽除了满足走线电阻足够小的需求,Current Density一般按照什么标准考虑?比如拿泄放电流的5%,10%当DC Current算最小Width,有没有个经验值?

Answer:CurrentDensity有文献([2010Ebook]_A.Vashchenko_ESD Design for Analog Circuits)给出DC电流40X经验值的说法,可以参考。

高*:端口钳位电压怎么考虑?

Answer:钳位电压保证不超过端口器件的击穿电压,同时高于信号电压或者电源电压(避免闩锁,也可以提高ESD器件的维持电流来实现)

IC*:高压60V的ESD如何做…一般Vhold都低

Answer:高压要参考ESD Window,高Vhold SCR有不少方案,例如发射极分割,用低维持电压堆叠等,例如两个30V或者三个20V。

泽*:您刚才说钳位电压不超过击穿电压,ESD这种瞬时击穿电压,是不是会比直流击穿电压大一些,有这种区分吗?

Answer:钳位电压不超过器件本身的击穿电压,ESD保护的作用就是把瞬时冲击电压压缩到安全范围。

冰*:有Vhold能堆叠,但是Vtrigger不怎么增加的技术吗?目前高Vhold ESD主流用的都是发射极分割的SCR吗?请问能高到多少V?面积多大呢?

Answer:有结构可以增加Vhold,但是维持Vtrigger不变的研究,通过外部触发的机制,同时触发堆叠的单元。参考”FeiMa, Bin Zhang and Yan Han, High Holding Voltage SCR-LDMOS Stacking StructureWith Ring-Resistance-Triggered Technique IEEE Electron Device Letters, 34(9),2013”。当然也有其他的实现方式。发射极分割的结构本身不增加版图面积,与传统结构相当。如果需要更大的维持电压,那么会导致单位面积上失效电流减小,需要增加版图面积提高保护能力。

Q*:做的高速的ESD可以用网络分析仪或者时域反射计量电容啊

Answer:这方面我没有看到太多工程应用的案例,仅在有的项目中做过应用。

凯*:请教个问题,在BUCK电路中,仿真时,强驱动下开关过程会产生ns级超过器件耐压的毛刺;但测试过程中,从未发现芯片有因此器件失效的现象,是因为毛刺从Clamp泄放掉还是短时毛刺器件不会损伤呢,Clamp使用GRNMOS。上管是p管,ESD2000V是pass的,器件用的5V,仿真最大有8V。

冰*:上管如果是PMOS不一定会死,PMOS没有Snapback特性,不过ESD倒很可能挂。应该是没超过Vtrigger吧。5V器件BV一般有11V以上的,没到trigger点。

Answer:仿真提示超耐压应该是指超了PDK提供的耐压,但是是不是器件真实的耐压不确定,击穿通常有一定的余量。要结合电路结构来分析,最好查foundry的PCM数据。

Q*:高速IO的ESD,如果想做8k HBM,你们能做成的ESD的寄生电容最小能达到多少?300fF?200fF?用于10Gbps的传输。

Answer:很抱歉我没有专门做这种器件,主要还是串联二极管,有文献说明针对2GHz的高频端口,可承受的最大寄生电容是200fF。

-

集成电路TVS保护电路图2009-06-08 506

-

集成电路继电保护(基本电路,距离保护,高频保护,发电机失磁保护,接地保护)2008-08-14 0

-

新型互补电容耦合ESD保护电路的设计2009-12-23 0

-

电子元器件基础:集成电路应用电路识图方法2015-08-20 0

-

如何设计ESD保护电路?2019-08-07 0

-

在I/O电路中ESD保护结构的设计要求2021-04-02 0

-

如何进行双极型集成电路的ESD保护?2021-04-07 0

-

如何设计MOS集成电路ESD保护模块?2021-04-12 0

-

双极型集成电路的ESD保护2009-04-27 449

-

ESD引起集成电路损坏原理模式及实例2012-03-27 10975

-

全面了解cmos电路中esd保护结构原理及应用2017-12-05 12156

-

影响 ESD 保护要求的集成电路趋势2022-11-14 206

-

HFTA-16.0:双极型集成电路的ESD保护2023-06-10 606

-

集成电路的核心是什么?集成电路有哪些器件?2023-08-29 2289

-

集成电路芯片的基本概念 集成电路材料与器件 集成电路介绍2023-08-29 2226

全部0条评论

快来发表一下你的评论吧 !