计算机并口EPP模式及基于XC95144芯片实现它的通信设计

描述

前言

计算机的并行接口一开始是作为打印机接口而设计的。随着计算机周边设备的不断扩展,人们对提高计算机外设的数据采集速度的要求也越来越高。传统的异步串行通讯方式虽然具有数据传输距离较远的优势,但是由于数据传输速度慢,会造成传输速率的瓶颈问题。所以在一些需要高速数据传输的场合,使用并行接口一直是一种比较理想的解决方法。

1、并口EPP模式介绍

1.1并行接口的种类

最初的PC机并口由8个单向输出,5个位输入和4位双向(控制)线组成(SPP),如今为了适应扩展外围设备的需要,并口已经发展出了多种工作模式。总共有标准并行接口(SPP)、简单双向接口(PS/2)、增强型并行接口(EPP)和扩展功能接口(ECP)模式和多模式接口(ECP+EPP)这几种。EPP工作模式作为一个提供高性能并口连接的方法,仍与SPP兼容。EPP工作模式的优点概括如下:

1)8位数据线由原来SPP的单向改成了双向,简化了外围电路的设计;

2)在一个ISA的周期可以完成一次数据的传输,大大加快了数据传输速率;

3)只需要对计算机发送一条简单软件指令,接口硬件就可以自动生成握手联络信号;

4)接口数据线可以分别定义为数据和地址,通过综合使用nAstrb和nDstrb两条控制线可以快速的实现数据向不同的设备传输;

5)相对ECP的工作模式,EPP具有操作简单、易于实现的特点;

1.2 EPP的硬件接口

EPP接口通常是25芯的D-sub接口,符合IEEE1284标准。其中数据选通和地址选通信号为低电平有效, 且两者不可能同时为低, 等待信号(nWait) 为握手信号,主要是考虑PC比外设快, 外设通过发送等待信号与PC并口协调工作。空闲信号线(Spare)可以由外设根据需要来决定其状态,由PC直接读取并口状态寄存器的相应位来获得Spare的状态信息。

1.3 EPP寄存器说明

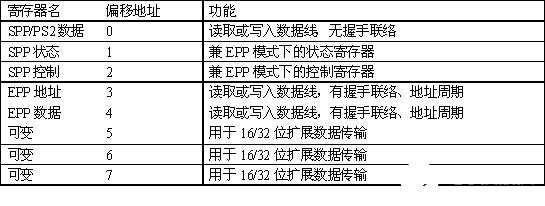

在PC机中,标准并行接口使用了3个8位的端口寄存器。PC就是通过对这些寄存器,也就是通常所说的数据、状态、控制寄存器的读写访问并口信号的,这3个寄存器的地址分别是基地址、基地址+1、基地址+2。如今,EPP将在基地址+3到基地址+7的范围内,添加5个寄存器。所以EPP一共使用了8个寄存器,表1列出了这些寄存器及其功能。

表1 EPP的8个寄存器及他们的功能

为了能够在EPP模式下读写一个数据字节,你需要将数据读取或者写入EPP数据寄存器(基地址+4),而不是读写基地址。同样的,地址的读写也是通过读取或者写入EPP的地址寄存器(基地址+3)来实现的。EPP的基地址通常是378h和278h。

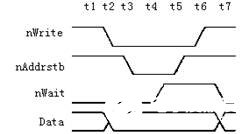

1.4 EPP工作模式的时序分析

在EPP和ECP模式中,简单的端口读写操作就会自动产生握手联络信号,这简化了很多软件上的设计。图1是一个EPP地址写入周期的时序图。如图所示,对EPP数据寄存器的写操作将导致接口启动一个完整的数据写入周期。接口的硬件把待写入数据置于D0~D7,然后接口自动触发握手联络信号,并检测外设的应答。读取一个字节的过程与此类似。同样的,对EPP地址寄存器进行读写操作将引发一个完整的数据读写周期。所以,仔细研究EPP工作状态的时序是非常重要的。

图1 EPP地址写入周期的时序图

2、基于WDM的并口驱动程序的实现

在设计PC机外围产品时,不仅需要考虑PC接口定义,与接口相关的寄存器定义,数据传输协议,还要根据上位机采用的操作系统来编写合适的通讯程序,以便上位机对数据进行管理和监控。早期的Windows98以及更低版本的操作系统,可以直接访问并口硬件资源,比如使用C语言中的inp()和outp()函数来编写简单的通讯程序。但Windows2000/XP的操作系统采用了一些保护措施,阻止对端口的直接访问。这样做虽然提高了系统运行的可靠性,但也增加了软件上实现通讯的难度。

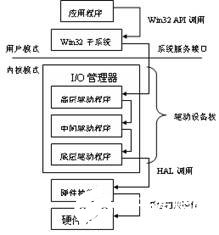

2.1 WDM驱动程序的种类和结构

WDM(Win32 Driver Model),即Windows驱动程序模型,是Microsoft力推的全新驱动程序模式,可以用来开发Windows 98和Windows 2000设备驱动程序。图2显示了在Win2000/XP系统中应用程序调用一个硬件操作的基本过程,从中可以看到WDM在整个驱动体系结构中的位置何作用。

图2 Win2000的驱动体系结构

如图所示,WDM的驱动程序是分层的,一般按照层次分为高层、中间和底层三类。顾名思义,高层驱动程序依赖于中间和底层驱动程序完成工作,而中间驱动程序又依赖于底层驱动程序来完成工作。其中各层驱动程序的详细介绍请参阅参考文献[1]。

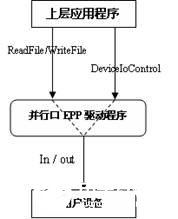

图3 并行口EPP模式驱动程序接口框图

2.2 并口EPP模式驱动程序的功能实现

WDM驱动程序开发工具通常用NuMega DriverStudio。因为它可以集成到VC++ 开发环境中,这样就可以像生成其他工程一样生成驱动程序框架,省去了大量的编写代码的时间。

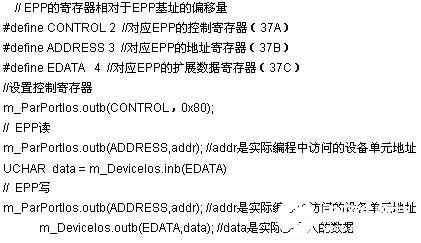

2.3 EPP模式的基本操作

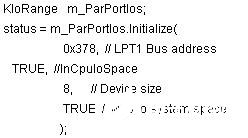

首先定义类KIoRange的一个实例,以对应EPP

下面就可以用类KIoRange的成员函数来访问EPP的寄存器:

3、并口EPP模式外围电路硬件设计实例

由上文可知,并口EPP模式下的数据传输速度可以达到?s级,所以使用一般的单片机来控制外设与EPP的通讯显然不能满足高速的要求。早期,工程师使用大量的逻辑分立元件来设计EPP的外围电路,但是当计算机的主频越来越高,EPP 模式在高速数据传输中可靠性明显下降, 因此本文采用大规模可编程逻辑器件, 充分利用其高速和大容量特性设计接口电路, 不仅可大大提高其可靠性, 且易于系统扩展和升级, 可广泛用于数据采集、D/A 转换以及数字控制。

采用Xilinx公司的XC95144芯片作为EPP接口模块的控制单元,并且通过XC95144实现了计算机并口与外部存储器SRAM的数据交换。在某些外设需要数据存储和与PC机进行数据交换的应用场合得到了成功的应用。该EPP接口模块的总体框架如图4所示。

图4 EPP接口模块逻辑框图

如图4所示,CPLD内部由各个负责不同功能的子模块组成,其作用与早期的分立元件一样,所有子模块用Verilog设计实现,并且通过了仿真验证。采用ECS将所有的子模块组织起来,集成在一块CPLD内。这样做大大提高了整个系统运行的可靠性,同时也为系统扩展其他功能提供条件。

由于SRAM相对DRAM具有存储速度块,无需定时刷新,控制信号简单的优点,所以被广泛的用于需要高速数据处理的小型设备中。图4中的SRAM采用ISSI的IS61C6416,存储容量是64K×16位。地址线和数据线都是16条,但是EPP每次只能传送一个字节的数据,所以CPLD内部需要配置4个8位的数据寄存器,分别保存SRAM的地址和数据总线上的数据。

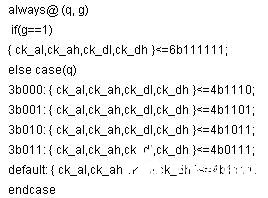

图4中的总线74LS245是一个总线收发器,由nWrite信号控制并口数据的传输方向。74LS138子模块是一个3-8译码器,通过EPP的地址线向138写入数据,使能不同的触发信号(CK)来锁存SRAM的地址或者数据总线上的高/低8位数据。该模块的Verilog核心源码如下:

由此可知,如果希望向SRAM的地址低8位写入数据,PC只需执行outp(0x378+3, 0x00),outp(0x378h+4,地址低8位值) 两条指令,在执行后一条指令的同时,ck_al选通信号将并口的数值锁存到SRAM地址低8位锁存器中。在ck_dh信号触发的同时将由nWE_cre模块使能一个nWE信号,将数据写入SRAM。

4、总结

采用增强型并口(EPP)模式,可以极大地扩展并口通讯的容量和速度。编写针对并口的WDM驱动程序,既可以保证系统运行的可靠性,也可以增加驱动程序的可移植性。使用CPLD设计并口EPP接口模块,可以*限度的体现EPP高速传输的特性,而且由于将所有的功能模块集成在一块芯片中,提高了系统的可靠性,特别是XC95144具有的ISP(在线可编程)技术使复杂的接口电路可根据具体的应用加以修正,大大增强了接口电路的灵活性和可扩展性。本文设计的EPP接口模块已被成功的运用到某款单片机仿真器产品中,实验证明这种设计是可行的。

责任编辑:gt

-

量子计算机或将提前实现2016-06-13 0

-

如何实现计算机与PLC 的通信联网?2021-05-21 0

-

基于WDM的并口驱动程序该如何去实现?2021-06-02 0

-

什么是计算机通信2022-02-17 0

-

计算机串行通信基础2009-12-03 468

-

CH341与EPP并口方式应用2010-01-06 1942

-

基于68HC908GP32单片机实现EPP增强并口的接口技术2010-09-26 1098

-

连接计算机并口的数据采集系统2011-08-29 580

-

XC95144使用组合EDA41说明2016-03-28 633

-

XC95144在系统可编程2017-01-13 690

-

如何实现自由口模式下PLC与计算机的通信方法概述2019-04-17 1510

-

基于Xilinx XC95144和单片机实现数字频率计的设计2020-08-05 1497

-

计算机通信的简单概念2023-05-09 1212

-

计算机通信的特点2023-05-09 708

全部0条评论

快来发表一下你的评论吧 !