将步进电机驱动器集成到CPLD/FPGA中的设计

描述

本设计实例进一步拓展了以前将步进电机驱动器集成到CPLD中的设计。本实例不仅集成了驱动器,而且还集成了一个简单的单轴步进电机运动控制器。根据CPLD大小,可以将多个运动控制器设计到单一设备中。例如,单轴运动控制器采用68%或63%的可用宏单元设计到Xilinx XC95108中。运动控制器以确定的速度与时间曲线顺时针或逆时针旋转步进电机指定的步数。运动开始时,控制器对电机加速,直到其达到巡航速度,然后减速直到停止(图1)。

控制器可将电机速度调节到16 个值,V=VMAX×speed/16, 其中速度值为0到16的整数。在加速阶段,速度从1到16升高,在巡航阶段,速度保持在16,最后,在减速阶段,速度下降到1,直到停止。控制器在达到巡航速度阶段前如果没有足够的步数,控制器可直接从加速阶段进入减速阶段。在程序中利用恒定“加速”功能可以在1到255间调节加速/减速速度。较大值的加速会造成缓慢的加速/减速;低值就会得到较快的加速/减速。该CPLD步进电机驱动器的输入包括时钟、方向、完全/半步长、复位、下一步、启动和停止等。

时钟输入工作在正向时钟脉冲边沿上。最大电机速度为16 个时钟一步。方向输入确定了电机的旋转方向。电机顺时针或逆时针方向运行,取决于该输入的大小和电机的连接方式。该值在开始向高运行后的第一上升时钟边沿锁定。完全步长或半步长输入决定了电机在每个时钟脉冲内的角旋转。在低态时,电机在每个应用的时钟脉冲内执行完全步长,在高态时则需要执行半步长。在复位输入时较大的电流可将电机设定为已定义好的状态。在复位输入较大时,电机可忽略任何时钟脉冲。16位的Nstep值定义了下一运动将要执行的步数。该值在开始向高运行后的第一上升时钟边沿锁定。开始输入较高的电流可启动运动。较大的停止输入电流可停止运动,从而退出当前的运动。

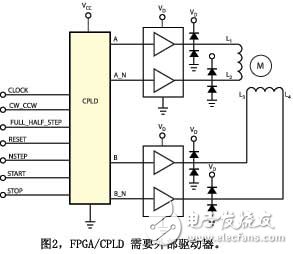

该CPLD步进电机驱动器的输出为A、A_N、B和B_N(图2)。A 和A_N 通过电源驱动器输出控制一个电机线圈,B和B_N输出通过电源驱动器控制电机的第二线圈。

CPLD/FPGA无法直接驱动电机,所以需要外部驱动器。驱动器必须达到电机的额定电压。每个驱动器输出端的肖特基整流二极管允许在电机线圈中的电流续流。如果使用MOSFET驱动器,由于MOSFET有内置的二极管,就不需要外部肖特基整流二极管了。Microchip TC4424A 双驱动器可以驱动电机线圈达到18V和3A。

-

如何利用FPGA实现步进电机正弦波细分驱动器的设计2021-05-06 0

-

如何将步进电机驱动器集成到CPLD/FPGA中的设计2021-05-06 0

-

步进电机驱动器故障分析2023-11-09 0

-

MOTEC 步进电机及驱动器2010-01-09 725

-

基于CPLD的五相步进电机驱动器设计2010-01-14 605

-

基于CPLD的两相步进电机细分驱动器设计2016-04-25 620

-

基于FPGA的两相步进电机细分驱动器设计2016-04-25 591

-

七特步进电机驱动器型号2018-11-21 1525

-

步进电机驱动器调速方法_步进电机驱动器的作用2020-04-20 10168

-

步进电机驱动器有什么参数_步进电机驱动器常见故障维修2020-04-20 15393

-

如何使用FPGA实现步进电机细分驱动器2020-07-24 1179

-

步进电机驱动器原理_步进电机驱动器接线2023-03-08 2799

-

步进电机驱动器拨码2023-03-14 4438

-

步进电机驱动器的主要驱动方式有哪些?2023-11-14 1224

-

步进电机驱动器拨码开关怎么调2024-01-15 1353

全部0条评论

快来发表一下你的评论吧 !