FPGA连线资源的可测性研究及优势分析

描述

1 引言

FPGA的出现大大缩短了集成电路设计的周期,使产品上市的时间大大缩短,并减少了设计成本。FPGA的应用越来越广泛,并且其市场份额也越来越大。但是逐渐扩大的芯片规模和更加复杂的芯片结构,给测试带来了越来越大的困难,测试成本大大增加,如何降低测试成本是很多商家和研究者共同面对的一个问题。有关FPGA测试的研究有很多。

FPGA主要由可编程逻辑资源,可编程连线资源,可编程输入输出资源组成。其中连线资源占芯片面积的60%以上,并且随着器件规模增大,连线也越来越复杂,其出现故障的可能性很大,所以连线资源测试在FPGA测试中扮演了一个很重要的角色。芯片测试包括故障检测、故障诊断和故障冗余。故障检测只检测芯片中有没有故障,如果芯片中有故障就把此芯片扔掉;故障诊断不仅要检测芯片中是否有故障,还要确定故障的位置和类型;而故障冗余是指,对于有故障的芯片采取一定的方法使得芯片可以继续使用,而不至于浪费。可以看到,故障检测是故障诊断的基础,而故障冗余又以故障诊断为前提,在本文的设计中,故障检测及故障诊断都可以支持,只要设计好需要的测试配置就可以了。

对于连线资源测试,出现了很多种方法,大致分为三类:(1)非内建自测试方法(Non—BIST),利用专有的测试仪器对芯片进行配置并加测试向量对芯片进行测试;(2)利用芯片内部可编程逻辑资源对连线资源进行测试,这是内建自测试方法(BIST),在芯片内部通过配置可编程逻辑资源自动产生测试向量,并且对测试结果进行判断。以上两种方法都是利用FPGA的可编程特性对芯片进行测试的;(3)利用可测试设计方便芯片进行测试,通过一定的硬件消耗,在芯片内部加上一定的辅助电路,使得测试比较方便、快速。本文提出的方法属于第三类方法。

与ASIC测试不同,FPGA测试需要将测试需要的配置下载到芯片中,然后加测试向量对芯片进行测试,其测试时间主要由编程下载的时间来决定,所以编程下载时间决定了测试的成本,很多研究者通过减少测试配置数目来减少测试时间,从而降低测试成本。

本文的出发点不是通过减少测试配置数目来减少测试时问,而是从另外一个角度对测试开关盒连线资源时间的减少进行了研究。通过一定的硬件消耗大大减少了编程下载的时间,降低了测试成本。

2 基于SRAM的FPGA结构简介

FPGA通常有三个基本的组成部分,即可编程逻辑单元((Sonfigurable Logic Block,以下简称CLB)、可编程输入输出单元(Input and Output Block,以下简称IOB)及可编程连线资源。通常CLB包含组合逻辑部分和时序逻辑部分,组合逻辑一般包括查询表(Look—up Table)和相关的多路选择器(Multiplexer)。而时序逻辑部分包含触发器(DFF)和一些相关的多路选择器。IOB则提供了FPGA内部和外部的一个接口,连线资源则提供CLB与IOB之间以及各CLB之间的通讯。

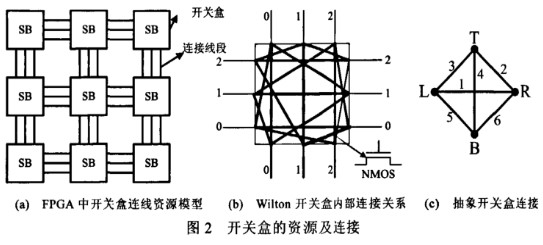

FPGA芯片的基本结构如图1其原因所示,现在的FPGA芯片结构越来越复杂,但都包含这些基本的组成部分。开关盒(Switch Box,以下简称SB)将水平和竖直连线资源进行切换。连接盒(Connection Box,以下简称CB)连接CLB的输入输出到连线资源中。在FPGA芯片中,由于连线资源比较复杂,所以测试花费时间会很长。其中把开关盒抽出来可以构造开关盒资源图,其中包括开关盒内部的可编程开关以及开关盒之间的连接线段,如图2(a)所示。

FPGA开关盒资源模型包括m×m个SB以及相邻的SB之间连接开关盒的k条连接线段,其中SB内部的连接关系如图2(b)所示。其中粗线代表一个NMOS管作为传输管,用来控制线段的连接,传输管的开和闭由编程信息来控制,编程信息存储在SRAM单元中。SB内部有很多传输管,其中两条线段之间有传输管相连的,称为可连接线段,没有传输管的,称为不可连接线段。图2(c)是抽象的开关盒连接关系,其中四个方向分别为T,B,L,R,黑点表示此方向的连接线段的集合,每条连接线段可以另外三条连接线段连接,这三条连接线段分别位于其他三个方向,其中的数字表示传输管的编号。比如3,表示左边的连接线段连接上边的连接线段。

在FPGA连线资源中,主要包含连接线段,传输管和CB中的连线资源。连接盒一般和逻辑资源放在一起进行测试,本文着重于开关盒连线资源的测试。

3 测试所需要的配置

3.1 测试采用的故障模型

1)线段开路故障,线段在制造过程中中间断开,不能正常传输信号,输出端的状态固定;

2)线段的固定O故障,不管输入信号是0还是l,线段总固定在0状态;

3)线段的固定l故障,不管输入信号是0还是1,线段总固定在1状态;

4)传输管的固定0故障,也就是常开故障,SRAM编程信息不能改变此开关的状态;

5)传输管的固定l故障,也就是常闭故障,SRAM编程信息不能改变此开关的状态;

6)线段的桥接故障,两条线段之间短路,当分别在桥接的两条金属线上加相反的信号时,因为桥接两线的输出信号是相同的。

3.2 测试所需配置

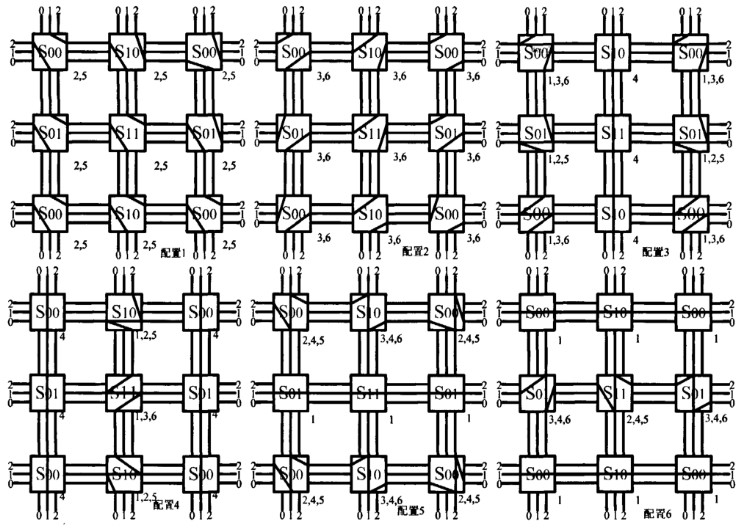

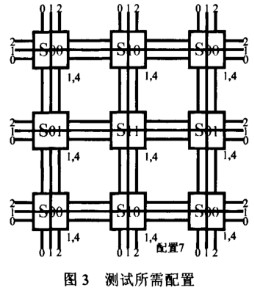

在测试之前,需要将配置信息下载到FPGA芯片中,然后施加测试矢量进行测试。本文以[3]中的配置为例说明此可测性设计,在此采用Wilton开关盒结构,配置原理与[3]一样。测试配置如图3所示。

上述的7种配置中同一个SB内编号相同的开关的状态都是一样的。配置中SB旁边的数字表示SB内需要闭合的传输管的编号。图中SB的编号Smn,其中:S00:处于奇行奇列的SB;S01:处于偶行奇列的SB;S10:处于奇行偶列的SB;S11:处于偶行偶列的SB。编号相同的SB在同一个测试配置中状态是完全一样的。如果对故障进行诊断,需要配置1到配置6。

1)配置l和配置2能够诊断任何单个线段开路故障、线段固定故障和线段桥接故障;

2)配置l、2、3、4、5和配置6能够诊断任何编号为3、6的单个传输管固定O故障;

3)配置1、2、3、4、5和配置6能够诊断任何编号为2、5的单个传输管固定0故障;

4)配置3、4、5和配置6能够诊断任何编号为4、1的单个传输管固定0故障;

5)配置l(或配置2)、配置3和配置4能够诊断任何编号为l的单个传输管固定1故障;

6)配置1(或配置2)、配置3和配置4能够诊断任何编号为4的单个传输管固定1故障;

7)配置3、4、5和配置6能够诊断编号为2、3、5、6的单个传输管固定1故障。

如果仅仅是进行故障检测,配置1、2和配置7就够了。

4 移位寄存器链测试方法

由于FPGA规模越来越大,编程SRAM单元数量巨大,下载测试配置的时间就非常大。在测试中,需将配置下载到芯片中,然后加测试矢量对连线资源进行测试,但是在下载的过程中,也同时将逻辑资源的编程数据下载到了芯片中,这种下载对测试连线资源是没有用的,所以这部分时间对连线资源测试来说是多余的。

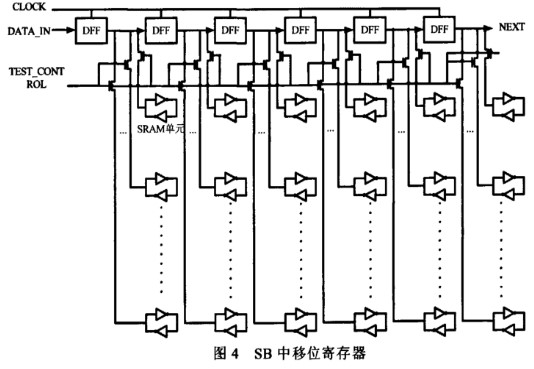

从图2的开关盒连接关系和图3中的测试配置可以看出,在一个开关盒内部编号相同的开关状态是一样的,所以在这种情况下就可以在开关盒内部增加6个触发器,每个触发器的输出端连接到相同编号的所有传输管上,并且将所有的触发器连接成多条移位寄存器链,这样在配置的时候就可以将事先设计好的配置数据通过移位寄存器链下载相对应的开关盒内SRAM单元中,每个触发器可以并行配置与其相连的SRAM单元,时间又可以节省很多。如图4所示。各信号意义如下:

1)DATA IN:将设计好的编程数据通过移位寄存器移位到相对应的位置上;

2)DATA 0UT:移位链的输出端;

3)TEST CONTROL:控制芯片为测试状态或正常工作状态。当其为1时,所有的测试控制NMOS管都闭合,将触发器的输出写到相应的SRAM单元中;而当其为0时,所有的测试控制NMOS管都断开,芯片处于正常工作状态,测试电路和工作电路完全断开,不会影响芯片的正常工作;

4)NEXT:连接到另外一个开关盒的DATA IN,将所有的触发器连接成多条移位寄存器链;

5)CLOCK:时钟控制端,控制数据的移位。其他的一些输入控制端没有列出。

测试方法:比如要实现图3中测试配置3,因为在这个配置中,开关盒S00需要将编号为1、3、6的传输管闭合,所以此开关盒寄存器的配置为101001,开关盒S10,S11需要将编号为4的传输管闭合,其需要的配置为000100,而开关盒Sol将闭合传输管l、2、5,所以其配置为110010,所以对于配置3中的9个开关盒来说,需要的配置序列为:101001,000100,10100l;1 100lO,000100,110010;101001,000100,101001。

在测试的时候分别将6种配置的测试序列分别通过下载端口下载到芯片中,实现测试需要的配置对开关盒进行测试。

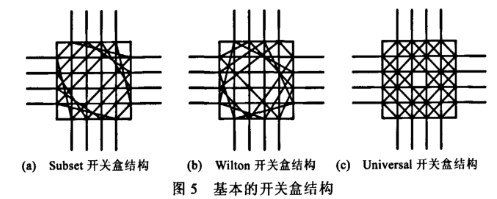

三种常用的SB结构如图5所示。

这三种结构中,同样一个方向的一个连接线段可以和其他三个方向的一个线段相连接,只是连接的线段编号不同,不过对应的配置还是一样的。以上的设计同样可以应用于这三种开关盒结构。

如果是不规则的SB结构,可以通过设计需要的测试配置来决定需要增加的触发器数目,在测试配置中,尽可能使SB内的状态相同的传输管多一些。一个基本的原则就是,在一个SB内部所有可以配置成同样状态的开关都可以利用一个触发器来进行下载。

如何测试芯片内部增加的电路呢?因为移位链有一个输出端DATA OUT,可以通过此输出端来验证移位链的正确性。对于传输管可以配合开关盒的测试来对其进行测试。如果下载以后功能正确则传输管没有常开故障。下载一定功能电路以后,将TEST CONTROL信号置0状态,即将所有的传输管断开,然后下载一个编程数据和之前相反的位流文件,如果功能未改变说明传输管没有常闭故障。

5 结果

以下从三个方面来说明此可测性设计的特点:

1)测试时间比较

首先定义几个参数,假定芯片的规模是N×N个逻辑单元,即有N行和N列逻辑单元。

NSB=N2:芯片中开关盒的个数 PS8:一个开关盒内部编程开关的数目

NCLB:芯片中CLB的个数 PCLB:一个CLB内部的编程开关的数目

NCB:芯片中CB的个数 PCB:一个CB内部的编程开关数目

T:编程下载的时钟周期 Nconfig:测试需要的配置数目

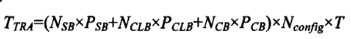

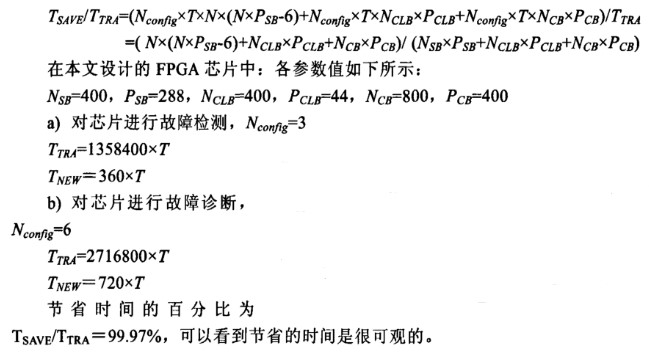

利用传统的测试方法测试SB互连资源时,需要将测试设计的配置数据下载到芯片中,此配置的编程数据包含了芯片内部所有编程SRAM的编程信息,所以在下载的时候同样将测试用不到的CLB,CB内部的编程信息也下载进去了,但是这部分的下载对测试SB是没有用的,所以时间就浪费了。传统的测试方法需要的时间为:

利用本文提出的可测性设计方法,测试数据仅仅对SB内部的SRAM单元进行配置,而且是并行的,这样就大大减小了测试SB连线资源配置需要的时间,在设计中可以实现N条移位链,利用这种方法测试需要的时间TNEW=6xNxNconfigxT

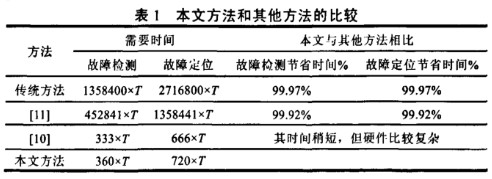

对于上述芯片的条件,测试时问比较如表1所示。

2)硬件的消耗*估

假设设计中使用的DFF内有30个MOS管,所以在设计中每个SB消耗的MOS管数目为6x30+PSB,而SB中逻辑资源包含的MOS管数目为PSBx6+NBUF,其中PSBx5是SRAM单元含有的MOS管数目,PSB是SB内传输管的数目,NBUF是SB Buffer中包含的MOS管数目。而在FPGA芯片中一般SB中逻辑资源占芯片面积的28%,所以硬件消耗的面积百分比:0.28x(6x30+PSB)/(PSBx6+NBUF)。

在本文设计的FPGA芯片中,其中只有一种开关盒。每个开关盒内部Buffer含有的MOS管数目为912个,所以如果在芯片中加入可测性移位链所消耗的面积百分比:是0.28x(6x30+216)/(216x6+912)=5.27%,消耗的面积可以接受。

由以上可以看出,文献方法在测试的过程中需要利用传统的方法下载测试少数种子配置,需要时问较多,可以看到本文提出的方法远远比文献改进很多,消耗的硬件仅稍有增加。对于文献采用的方法,需要的测试时问与本文方法可相比较,但它的硬件及内部控制比较复杂,并且测试需要相应的一些外部设备来判断是否为测试需要的配置。而本文提出的方法则比较简单,而且测试需要的时间和硬件面积的增加达到了一个比较好的平衡。

3)对芯片的影响

此可测性设计不会对芯片的正常工作产生影响,因为在芯片正常工作的时候,测试电路完全与芯片内部电路分开。所以对于芯片使用者来说不存在性能方面的问题。

6 结论

本文提出在FPGA芯片内插入多条移位寄存器链的方法,可使测试开关盒连线资源的时问比传统的测试方法和已有的一种方法时间上减少了99%以上,大大降低了测试的时间,降低了测试成本,并且消耗的硬件面积比大约在5%左右,在可接受的范围内。

-

FPGA图书分享系列-2024.01.312024-01-31 0

-

FPGA资源与AISC对应关系2024-02-22 0

-

FPGA可重构设计的结构基础2011-05-27 0

-

基于FPGA的可重构系统结构分析2011-05-27 0

-

快速浮_定点PID控制器FPGA的研究与实现2012-08-11 0

-

FPGA易测试性分析2012-08-12 0

-

matlab关于城市空气污染数据的真实性判别及分析研究2016-08-15 0

-

基于FPGA的数据采集器设计及可靠性分析2018-05-03 0

-

FPGA的三大特点和优势2019-04-12 0

-

labview FPGA技术的优势2019-04-28 0

-

FPGA有哪些特点和优势 FPGA与MCU有什么区别2020-06-23 0

-

FPGA连线资源的可测性研究及优势分析2021-05-06 0

-

fpga是什么?看完你就明白了2023-11-13 0

-

FPGA中丰富的布线资源2017-12-05 861

-

FPGA 结构分析 -IO 资源2022-12-13 1211

全部0条评论

快来发表一下你的评论吧 !