DSP中对中断的理解 浅谈DSP入门应用

处理器/DSP

描述

本文主要是关于DSP的相关介绍,并着重对DSP对中断的理解及其入门应用进行了详尽的阐述。

DSP

现代社会对数据通信需求正向多样化、个人化方向发展。而无线数据通信作为向社会公众迅速、准确、安全、灵活、高效地提供数据交流的有力手段,其市场需求也日益迫切。正是在这种情况下,3G、4G通信才会不断地被推出,但是无论是3G还是4G,未来通信都将离不开DSP技术(数字信号处理器),DSP作为一种功能强大的特种微处理器,主要应用在数据、语音、视像信号的高速数学运算和实时处理方面,可以说DSP将在未来通信领域中起着举足轻重的作用。

为了确保未来的通信能在各种环境下自由高效地工作,这就要求组成未来通信的DSP要具有非常高的处理信号的运算速度,才能实现各种繁杂的计算、解压缩和编译码。而目前DSP按照功能的侧重点不一样,可以分为定点DSP和浮点DSP,定点DSP以成本低见长,浮点DSP以速度快见长。如果单一地使用一种类型的DSP,未来通信的潜能就不能得到最大程度的发挥。为了能将定点与浮点的优势集于一身,突破DSP技术上的瓶颈,人们又推出了一种高级多重处理结构--VLIW结构,该结构可以在不提高时钟速度的情况下,实现很强的数字信号处理能力,而且它能同时具备定点DSP和浮点DSP所有的优点。为了能推出一系列更高档的新技术平台,人们又开始注重DSP的内核技术的开发,因为DSP的内核就相当于计算机的CPU一样,被誉为DSP的心脏,大量的算法和操作都得通过它来完成,因此该内核结构的质量如何,将会直接影响整个DSP芯片的性能、功耗和成本。

考虑到未来无线访问Internet因特网和开展多媒体业务的需要,现在美国的Sun公司又开始准备准将该公司的拳头产品--PersonalJava语言嵌入到DSP中,以便能进一步提高DSP在处理信号方面的自动化程度和智能化程度。当然,在以前DSP中也潜入了其他软件语言,例如高级C语言,但这种语言在处理网络资源以及多媒体信息方面无能为力;而PersonalJava是一种适合个人网络连接和应用的Java环境,基于该环境的个人通信系统可以从网络和Internet网上下载数据和图像。此外,人们还在研究开发符合MPEG-4无线解压缩标准DSP,该压缩标准将为未来通信传输各种多媒体信息提供了依据。

作为一个案例研究,我们来考虑数字领域里最通常的功能:滤波。简单地说,滤波就是对信号进行处理,以改善其特性。例如,滤波可以从信号里清除噪声或静电干扰,从而改善其信噪比。为什么要用微处理器,而不是模拟器件来对信号做滤波呢?我们来看看其优越性:模拟滤波器(或者更一般地说,模拟电路)的性能要取决于温度等环境因素。而数字滤波器则基本上不受环境的影响。数字滤波易于在非常小的宽容度内进行复制,因为其性能并不取决于性能已偏离正常值的器件的组合。一个模拟滤波器一旦制造出来,其特性(例如通带频率范围)是不容易改变的。使用微处理器来实现数字滤波器,就可以通过对其重新编程来改变滤波的特性。

DSP中对中断的理解

1 中断概述

中断定义:由硬件或软件驱动的信号,使DSP将当前的程序挂起,执行另一个称为中断服务子程序(ISR)的任务。

C55x支持32个ISR。有些ISR可以由软件或硬件触发,有些只能由软件触发。

当CPU同时收到多个硬件中断请求时,CPU会按照预先定义的优先级对它们做出响应和处理。

所有的软件中断都是不可屏蔽中断

DSP处理中断的步骤:

(1)接收中断请求。软件和硬件都要求DSP将当前程序挂起。

(2)响应中断请求。CPU必须响应中断。如果是可屏蔽中断,响应必须满足某些条件。如果是不可屏蔽中断,则CPU立即响应。

(3)准备进入中断服务子程序。

CPU要执行的主要任务有:

完成当前指令的执行,并冲掉流水线上还未解码的指令

自动将某些必要的寄存器的值保存到数据堆栈和系统堆栈

从用户实现设置好的向量地址获取中断向量,该中断向量指向中断服务子程序

(4)执行中断服务子程序。

CPU执行用户编写的ISR。ISR以一条中断返回指令结束,自动恢复步骤(3)中自动保存的寄存器值。

☼ 注意:

外部中断只能发生在CPU退出复位后的至少3个周期后,否则无效;

在硬件复位后,不论INTM位的设置和寄存器IER0、IER1的值如何,所有的中断都被禁止,直到通过软件初始化堆栈后才开放中断。

2 可屏蔽中断

所有的可屏蔽中断都是硬件中断。

无论硬件何时请求一个可屏蔽中断,在一个中断标志寄存器里就有相应的中断标志置位。该标志一旦置位,相应的中断还必须使能,否则不会得到处理。

当CPU在实时硬件仿真模式下暂停时,只能处理时间临界中断。

可屏蔽中断标准处理流程:

1. 向CPU发送中断请求。

2. 设置响应的IFR标志。CPU检测到一个有效的可屏蔽中断请求时,它设置并锁上某个中断标志寄存器的响应标志位,这个位保持锁定,直到该中断得到响应或者复位,才清楚

3. IER中断使能?根据中断使能寄存器是否使能,响应中断。

4. INTM = 0?全局开放中断,才响应

5. 跳转到ISR服务程序,

6. 执行ISR服务程序

7, 返回。

3 不可屏蔽中断

当CPU接收到一个不可屏蔽中断请求时,立即无条件响应,并很快跳转到相应的中断服务子程序(ISR)

C55x的不可屏蔽中断有:

硬件中断/RESET。如果引脚/RESET为低电平,则触发了一个DSP硬件复位和一个中断(迫使执行复位ISR)。

硬件中断/NMI。如果引脚/NMI为低电平,则CPU必须执行相应的ISR。 /NMI提供了一种通用的无条件中断DSP的硬件方法。

软件中断。

4 按键中断

按键中断,属于可屏蔽中断,用户自定义硬件中断,当CPU响应按键后,检查相关引脚中断标记寄存器,若标志位为1,则响应该中断。同时,清除中断标志寄存器位。

5 c_int00

当C环境被初始化时,启动程序禁止中断。 如果系统使用中断,必须处理有关的中断使能或屏蔽。

关于中断的几个要点:

中断程序会执行任何其它函数执行的工作,包括访问全局变量、为局部变量分配地址、调用其它函数。

需要处理任何特殊中断屏蔽(通过IER0寄存器)。通过嵌入汇编语言语句可以使能或禁止中断,也可以修改IER0寄存器而不会破坏C环境或C指针。

中断处理程序不能有参数,即使声明了参数也会被忽略

中断处理程序不能被普通C代码调用。

为了将中断程序和中断联系起来,需要将分支程序放在合适的中断向量中,通过.sect指令创建一个简单的分支指令表就可以实现此操作。

在汇编语言中,需要在中断程序名前加下划线,如_c_int00。

分配堆栈到偶地址。

c_int00是系统复位中断。当进入c_int00中断时,运行时间堆栈并没有被建立起来,因此不能为局部变量分配地址,也不能在运行时间堆栈中保存任何信息。

通过interrupt关键字可以用C函数直接处理中断。

interrupt关键字可以和定义为返回void并不含参数的函数一起使用。中断函数体可以有局部变量,可以自由使用堆栈。

c_int00是C程序入口。这个名字被保存为系统重启中断。这个特殊的中断程序初始化系统并调用了主函数。因为没有调用者,所以c_int00不保存任何寄存器。

例,

interrupt void isr()

{

。。.

}

中断管理

基于DSP/BIOS管理中的硬件中断,DSP/BIOS为中断提供了一个HWI调度程序,为ISR完成必要的开头和结尾部分。如果不使用,则在调用任何DSP/BIOS对象的API之前,必须调用HWI_enter和HWI_exit汇编宏来完成ISR的开头和结束。实际上,DSP/BIOS提供的调度程序,就包括这两个宏。

为了正确响应硬件中断,同时,也为了DSP/BIOS内核的稳定性,必须注意:

1 在一个硬件中断ISR中,不要调用SWI_disable和SWI_enable。

2 在NMI(不可屏蔽)中断中,不要调用硬件中断使能/禁止函数。

3 当使用DSP/BIOS调度程序时,不要使用HWI_exit和HWI_enter汇编宏

4 中断中,可以打开新中断。

我们可以在中断配置选项卡中,设置Interrupt Mask 来实现在DSP/BIOS调度程序执行前禁止某些中断。

浅谈DSP入门应用

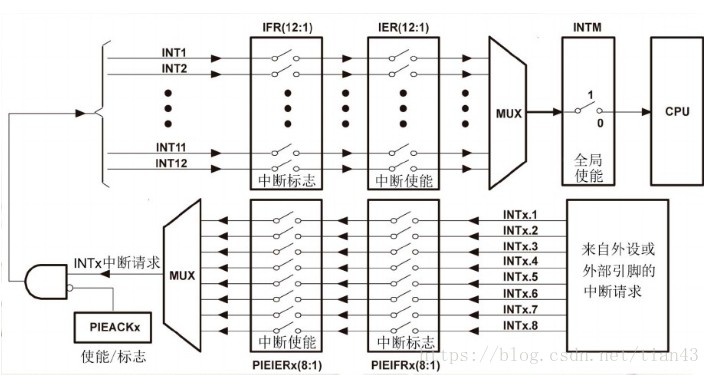

1、DSP中断管理分为3个层次:外设级,PIE级,CPU级。

其中,外设级中断管理负责具体外设中断源的允许与禁止,PIE级中断管理负责对外设级中断分组并按照优先级管理,CPU内核级中断管理则负责处理直接向CPU申请的中断请求。

DSP控制器的外设中断扩展模块(PIE),对中断进行集中化扩展,使每一级CPU中断均可以响应多个中断源。

2、PIE级中断及管理:

CPU内核级中断(INT1–INT14),INT1-INT12被PIE模块用来进行中断扩展,有12组,每组8个中断源。

各中断的优先级自上而下,由右到左逐步降低,总体优先级INT1最高,INT12最低。

INT13由CPU定时器1和外部中断XINT13复用,INT14由定时器2独占。

3、中断响应过程

4、中断寄存器介绍

PIEIFRx (1-12)中断标志寄存器

PIEIERx (1-12)中断屏蔽寄存器

各有12个,每个16位宽,只用了前8位分别表示8个中断源;IFR标志中断到来,IER表示是否要响应(PIEIFRx.1-8,PIEIERx.1-8)

PIEACKx (1-12)应答位

CPU是否响应给位的中断,为0中断送入CPU,为1等待

PIECTRL PIE控制寄存器,只读

读取中断向量

XINTnCR (n为1-7) 7个外部中断

选择中断边沿,01上升沿;外部中断允许位

5、代码片

PieCtrlRegs.PIEIFR1.bit.INTx4=1;//在PIE中断组1设置XINT1的中断标志位

PieCtrlRegs.PIEIER1.bit.INTx4=1;//允许PIE中断组1的XINT1 中断

PieCtrlRegs.PIEACK.all = 0x0004;//清除中断组3的ACK位,以便再次响应

PieCtrlRegs.PIECTRL.bit.ENPIE=1;//允许从向量表中读取中断向量

1

2

3

4

5

6、定时器中断实例

#include “DSP2833x_Device.h”

#include “DSP2833x_Examples.h”

interrupt void cpu_timer0_isr(void);//声明中断服务函数

void main()

{

//step1:初始化系统控制、PLL、看门狗、允许外设时钟

InitSysCtrl();

//step2:初始化GPIO

InitGpio();

//step3:清除所有中断,初始化PIE向量表

DINT;

InitPieCtrl(); //初始化PIE控制器

IER = 0x0000; //禁止CPU中断

IFR = 0x0000; //清除所有CPU中断标志

InitPieVectTable(); //初始化PIE中断向量表

EALLOW;

PieVectTable.TINT0 = &cpu_timer0_isr; //重映射中断向量,指向中断服务程序

EDIS;

//step4:初始化外设模块

InitCpuTimers();

ConfigCpuTimer(&CpuTimer0,150,1000000); //150MHz,周期1秒

CpuTimer0Regs.TCR.all = 0x4001; //允许定时器中断,且设置TSS为0启动定时器工作

//step5:

IER |= M_INT1; //允许CPU的INT1中断,该中断连接至TINT0

PieCtrlRegs.PIEIER1.bit.INTx7 = 1; //在PIE中断组1中允许TINT0中断

EINT; //清除全局屏蔽

ERTM; //允许全局实时中断

//step6:循环

while(1);

}

interrupt void cpu_timer0_isr(void)

{

CpuTimer0.InterruptCount++;

PieCtrlRegs.PIEACK.all = PIEACK_GROUP1; //清除PIE中断组1的应答位,以便CPU再次响应

}

结语

关于DSP的相关介绍就到这了,希望通过本文能让你对DSP有更全面的认识。

-

基于DSP中断设置简明教程2017-10-23 739

-

#硬声创作季 #DSP 手把手教你学DSP-06 中断系统及应用-1水管工 2022-10-25

-

#硬声创作季 #DSP 手把手教你学DSP-06 中断系统及应用-2水管工 2022-10-25

-

#硬声创作季 #DSP 手把手教你学DSP-06 中断系统及应用-3水管工 2022-10-25

-

#硬声创作季 #DSP DSP从入门到编写-16 EPWM的中断水管工 2022-10-25

-

如何快速入门DSP2012-02-27 0

-

DSP从入门到精通全集2006-03-30 14613

-

带你了解TI的DSP入门芯片TMS320F283352012-08-15 37408

-

Dsp28335中断的方法2016-01-08 902

-

DSP入门资料(精华)2016-07-13 392

-

DSP从入门到精通全集—DSP中的DAC_英版2016-07-18 584

-

DSP从入门到精通全集—DSP中的ADC_英版2016-07-18 429

-

DSP从入门到精通全集—DSP 硬件_英版2016-07-18 643

-

基于DSP开发入门综述2017-10-23 693

-

DSP- CCS编程入门2017-10-23 719

全部0条评论

快来发表一下你的评论吧 !