资料下载

高速串行IO如何简单化?设计指南与FPGA应用详细资料免费下载

人生中只有少数几次幸运地成为新发现或想法的一部分,而这些发现或想法的时代终于来临了。其中一些想法或创新可以极大地改变我们生活的宇宙。想想看,当生物科学家对绘制整个人类基因组——识别我们DNA结构中的最后一个基因——进行最后的研究时,身处美国国立卫生研究院的实验室一定有什么感觉。或者在贝尔实验室,当巴丁、布拉顿和肖克利演示了导致通信革命的第一个工作晶体管时。

仅仅在过去的50年里,科学家和工程师已经产生了数量惊人、种类繁多的科学技术突破。他们提出的想法改变了我们的思维方式和我们做几乎一切的方式。例如,连接研究中心计算机的愿望演变成今天的互联网——许多人认为这是我们有生之年创造的商业、社会和政治变革的最重要工具。

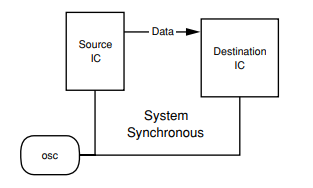

今天,我们再一次成为见证和参与这些稀有科技时刻的一员。电子工业正在发生根本性的转变_从并行I/O方案向串行I/O连接解决方案的转变。这种变化是由各个行业的公司推动的,作为降低系统成本、简化系统设计和提供满足新带宽需求所需的可伸缩性的手段。

在Xilinx,我们坚信串行连接解决方案将最终部署到几乎每个电子产品的各个方面。这种部署将出现在芯片到芯片接口、底板连接和系统板以及盒到盒通信中。为了支持这个信念,我们宣布了一个“高速串行倡议”来帮助加速工业从并行向高速串行I/O的转变。每秒比特数(Mb/s)到每秒11.1千兆比特(Gb/s),以及超过。

业界分析家一致认为,高速串行倡议是不可避免的,因为当数据速率开始超过1Gb/s时,并行I/O方案达到物理限制,并且不再能够提供可靠的、成本效益高的保持信号同步的手段。基于串行I/O的设计比传统的并行实现提供了许多优点,包括更少的器件引脚、减少的板空间要求、更少的印刷电路板(PCB)层、更容易的布局PCB、更小的连接器、更低的电磁干扰和押注。抗噪声能力。

从并行到串行的转变将不是没有工程挑战。其中,最大的问题是,人们认为设计高速串行I/O解决方案是如此困难和复杂,以至于尽管存在明显的缺点,系统工程师仍宁愿继续使用现有的并行技术。为了解决这些挑战,我们创建了串行I/O启动器指南。它向所有对迅速发展的串行技术感兴趣的设计师提供帮助,但是对于迈出第一步犹豫不决。对于那些已经用串行进行设计的读者来说,这本书可以看作是《通过高速串行倡议》,Xilinx为各种串行系统体系结构提供了技术专长和完整的、预先设计的解决方案。这些架构包括网络、电信和企业存储市场,这些市场由具有集成串行I/O收发器的Xilinx平台FPGA提供,集成串行I/O收发器是最终连接平台。

除了这本书,Xilinx还积极参与帮助推动系列技术标准的关键行业组织。此外,Xilinx提供了广泛的“生态系统”合作伙伴网络(EDA、参考设计、IP、设计服务等),以保证互操作性和对最新技术、技术和设计工具的访问。

全世界都在接受串行技术。在FPGA中包括高速串行I/O(如RocketIO™收发器)使得串行成为首选的系统连接解决方案。我们还认识到,对于大多数熟悉并行I/O技术的设计人员来说,高速串行设计的许多挑战仍然是新的。串行I/O启动器指南提供了串行I/O设计的基本原理,以便任何人都可以开始正确应用这一革命性的技术。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。 举报投诉

- 相关下载

- 相关文章