资料下载

如何轻松实现高速串行IO?FPGA应用设计指南详细资料中文版免费下载

I/O性能极限

输入/输出(I/O)在计算机和工业应用中一直扮演着关键角色。但是,随着信号处理越来越复杂, I/O通信会变得不可靠。在早期的并行I/O总线中,接口的数据对齐问题影响着与外部设备的有效通信。并且,随着更高的传输速度在数字设计中日渐普及,对信号延迟的管理也变得困难重重。

针对I/O的数字设计解决方案

数字电路设计者采用了一系列方法来提高信号速度和消除I/O问题。例如,采用差分信号处理来提高芯片间的通信速度。信号同步、源同步和自同步之类的设计方法改善了内部IC(集成电路)通信,在满足计算机行业所需速度的前提下,提供了可靠的输入/输出。

千兆位级串行技术介绍

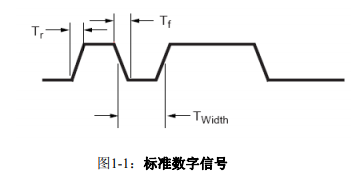

图1-1为典型的数字信号。

晶体管-晶体管逻辑电路(TTL)曾是首选的设计方法。分立的逻辑门芯片可以相互通信从而组成更大规模的电路,这些更大规模的电路后来又集成为复杂的芯片,例如多比特寄存器和计数器。多年来,并行通信一直是印刷电路板(PCB)所采用的主要通信方法。但对于外部通信而言,数据对齐问题太难解决。因此,串行端口成为了设备盒到设备盒之间通信的主要方法,这一点在早期的计算机串行打印机端口中得到了证实。

数据对齐问题最终得以解决。随着并行技术的发展,高速并行打印机端口激增。这些并行端口技术包括工业标准架构(ISA)、扩展工业标准架构(EISA)和小型计算机系统接口(SCSI)、外围部件互联(PCI)以及更小的个人电脑存储器卡行业协会(PCMCIA)标准。

串行技术继续与并行技术共存。以太网和令牌环在许多应用中占主导地位。最终,以太网在使用五类线(Cat5)的应用中取代了令牌环。

并行技术竭力适应新的接口需求。随着对特殊信令越来越多的需求,PCI 33之类的标准也发展成PCI 66。目前,低摆幅标准(如高速晶体管逻辑(HSTL))试图支持并行技术。同时,以太网速率从10Mb/s提高到100Mb/s,进而达到1000Mb/s。这类速度使得以太网非常适于应用在桌上型电脑中。

这时,分数相位检测器(fractional phase detector)面世了。这项技术将串行接口速度提高到了千兆位级的范围。串行技术被证明是快速而功能强大的,可作为背板技术采用。随着串行引脚数和同步开关输出(SSO)的提高,千兆位级串行技术在PCB中获得了主导地位,取代了并行技术。

基本I/O概念

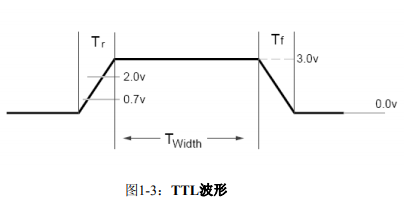

单端I/O成为标准已有数年光景。单端系统中,2个IC间仅用单一的信号连接。该信号与指定的电压范围(TTL CMOS [互补金属氧化物半导体])或参考电压(HSTL)进行比较。这些方法的指标示例如图1-3所示。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。 举报投诉

- 相关下载

- 相关文章