CAN总线通讯软件的设计及在航空领域的应用研究

描述

1 、引言

CAN总线是由德国BOSCH公司为现实汽车测量和执行部件之间的数据通讯而设计的、支持分布式控制及实时控制的串行通讯网络。CAN总线通讯的波特率可高达1Mbps,最远距离可达10km;CAN总线通讯采用短帧结构,数据传输的时间短,受干扰的几率低;CAN总线协议有良好的检错措施,可靠性较高;CAN总线通讯对于传送帧可以设定不同的优先级,通过总线仲裁机制使高优先级的信息能够被优先及时传送,增加了CAN总线通讯的实时性;CAN总线的完善可靠的通信协议主要由接口器件完成,降低了软件开发的难度。此外,CAN总线网络中的每节点对应一个地址,理论上基于CAN总线的网络上可以添加删除任一节点,通讯方式可以为点对点的通讯也可以为广播方式,可以为单主方式也可以是多主方式,因此CAN总线通讯有相当的灵活性。

CAN总线开始主要应用于自动化电子领域的汽车发动机部件、传感器、抗滑系统等应用中,但随着CAN的应用普及,其应用范围已不局限于汽车行业,正在向过程控制、机械、纺织等行业发展,应用领域从高速网络到低成本的多线网络。而且CAN总线的实时性以及抗干扰能力强等优点也逐步为航天领域所认可。1995年SSTL(Surrey大学卫星技术公司)将CAN作为星载遥测/遥控信道,随之SSTL开发了基于CAN的分布式解决方案。至今SSTL已经在UoSAT-12,SNAP-1,AISAT-1,UKDMC,NigeriaSAT-1,BilSAT-1 等6颗LEO卫星中应用了CAN总线网络,用于实现星载计算机与其他任务节点之间的通信;ESA在SMART-1上也将CAN作为系统总线和有效载荷总线,实现数据交换和控制命令的传送。在国内,CAN总线技术在小卫星中也得到了实际的应用。

本文在分析CAN总线航天应用的基础上,从硬件原理设计、CPU与CAN总线接口实现以及CAN总线通信软件设计等方面进行了论述。

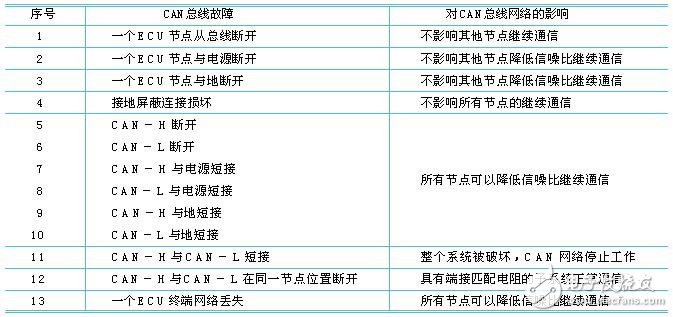

表1 CAN总线故障及其影响分析

2 、CAN总线工作原理

CAN总线的多主站工作方式的发送原理采用“载波侦听多路访问/冲突检测”(CSMA/CD:Carrier Sense Multiple Access with Collision Detect)技术实现。利用CSMA访问总线,可对总线上信号进行检测,只有当总线处于空闲状态时,才允许发送。利用这种方法,可以允许多个节点挂接到同一网络上。当检测到一个冲突位时,所有节点重新回到‘监听’总线状态,直到该冲突时间过后,才开始发送。在总线超载的情况下,这种技术可能会造成发送信号经过许多延迟。为了避免发送延时,可利用CSMA/CD方式访问总线。当总线上有两个节点同时进行发送时,通过“无损的逐位仲裁”方法来使有最高优先权的报文优先发送。在CAN总线上发送的每一条报文都具有唯一的一个11位或29位数ID。CAN总线状态取决于二进制数‘0’而不是‘1’,所以ID号越小,该报文拥有越高的优先权。

CAN总线的多主站工作方式的接收原理是通过验收滤波器来实现的。独立的CAN 控制器SJA1000设置了一个多功能的验收滤波器,该滤波器允许自动检查标识符和数据字节。使用验收滤波器的滤波方法可以防止对于某个节点无效的报文或报文组存储在接收缓冲器里,因此降低了主控制器的处理负荷。滤波器由验收码寄存器(ACC)和屏蔽寄存器(AMR)组成。在BasicCAN 模式里的验收滤波,其判据为:(ACC(7:0) ⊙ ID(10:3))+AMR(7:0)。如果判据的结果为“11111111”,则表示该帧数据是其他节点传送给本节点的数据,本节点CAN总线控制器将接收本帧数据,在CRC校验无误后于应答间隙产生应答信号。

3 、CAN总线航天应用分析

ESA开展的CAN、1553B、SpaceWire技术研究表明以差分信号传输的高速串行总线用于星载设备之间的数据传输能保证通信的及时性, 利于降低星载设备的功耗,有助于获得低噪声、抗电磁干扰性强、EMI低、信号不受电源开关状态变化影响等优势, 具有良好的航天应用前景。

CAN总线作为一种专为汽车工业设计的现场总线,具有很多适合航天应用的特点:作为多主站方式的串行通讯总线,CAN总线具有低成本,高抗电磁干扰性,高总线利用率,很远的数据传输距离(长达10km),高速的数据传输速率(高达1Mbps),可根据报文的ID决定接收或屏蔽该报文,可靠的错误处理和检错机制,发送的信息遭到破坏后,可自动重发,节点在错误严重的情况下具有自动退出总线的功能等特点。

ISO11898建议的CAN总线的物理电气性能,能够保证在总线发生某些故障时不至于中断通信,而且可以为故障的定位提供可能。表1列出了CAN总线可能发生的各种开路和短路故障,以及在该故障模式下CAN总线受影响的情况。

CAN总线具有安全可信性。从协议分析,CAN总线的每个ECU具备错误检测、标定和自检的强有力措施。检测错误包括:发送自检、CRC校验、位填充和报文格式检验。其错误检测具有如下特性:其一, 所有全局错误都可以检测;其二,发送器的所有局部错误都可以被检测;其三,报文中5个以内的随机分布错误都可以被检测到;其四,报文中长度小于15的突发性错误都可以被检测得到;其五,报文中任何奇数个错误都可以被检测得到;其六,没有检测出的已损报文的剩余错误概率为报文出错率的4.7×10-11。

SSTL经过研究发现,在600公里~1000公里的空间领域,空间辐射对卫星的影响相对较小。在这个高度上,总剂量为每年1Krad左右(其量级相当于增加5mm的铝屏蔽层),SEU发生率相当于每天每Mbyte一次(此数据来源于试验观察),并且观测到的SEL发生概率非常低,在SSTL整个记录中只记录到3到4次值得怀疑的情况(确定的只有4次)。SSTL还发现几乎所有的商业CMOS器件,在经受10 Krad辐照后其性能并无明显下降。SSTL在低轨道小卫星采用工业级CAN控制器芯片构建卫星CAN总线网络的成功,验证了上述结论。表2为SSTL在近年来采用的COTS CAN器件。

表2 Surrey大学采用的COTS CAN器件统计列表

器件飞行任务次数

Philips CAN收发器:当前主流产品 4

Philips PCA82C250 10

Philips P87C592 10

Philips CAN 8位外设:产权主流产品 4

Philips PCA82C200:CAN 8位外设 6

Infineon:8位CAN微控制器(A/D,PWM,例如8051) 6

Microchip CAN SPI外设 4

4 、星载计算机中的双冗余容错CAN总线设计

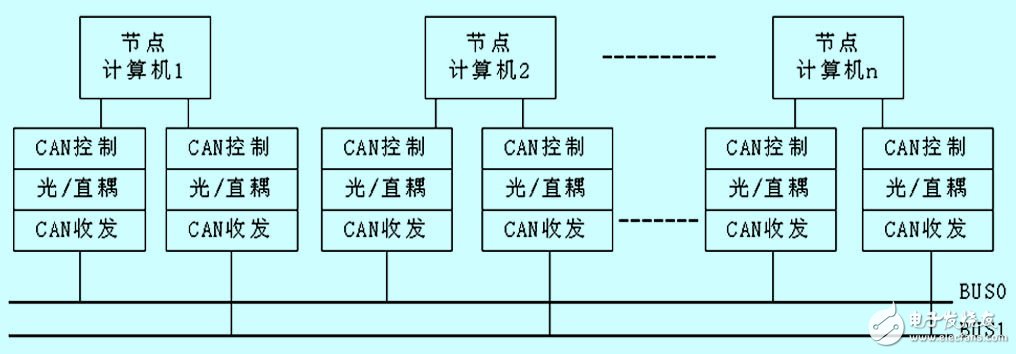

图1描述了基于CAN的双冗余总线结构。基于CAN总线的双冗余系统通信总线的基本设计思想是在卫星各功能模块之间布下两条基于CAN的系统通信总线,即用两套CAN总线控制模块分别连接到总线BUS0和BUS1上。正常情况下优先在一条总线上通信,这条总线出现故障时通过另一条进行通信并重新初始化出错的总线以备将来再用。这样即使一条通信通道故障后不会影响整个系统的数据交换,大大提高了通信的可靠性。

图1 基于CAN的双冗余总线结构

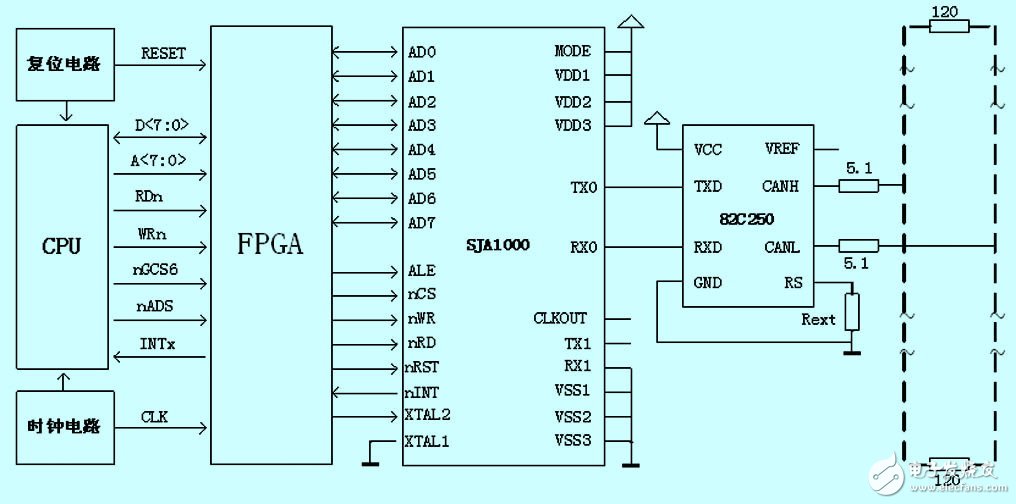

图2 CAN总线硬件设计原理简图

图2为星载计算机中CAN总线硬件设计原理框图。 CAN总线协议控制芯片选用Philip的工业级器件SJA1000,收发器选用Philip的PCA82C250。CPU与SJA1000的接口控制逻辑通过Actel的反熔丝FPGA实现。SJA1000工作在Intel模式,工作时钟为7.3728MHz。复位信号通过MAX708产生。为了有更好的EMC/EMI性能和抑制比较器的噪声,VDD通过RC滤波器退耦。

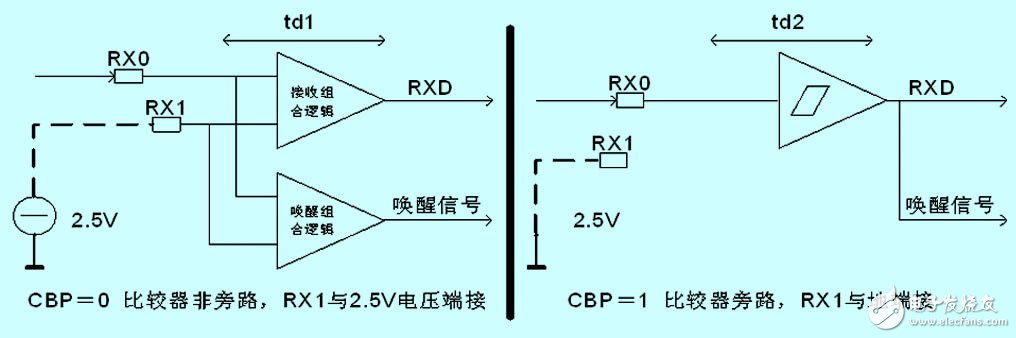

SJA1000的RX1信号处理非常关键。如果使用外部集成收发器电路而且没有在时钟分频寄存器里使能比较器旁路功能,RX1输出要被连接到2.5V的参考电压(82C250的Vref输出)。图3显示了CBP的两种设置所对应的电路。对于使用82C250集成的收发器电路,SJA1000的相关数据手册建议使用旁路功能,即CBP设置为1,在这种情况下,SJA1000的比较器旁路功能有效,减少了内部传播延迟,即td2《td1,提高了CAN总线的最大长度,休眠模式的电流将显著降低。在CBP为1时,硬件设计必须保证RX1接地。

图3 SJA1000的接收输入比较器旁路设计

82C250的RS信号通过电阻Rext接地。RS管脚的电流决定了传输介质上传输信号的信号沿的陡峭程度,Rext阻值的大小必须根据CAN总线的工作速度及其工作环境进行设计和选择,具体可参见SJA1000的数据手册或者应用文档。

5 CPU与SJA1000的接口逻辑设计

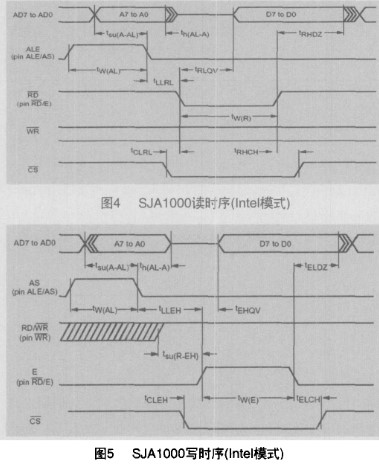

星载计算机的CPU不同于8086,采用的是独立地址和数据总线。CAN总线控制器SJA1000采用地址/数据总线复用方式,需要将CPU的总线信号经过适当逻辑处理后才能够满足CAN总线控制器的时序要求。图4和图5是SJA1000在Intel模式下的读写时序。

按照SJA1000的数据手册,确保SJA1000的读写正确,如下的时序参数必须满足:

l tW(AL):必须保证ALE的时间,最小不能小于8ns;

l tLLRL/tLLWL:读写时ALE无效到读写信号有效的时间,最小不能小于10ns;

l tLCRL/tLCWL:片选信号有效后读写信号有效的时间,最小不能小于0,即片选有效必须出现在读写信号有效前;

l tW(R):读信号有效宽度,最小不能小于40ns;

l tW(R):写信号有效宽度,最小不能小于20ns;

l tWHLH:写信号无效到下一次ALE有效的时间,最小不能小于15ns;

l th(AL-A):在ALE为低电平后地址应该保持时间,最小不能小于2ns。

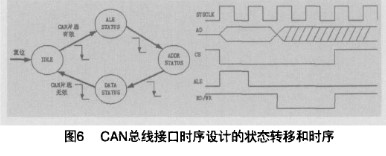

CPU和CAN总线接口采用地址直接映射。接口时序设计重点是接口控制逻辑必须产生符合上述关键参数的读写时序。如果简单的按照ALE《=not nADS方法处理,不满足要求时序关系,这在调试过程中已经得到验证。为此,在设计中采用了FPGA技术,以求很好地解决CAN总线与CPU的接口问题。图6描述了通过VHDL编写实现接口电路的状态转移图和FPGA设计产生的读写CAN总线时序,其中时钟周期不低于67ns,该时序满足SJA1000要求。

6 、CAN总线通讯软件的设计

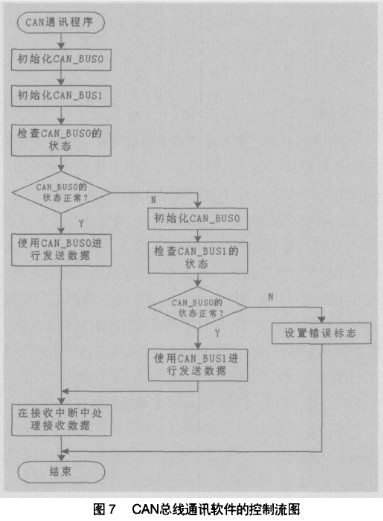

双冗余总线结构的通讯软件主要由初始化、接收和发送三个模块组成,控制流图见图7。在程序设计时采用了SJA1000的Basic模式,初始化中需要对BUS0和BUS1分别进行初始化,包括SJA1000的控制寄存器、接收代码寄存器、接收屏蔽寄存器、总线时序寄存器等。

发送模块采用主动发送方式,BUS0为优先通讯通道,若BUS0通道状态不正常,则启动BUS1通道进行通讯,并对BUS0通道进行初始化以备下次通讯时使用。

接收模块采用中断接收方式,为了保证接收到的数据被实时处理,CAN总线的接收中断被设置为高优先级中断。在接收中断中首先判断接收通道是BUS0还是BUS1,然后从接收通道按数据长度进行数据接收。

7 、结束语

CAN总线技术的诸多优点如实时性好,通信速率高,抗干扰能力强,低廉的价格等使它不仅广泛应用于工业控制领域,而且开始向航天领域进军。其COTS工业级器件SJA1000经过飞行也得到了验证,CAN总线适宜航天应用的特点得到了充分的展示和飞行验证。

责任编辑:gt

-

#硬声创作季 #CAN #PLC CAN总线在工业通讯中的应用前景如何?学习电子知识 2022-11-02

-

基于CAN总线的网络化PLC技术研究与实现-硕士学位论文2009-10-31 0

-

ZigBee技术在矿灯监控中的应用研究2013-03-15 0

-

CAN总线通讯平台开发2019-04-08 0

-

RFID在航空领域的应用有哪些误区?2019-08-05 0

-

CAN总线数据离线分析软件-X-CAN2020-01-05 0

-

基于CAN总线的电梯串行通讯2009-06-25 658

-

CAN总线应用—汽车领域2011-12-14 809

-

基于CAN总线的通讯系统软件框架设计2017-01-24 804

-

自动选择工具在通讯软件中的应用研究_陈擎月2017-03-19 703

-

CAN总线的原理、通信接口设计及在航天卫星中的应用研究2020-04-02 2971

-

基于S3C2410的CAN总线通讯设计与开发2021-04-20 668

-

CAN总线的应用研究2021-04-20 461

-

为什么说双通道CAN总线通讯卡是最好选择2022-01-27 3188

-

Loto实践干货(3) 测量CAN总线通讯数据2022-05-31 768

全部0条评论

快来发表一下你的评论吧 !