资料下载

×

扫描模式下ADC如何发生通道间串扰?详细解答

消耗积分:0 |

格式:rar |

大小:0.15 MB |

2018-09-27

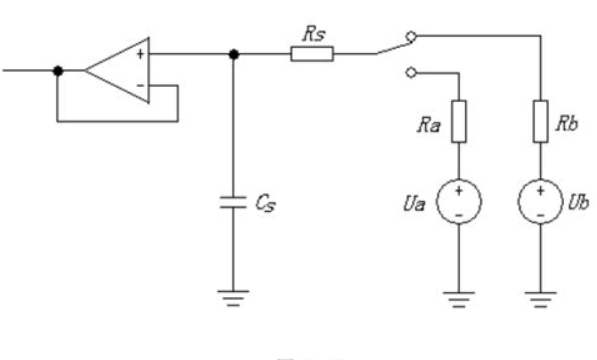

该问题由某客户提出,发生在 STM32F103VDT6 器件上。据其工程师讲述:在其产品中,需要使用STM32 的 ADC 对多路模拟信号进行同步采样。在具体的实现上,采用了 ADC 常规通道的扫描模式来完成这一功能。然而,在调试中过程中发现一个奇怪的现象:当将各路模拟信号的电平设置成相同时,ADC 对各路模拟信号的转换结果相同,用 A 来表示。改变其中一路模拟信号的电平,并保持其各路模拟信号的电平不变,则 ADC 对该路信号的转换结果变为 B。然而,此时与其在扫描次序上相邻的下一路模拟信号的转换结果也发生了变化,记作 C。经多次实验发现,B 和 C 在数值上相对于 A 有相同的变化方向。于是,怀疑 ADC 的相邻通道间存在着某种串扰。

重复试验,确认现象如其所述。检查其硬件设计,在与 VDD、VDDA、VSS、VSSA、Vref+、Vref-相关的电路中未发现异常。修改软件,增大 ADC 各个通道的采样保持时间Ts 。重新测试,发现 C 相对于 A 的变化量有所减小。进一步增大 ADC 各个通道的采样保持时间Ts,发现 C 相对 A 的变化量进一步减小。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。 举报投诉

评论(0)

发评论

- 相关下载

- 相关文章