解决保持时间违例流程

电子说

描述

在分析place_design生成的dcp时,就要开始关注保持时间违例,尤其是当WHS < -0.5ns时。这是因为过大的保持时间违例往往会导致布线时间增大,同时,在布线阶段,工具未必能修复此类违例。

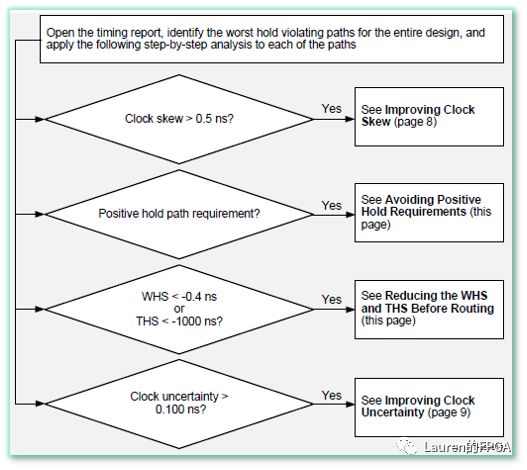

解决保持时间违例流程如下图所示。按照此流程,要逐步关注以下几个因素:

Clock Skew是否大于0.5ns

Hold Requirement是否为正(应该为0)

WHS是否小于-0.4ns或THS是否小于-1000ns

Clock Uncertainty是否大于0.1ns

图片来源 page 4, ug1292

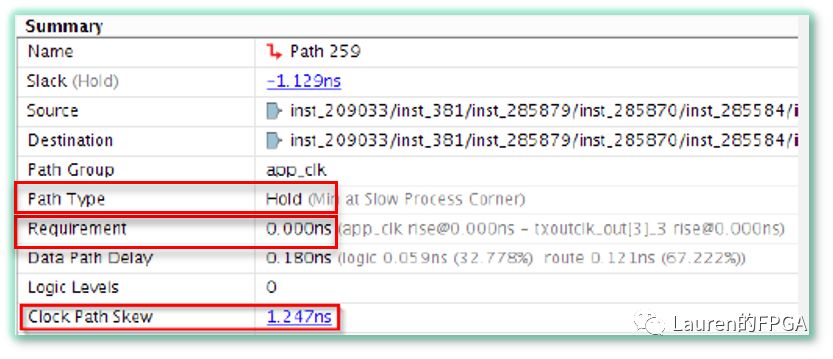

这几个指标的具体数值可在时序报告中查到,如下图所示。图中,Path Type用于确定分析的是保持时间。

图片来源 page 4, ug1292

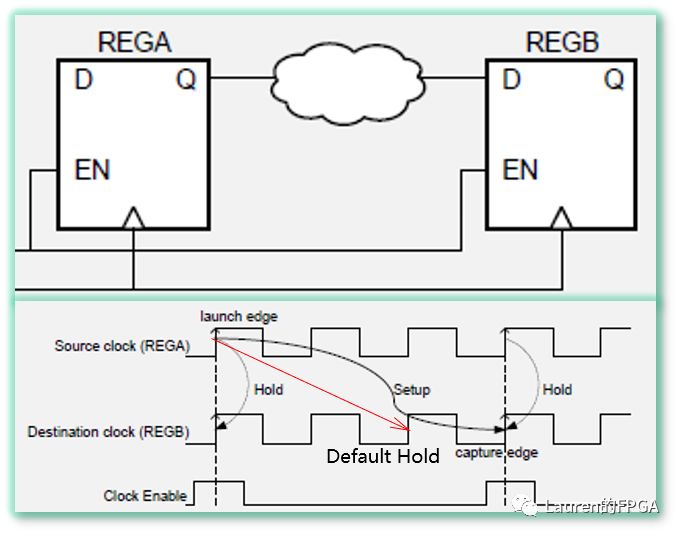

Hold Requirement为正的可能情形出现在使用多周期路径约束的时序路径中。如下图所示,时钟使能信号EN使得路径的Setup Requirement为3个时钟周期,但Hold Requirement仍应为0。

图片来源 page 4, ug1292

在此情况下,应采用如下图所示的多周期路径约束。其中的第2条约束是对hold的调整,却往往容易被遗漏。对于-hold,它表示相对于缺省捕获沿(图中的Default hold),实际捕获沿应回调的时钟周期个数。

对于过大的WHS或THS,应在布线之前做一些优化,尽可能地降低WHS和THS。为此,可在phys_opt_design阶段采取如下图所示的几个措施。

其中方法(1)是在两个同步时序元件之间插入与至相反的时钟沿触发的寄存器,将该路径一分为二,该方法的前提是建立时间不会被恶化。方法(2)至方法(4)都是在路径中插入LUT1。方法(2)只在WHS最大的路径中插入LUT1;方法(3)则是在更多的路径中插入LUT1;方法(4)则是在-directive为Explore的基础上进一步修正保持时间违例,等效于-directive Explore +-aggressive_hold_fix。

-

请问stm32不精确的数据访问违例怎么解决?2018-09-28 0

-

出现时序违例的原因及解决办法2021-01-08 0

-

篮球前场进攻24秒违例音响器电路图2009-05-30 969

-

门球违例裁判器电路图2009-07-29 508

-

基于概率时间Petri网的流程推荐方法2018-01-14 808

-

检测内存泄漏和内存违例,Valgrind不可少!2018-05-07 6020

-

Vivado时序案例分析之解脉冲宽度违例2020-11-19 4793

-

静态时序之建立时间和保持时间分析2022-08-22 3400

-

怎么解决解决Hold Time违例的问题呢2023-01-11 2636

-

芯片设计进阶之路—从CMOS到建立时间和保持时间2023-06-21 981

-

数字IC设计中的建立时间和保持时间2023-06-21 1268

-

时序约束出现时序违例(Slack为负数),如何处理?2023-07-10 3489

-

SOC设计中的建立时间和保持时间2023-08-23 440

-

ug内部错误,内存访问违例怎么解决2023-12-27 3299

全部0条评论

快来发表一下你的评论吧 !