FPGA开发要懂得使用硬件分析仪调试——ILA

电子说

1.2w人已加入

描述

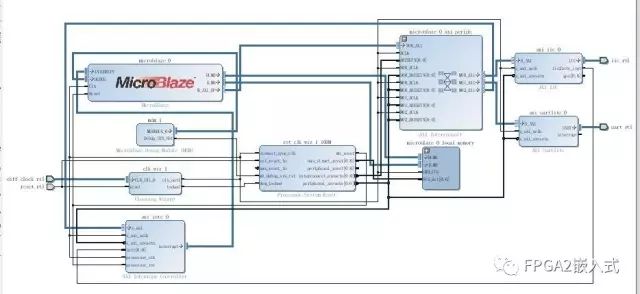

上一篇文章的介绍大家多少对ila核的使用有一些了解吧。在做纯逻辑的设计时,添加ILA核,然后在代码中进行定义就可以了。但FPGA已经不仅仅只是纯逻辑这么简单了,当你一个工程做到嵌入式层面,你就会使用软核,这时就会使用到画布。如下图所示,其中Microblaze就是一个处理器,可以看到各模块都是一个个IP核,我们无法对代码进行修改,如果这时我们要查看某个模块的端口改怎么办呢?不能在代码中定义一个ILA核呀!

其实这儿便很简单了,可以直接在画布上添加一个ILA核,再把想要的信号线连进来就行了呀,都不需要在代码里定义这个ILA核。不过这样做就说明你还没能灵活的使用Xilinx的在线调试工具了,因为还有更简单的办法哈哈。

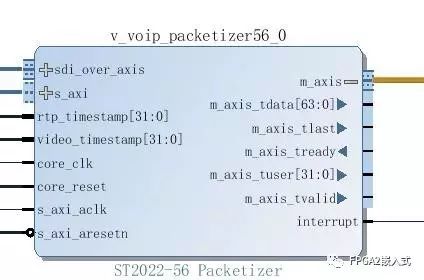

如下图所示,对于这个IP核,他的输出是axi_stream,我们如果想要查看他的工作时序该怎么做呢?

首先我们选择他的信号线,右键,就可以看到一个选项“Mark Debug”,选择后就会有一个绿色的甲虫出现,这时说明axi_stream所有信号都被引入到ILA中了。

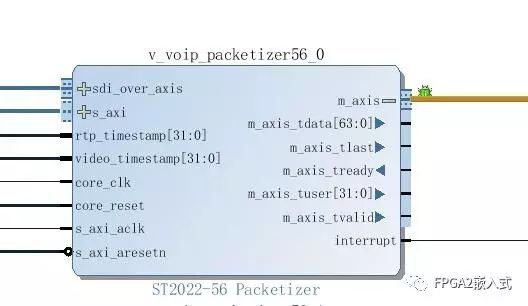

如果我们不想加入这个调试信号,直接右键,会有“Unmark Debug”选项,单击便会取消了。

然后在Vivado中点击保存,这样便完成了调试信号的添加了,是不是很方便。

这种方式大家先慢慢消化一下吧,后面再给大家介绍另一种调试方式,嘿嘿。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

巧用逻辑分析仪 助力单片机开发2012-03-22 0

-

玩转Zynq连载5——基于Vivado的在线板级调试概述2019-05-24 0

-

便携式逻辑分析仪电路设计2019-06-18 0

-

浅析逻辑分析仪的原理2019-06-28 0

-

如何用内部逻辑分析仪调试FPGA?2021-04-30 0

-

【正点原子DFPGL22G开发板体验】+ 使用在线逻辑分析仪进行调试2023-02-05 0

-

Vivado在线调试方法-Vivado内嵌逻辑分析仪器的使用2023-04-06 0

-

Vivado逻辑分析仪使用教程2023-04-17 0

-

如何利用ila(逻辑分析仪)调试nice?2023-08-16 0

-

TLA逻辑分析仪原理与应用硬件调试基础教程2009-10-17 643

-

TLA逻辑分析仪原理与应用 (硬件调试基础教程)2010-08-05 994

-

Vivado中关于ILA的详解2022-02-08 22433

-

Vivado之ILA详解2021-01-22 6578

-

集成逻辑分析仪(ILA)的使用方法2023-10-01 1757

全部0条评论

快来发表一下你的评论吧 !