资料下载

如何使用FPGA和DSP进行精度数字频率计的设计

本设计根据等精度的多周期同步测频原理,采用Altera 公司的FLEX10K10 系列FPGA 和TI 的TMS320VC5402进行硬件电路的设计。各项实测表明,多周期同步测频法是正确、合理和可靠的。

频率检测是电子测量领域的最基本也是最重要的测量之一,频率信号抗干扰强,易于传输,可以获得较高的测量精度, 所以测频率方法的研究越来越受到重视。本设计是以FPGA 为核心的等精度率数字频率计,采用TI 公司的TMS320VC5402 DSP 芯片和Altera 公司的FLEX10K10 系列FPGA,采用多周期同步测频原理,实现了高精度的恒误差频率测量,在使用过程中无需量程切换。经验证,产品性能稳定可靠,达到了较高的测量精度和测量速度。

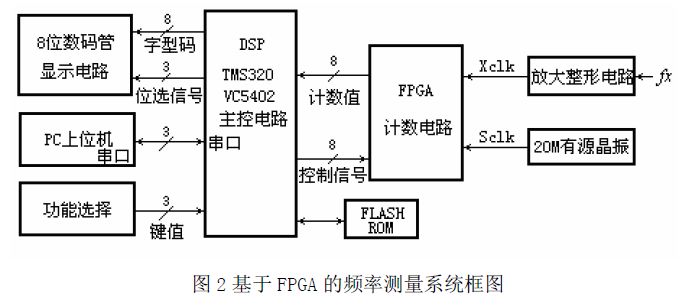

本系统可以完成频率、周期和占空比的测量,设计的总体电路如图2 所示,由DSP 主控电路、FPGA 计数电路、小信号放大整形电路、串口通信电路、数码显示电路和功能键选择组成。其工作过程是:根据功能键的判键结果(测频率、测周期还是测占空比),DSP 发出启动等控制信号和1S 的闸门,FPGA 完成对闸门的同步和在闸门时间内分别对标准信号和被测信号进行计数,然后将两组计数值(各32 位)分8 次送给DSP,DSP 完成数值转换和相应的浮点运算,最后将运算结果送8 位数码管动态显示。通过串口通信和上位机程序,测量过程也可以在PC 机控制下完成,并将测量结果送到PC 中记录,完成采集功能。

FPGA 程序设计

FPGA 程序框图如图 所示,由同步门D 触发器、标准信号计数器、被测信号计数器和64-8多路选择器构成。其中预置门控信号CL、清零信号CLR、数据输出选择SEL[2..0]由DSP 发出,FPGA 通过START 的下降沿通知DSP 计数结束,可以分8 次取数。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。 举报投诉

-

qjzyx

2019-02-13

0 回复 举报谢谢分享! 收起回复

qjzyx

2019-02-13

0 回复 举报谢谢分享! 收起回复

- 相关下载

- 相关文章