IC攻城狮求职宝典 02 2018年IC设计企业 笔试题 02 汇顶

今日头条

描述

1. 下面关于PLL电路表述正确的是:

A. PLL属于模拟电路,无法用全数字电路实现

B. PLL相对于参考时钟,可以输出分频、倍频、分数频的时钟

C. PLL输入的参考时钟jitter,在PLL输出是会变大,也有可能变小

D. PLL的jitter值等于同步数字电路中clock uncertainty的设定值

解析:jitter在线路传输过程中也会被改变。

2. 如图所示时序路径示意图,椭圆表示组合逻辑,FF1/FF2表示寄存器,A表示数据输入端口,CLK表示时钟输入端口,Z表示数据输出端口,下图选项描述正确的是:

A. 只要在端口CLK上创建时钟,即可约束A->Z之间的组合逻辑的延时

B. 只要在端口Z上设置输出延时,即可约束FF2 -> Z之间的组合逻辑的延时

C. 只要在端口CLK上创建时钟,即可约束FF1->FF2之间的组合逻辑的延时

D. 只要在端口A上设置输入延时,即可约束A->FF1之间的组合逻辑的延时

解析:

如上图所示,共有四条时序路径。

1:从输入端口A到FF1的D端;

要满足的时序要求为(其中Tsetup为寄存器建立时间要求):

Tclk - Tin_delay - T1 - Tsetup > 0;

故只要有了Tclk ,Tin_delay的的信息,EDA工具便可以完成对T1(A->FF1之间的组合逻辑的延时)的约束。

2:从FF1的CLK端到FF2的D端;

要满足的时序要求为(Tcq(寄存器输出延时),Tsetup(建立时间要求)):

Tclk - Tcq - T2 - Tsetup > 0;

故只要有了Tclk的信息,EDA便可以根据上面的要求去约束T2(FF1->FF2之间的组合逻辑的延时)。

3:从FF2的CLK端到输出端口Z;

要满足的时序要求为:

Tclk - Tcq - T3 - To_delay - Tsetup > 0;

其中Tcq(寄存器输出延时),Tsetup(为Z端口后面寄存器的建立时间要求)为工艺库有的信息,因此只要有了Tclk,To_delay(输出端口延时),EDA就可以去约束T3(FF2 -> Z之间的组合逻辑的延时)。

4:从输入端口A到输出端口Z。

对于A至Z之间的组合逻辑F的延时的约束。可以看到,A到Z端两边有寄存器。对于时序约束条件如下:

Tclk - Tin_delay -TF - To_delay - Tsetup > 0;

如果只是建立了clk,也就只是有了Tclk。而没有设置端口Z端的输出延时To_delay ,以及输入端口A端的延时Tin_delay故因此EDA不能完成对TF的约束。

3. 一个线性反馈移位寄存器(LSFR)的特征多项式为F(x)=x4+x+1,初始态为全1,则以下哪些描述是正确的?

A. 输出的m-序列为11100101

B. 该LFSR包含四个寄存器

C. 寄存器的状态不会出现全零

D. 该LFSR能够产生的不重复序列最长为15位

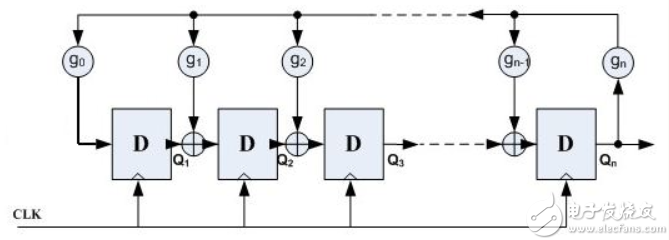

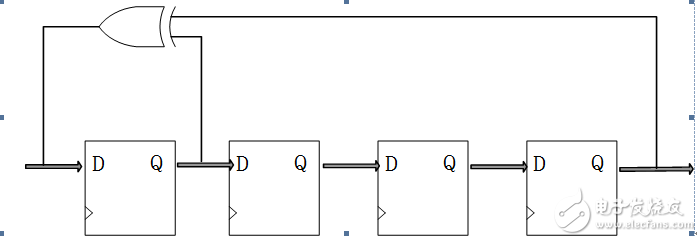

解析:LSFR如下,由n个D触发器和若干个异或门组成的。

多项式中的指数代表从左至右的抽头位。第一个和最后一个比特一般相应的是输入和输出位。故对于多项式F(x)=x4+x+1对应的电路如下:最开始第一个寄存器初始值为1。

故四个寄存器的输出随时钟节拍为:

1000 -> 1100 -> 1110 -> 1111 -> 0111 -> 1011 -> 0101 -> 1010 -> 1101 -> 0110 -> 0011 -> 1001 -> 0100 -> 0010 -> 0001 -> 1000。

故输出的序列为 0001111010110010。

4. 以下关于验证的描述,正确的是

A. 验证平台使用checker检测DUT的行为,只有知道DUT的输入输出信号变化之后,才能根据这些信号变化来判定DUT的行为是否正确

B. SystemVerilog区别于verilog的一个重要特征是其具有面向对象语言的特性:封装、继承和多态

C. UVM是synopsys、cadence、mentor等EDA厂商联合发布的验证平台

D. Verilog,SystemVerilog, SystemC, UVM 都是验证常用的硬件语言

解析:(1)checker是根据当前的输入值去判断输出值的正确性。(2)UVM由mentor发布。(3)UVM不是语言,而是一套验证系统。

- 相关推荐

- 面试题

-

华为笔试题大全(史上最齐全)2012-08-17 0

-

500强企业面试硬件笔试题2012-08-17 0

-

IC攻城狮们,2015最值得固化的是什么2015-12-31 0

-

IC攻城狮求职宝典2018-09-27 0

-

IC攻城狮求职宝典02-汇顶2018-10-18 0

-

IC攻城狮求职宝典08-地平线2018-12-13 0

-

IC攻城狮求职宝典05钜泉光电笔试题2018-12-14 0

-

求职宝典:寒武纪2019笔试题2018-12-24 0

-

【福利】给大家分享一些企业的测试和笔试题2018-12-26 0

-

IC攻城狮求职宝典 07 cadence笔试题2018-12-28 0

-

IC-ICE2QS02 Infineon高性能数字PWM2009-07-01 1337

-

硬件类笔试题(超齐全的笔试题)2015-10-28 1026

-

2014全志数字IC笔试题目2016-12-14 1543

-

WSTDW02E(锂电池保护IC)6-232017-07-28 1077

-

一线大厂的IC笔试复习题合集免费下载2020-09-08 1211

全部0条评论

快来发表一下你的评论吧 !