分频器的设计-奇偶分频

电子说

1.2w人已加入

描述

分频器的设计-奇偶分频

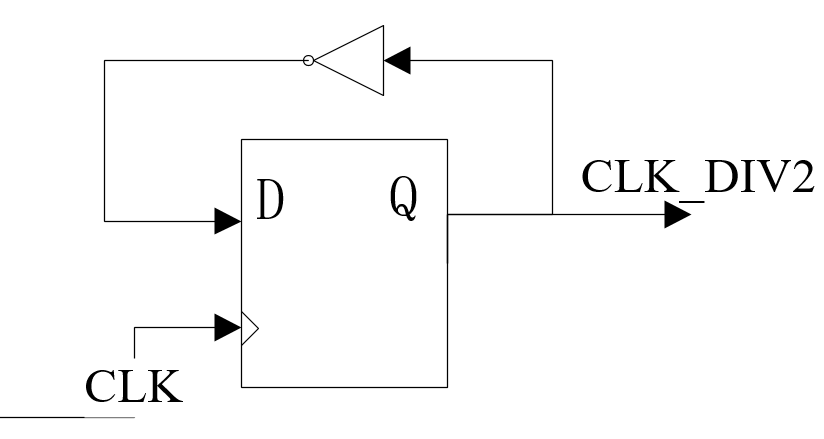

2的n次方分频实现

如下电路可以实现对CLK的2分频。原理很简单,上电复位先给寄存器一个初始值,然后只有在CLK上升沿CLK_DIV2才会翻转一次。故CLK两个上升沿之后,CLK_DIV2才完成两次翻转。

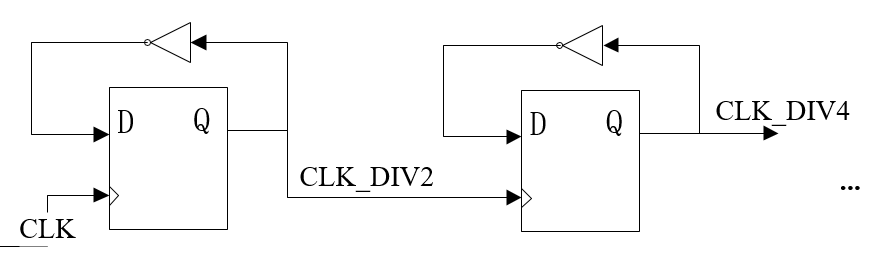

要实现2的n次方分频可以通过复用n次这个电路。如下所示。

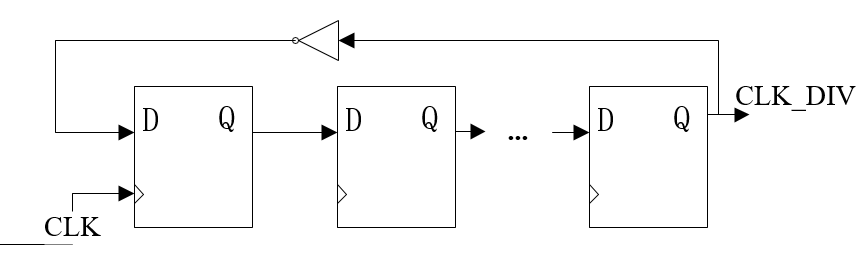

偶数倍分频

方式一:如下所示。通过移位寄存器实现分频。例如要实现2n倍分频,则需要用n个寄存器。

优点:不需要其它任何控制逻辑,只需要寄存器加一个反相器。

缺点:当分频倍数很大时,需要的寄存器也是倍增。当然你也可以采用复用的方式去减少所需寄存器数目,例如,36分频,可以做两个6分频器相连,则所需寄存器为6个,需要的寄存器数大大减少。

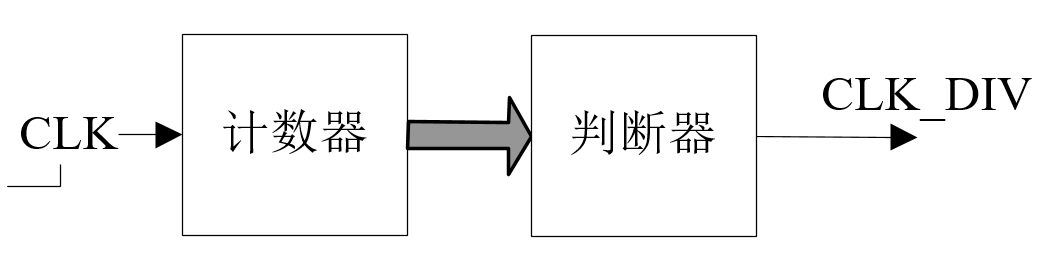

方式二:如下图所示,通过计数器来实现分频。比如,做一个2n分频器,则计数器计数从0到n-1,CLK_DIV就翻转一次。

代码如下(分频数为DIV_NUM=20):

仿真波形:

奇数倍分频

如上方式只能实现偶数倍分频,是因为寄存器都是源时钟CLK上升沿触发的,因此DIV_CLK只能在上升沿去发生跳转,这导致DIV_CLK必定只能是CLK的偶数倍分频关系(CLK跳转两次,DIV_CLK才可能跳转一次)。

奇数倍分频的一种实现方式如下。一路计数器用CLK的非CLK_N控制,一路用CLK控制。最后将两路的输出分频波形相亦或,得到最后的分频输出。如果难以理解可以对着最后的波形去看。

Verilog实现如下(分频数为DIV_NUM=9):

仿真波形如下:

思考

大家以上面的为基础,思考一下占空比可调的分频时钟的实现。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

#硬声创作季 分频器Mr_haohao 2022-10-21

-

跟大家聊聊分频器。 #Hifi #分频器 #发烧音响 #硬声创作季Hello,World! 2022-10-25

-

定阻型功率分频器的设计与制作(四)-分频器元器件的选取与制作2009-12-02 810

-

定阻型功率分频器的设计与制作(三)-二阶功率分频器2009-12-02 999

-

定阻型功率分频器的设计与制作(二)--一分频点的选择2009-12-02 709

-

分频系数可变的分频器2009-04-11 1231

-

具有奇次和偶次分频的分频器2009-04-11 894

-

什么是分频器 分频器介绍2010-02-05 3724

-

什么是分频器_分频器的主要参数(分频点、路、阶)2017-11-18 47092

-

分频器有哪些_分频器分类2018-01-10 10904

-

音箱分频器怎么接线_音箱分频器接线图解2018-04-13 111629

-

分频器是什么东西_音箱分频器的结构、特点2018-05-25 11678

-

一文解析主动分频器和被动分频器的优缺点2018-05-28 47480

-

音箱分频器的维修方法_音箱分频器怎么接喇叭2020-03-28 15140

-

FPGA学习-分频器设计2023-11-03 533

全部0条评论

快来发表一下你的评论吧 !