资料下载

高电源抑制比低压差线性稳压器的设计与研究

随着手机的不断普及和手机功能的不断增加,对电源管理的要求也更加复杂和严格。目前,电源管理集成电路市场大部分被国外产品占据,研究和开发国内的电源管理电路产品,能夺回巨大的市场。因此,开展本课题的研究具有特别重大的现实意义。

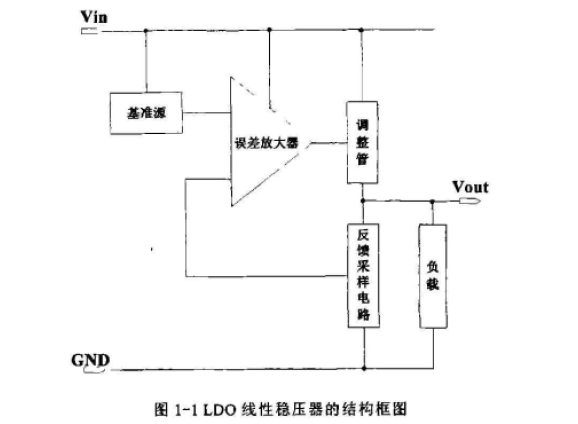

本文设计了一款高电源抑制比低压差线性稳压器芯片,它采用TSMC 0.6微米CMOS工艺设计,有良好的电源抑制比(低频超过90dB,高频40dB左右),支持较宽的输入电压范围(3.0V-5.5V),输出电压为2.8V, 在典型电流(150mA)情况下,压差为160mv.该电路主要用作对电源敏感的后级电路(如射频电路、VCO等)的电源电压。此外,芯片中还集成了过流保护电路和过热保护电路,保证电路的安全工作。基于以上技术优势,该芯片具有高电源抑制比、低输出噪声的特点,同时外围电路简单,大大降低了设计成本,适用于手机、数码相机、MP3播放器、PDA等手提移动设备的供电模块。

在本文中首先阐述了低压差线性稳压器的基本理论,包括基本工作原理和主要的电路指标;然后根据性能需要进行了深入的技术研究和完整的电路设计;最后详细分析并解决了低压差线性稳压器设计中的难点和关键点。借助设计软件Cadence和Spectra对电路进行了完整的设计和仿真,给出了合理的电路数据。仿真结果表明该电路实现了设计功能,达到了设计之初制定的设计指标。

最后对全文进行了 总结,并结合已经完成的研究内容提出了对下一步工作的展望。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。 举报投诉

- 相关下载

- 相关文章