以太网口模块的原理及布局布线原则

电子说

描述

一、以太网介绍:

以太网接口电路主要由MAC控制器和物理层接口(Physical Layer,PHY)两大部分构成,目前常见的以太网接口芯片,如 LXT971、RTL8019、RTL8201、RTL8039、CS8900、DM9008 等,其内部结构也主要包含这两部分。

一般 32 位处理器内部实际上已包含了以太网 MAC 控制,但并未提供物理层接口,因此,需外接一片物理层芯片以提供以太网的接入通道。

常用的单口 10M/100Mbps 高速以太网物理层接口器件主要有 RTL8201、LXT971等,均提供MII接口和传统7线制网络接口,可方便的与CPU接口。以太网物理层接口器件主要功能一般包括:物理编码子层、物理媒体附件、双绞线物理媒体子层、10BASE-TX 编码/解码器和双绞线媒体访问单元等。

模块示图:

A. RJ45和变压器合并示例:

B. RJ45和变压器分离示例:

实体图示:

二、布局布线原则

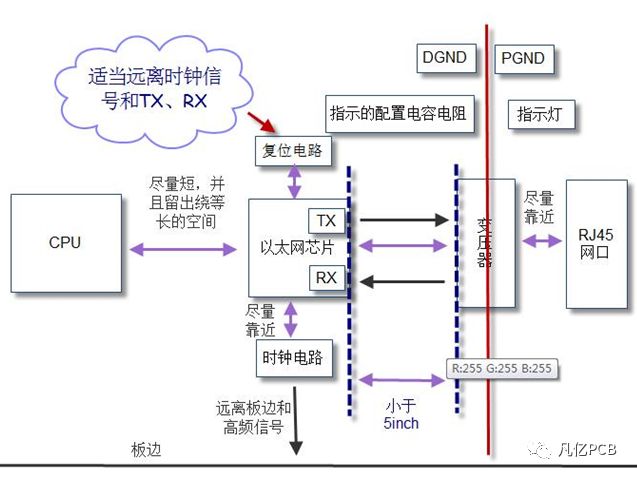

A.推荐布局原则:

1、RJ45和变压器之间的距离应尽可能的缩短。

2、复位电路信号应当尽可能的靠近以太网转换芯片,并且若果可能的话应当远离TX+/-、RX+/-和时钟信号。

3、时钟电路应尽可能的靠近以太网转换芯片,远离电路板边缘、其他高频信号、I/O端口、走线或磁性元件周围。

4、以太网转换芯片和变压器之间的距离也应该尽可能的短,以太网转换芯片和变压器之间的距离一般不要超过5inch(1 inch=1000 mil)。

5、每个电源管脚放置一个容值为0.1uf或者0.01uf的小电容,芯片周边每个电压应该最少有一个以上的大于4.7uf的大电容。

6、以太网转换芯片到CPU的距离也尽可能的短,并留出绕等长的空间。

7、一般RJ45网口插座旁边会更具结构要求放置LED指示灯,而RJ45插座这边一般只放置LED指示灯,将与LED指示灯相配置的电阻、电容或者磁珠放置在DGND区域,并注意在跨接线上放置桥接电容。

8、对交流端接的放置,如果以太网转换芯片的资料有布局要求(有的芯片会要求放置在以太网转换器端)就按照芯片资料完成布局;如果没有要求,一般情况下交流端接靠近以太网转换器边。

总体要求示意图:

PCB范例示意图:

B、推荐布线原则:

1、变压器下面所有层挖空(从变压器封装的丝印框就可以了,没必要挖到管脚)。

2、从变压器下面画出PGND和DGNS的隔离带、隔离带的最小宽度为80mil。

3、电源信号的走线(退耦电容走线,电源线,地线)应该保持短而宽。退耦电容上的过孔直径最好稍大一点。 每一个电容都应当有一个独立的过孔到地。

4、TX+-尽量走表层,对内等长约束为5mil。RX+-尽量走表层,对内等长约束为5mil,TX和RX没必要等长。走线长度差应当保持在 2cm 之内,Rx±最好不要有过孔, 并且布线在元件侧。

5、交流端接一般要经过电阻再连接到芯片或者变压器上,不允许有STUB的存在。

6、以太网芯片到CPU的GMII接口线的发送部分( GTX_CLKTX_ENTX_ERTXD[7:0])和接收部分(GRX_CLKRX_DVRX_ERRXD[7:0])要分开布线,不要将接收和发送网络混合布线、线与线直接的间距满足3W需要、RX和TX分别等长,等长范围在100mil。走线的长度不应当超过该信号的最高次谐波(大约10次谐波)波长的1/20。例如:25M 的时钟走线不应该超过 30cm,125M信号走线不应该超过12cm (Tx±, Rx±)。

7、有的变压器两端(特别是以太网信号来自背板插座)并没有将变压器两边的地分开,在这种情况下,变压器下面挖空是必须的。

8、有的变压器管脚分布,并不是常见的从一侧管脚输入,从另一侧管脚输出,而是同一侧的管脚上半部分是输入,下半部分是输出,在分割平面的时候一定要注意。

9、TX和RX走线间距满足4W(差分线宽和间距选大者)以上。走线要求如下图所示:

10、对于千兆以太网的信号线优先选择最优的信号层进行布线,过孔数量不要超过2个,换层时请在不超过200mil的范围内增加回流地过孔。

11、从变压器的PHY芯片的走线长度一般不超过12cm(大约5 inch)。

12、以太网模块的电源线要粗而直,滤波电容的放置位置和数量要合理。

13、有的原理图在电源部分增加了磁珠,磁珠要尽量靠近所提供的电源管脚,磁珠两边根据原理图或者设计要求增加电容,磁珠的布线要合理(一般采用铺铜和打过孔的方式)。

一般通用的法则,例如25M晶体下面不能走其它的信号线、时钟线不要走在RJ45插座下面,复位信号的布线要求满足3W要求等也要适用以太网的PCB板设计

电源和地的处理原则如下:

RJ - 45底盘接地和数字地通过一个1M欧姆的电阻和一个0.1uF的去耦电容应隔离。机箱地和数字地之间的差距,必须比60密耳宽。

图4 典型的机箱/数字地平面与磁集成单RJ- 45

图5 典型机箱/数字地平面分开的RJ - 45和磁所有的数字和模拟不同的电源电压的电源平面应隔离。

图6 典型的数字/模拟电源平面与磁集成单RJ- 45

图7 典型的数字/模拟电源平面独立的RJ- 45和磁

注:上述数字是数字电源(VCCxx)和模拟电源(AVCCxx)平面说明LAN电路板设计图。

以太网物理层接口器件过来的信号接往RJ45网口插座时需要注意:金属机壳以及与印制板相连的金属前面板应与印制板内部电路(包括信号和地线层)隔离至少 5mm 以上,印制板静电电流泄放通路的地应优先选择机壳地,板上的金属部件和金属接插件能就近接机壳的应就近接机壳,无法就近接机壳的接静电保护地环或工作地,工作地应是大面积的地层。

1. 晶体/振荡器的时钟源和数字信号的开关噪声应保持距离的MDI0 ±,MDI1 ±,MDI2 ± MDI3 ±差分对。此外,晶体/振荡器可漫步电容和其他信号的噪声敏感,最好是远离I / O端口,高频信号的痕迹,磁场,电路板的边缘,等部署的结晶。

2. 以太网磁应尽可能接近尽可能RJ - 45接口。

3. 千兆以太网PHY应放在尽可能接近的磁性。如果PCB的布局上有一定的局限性,从千兆以太网PHY的磁迹线长度不应该超过5英寸。

4.MDI0 ± MDI1 ± MDI2 ± MDI3 ±差分对应该尽可能接近路由。道间距D1之间MDI0 +和MDI0(或之间MDI1 +和MDI1,MDI2 +和MDI2,MDI3 +和MDI3)对应该在8〜10密耳。走线的宽度应相应调整,以产生所需的微量元素阻抗。

5.间距D2应大于200密尔。如果PCB的布局实在是难以满足这一要求,首长级薪级第2点的间距应尽可能大。

6.路线MDI0 ±,MDI1 ± MDI2 ± MDI3 ±差分对尽量伸直,并保持在差分对并行。

7.保持之间MDI0的走线长度的差异和MDI0(或之间MDI1 +和MDI1,MDI2 +和MDI2,MDI3 +和MDI3)一双700密耳内。

8.的终止电阻49.9Ω和电容的MDI0 ±,MDI1 ±,MDI2 ±和MDI3 ±差分对应该放在尽可能接近磁和跟踪应少于400密尔。

9.路线MDI0 ±,MDI1 ± MDI2 ± MDI3 ±差分对运行对称的,平等的长度,并尽可能接近。

10.避免使用过孔上的MDI0痕迹± MDI1 ±,MDI2 ± MDI3 ±差分对。如果PCB的布局确实需要使用差分对通孔,请匹配的通孔,以保持平衡差分对。

11.电源平面和数字地平面不应该划归磁性和RJ - 45接口。

12.直角,避免路由信号的跟踪,而不是,信号线应与多个45˚角路由。

MII 接口包含两种接口:SMII 和 SSMII

SMII 布局布线遵循下列原则:

1) TX_RXCLK 和 TX_RXSYNC 与其它信号间要求满足 3W 原则;

2) 收和发分为两组信号,每组信号间要尽量等长,走相同布线层,误差小于 100mil;

3) TX_RXCLK 优先采用带状线,布线尽量同层;

4) 保证所有信号有完整的参考地平面;

5) 布线的长度小于 10cm(不经过连接器);

6) 阻抗要求 50ohm +/-10%;

7) 布线拓扑:当端口数多于 1 个以上,TXD+/-一组信号和 RXD+/-一组信号分别并行走线

8) 过孔要求尽量少。

SSMII 接口布线遵循如下原则:

1) 走线一般要求参考 SMII 布局布线要求。

2) 一般驱动端的内阻为 17 欧姆,因此需要在驱动端串接 33 欧姆的电阻,此电阻离驱动端越近越好。

3) 线长要求:RX CLK 和 TX CLK 的长度差在 250MIL 以内。

4) 所有 INPUT 信号或 OUTPUT 信号,走相同布线层线长差必须在 200MIL 以内。

5) 所有信号的总长不能超过 15 英寸。

-

以太网接口在印制电路板上的实现2018-09-19 0

-

以太网是什么鬼?以太网基础知识详解电子学习 2023-02-07

-

车载以太网快速入门#车载以太网北汇信息POLELINK 2023-09-01

-

车载以太网基础培训——车载以太网的链路层#车载以太网北汇信息POLELINK 2023-09-19

-

RTC模块实用模块l;以太网交换机Piezoman压电侠 2023-12-11

-

PCB板布局原则、布线技巧2014-05-02 0

-

千兆以太网口防护方案2015-06-26 0

-

以太网口 的bob Smith电路2015-11-12 0

-

请大神指点一下以太网口RJ45的TX+ TX- RX+ RX-布线经验2019-12-18 0

-

高价回收新旧以太网模块-回收abcpu模块和ab以太网模块2021-06-30 0

-

PCB板基础知识、布局原则、布线技巧、设计规则2016-05-11 1232

-

PCB板布局原则、布线技巧(图解)2016-05-17 1832

-

以太网设计和布局2016-05-30 729

-

史上最全典型以太网口模块电路PCB设计2019-02-18 32693

-

以太网PCB布局布线2022-02-11 1210

全部0条评论

快来发表一下你的评论吧 !