一种基于FPGA的带死区的SPWM波形产生的设计与实现详解

模拟技术

描述

0 引言

PWM(Pulse Width Modulation)是通过调节输出波形的脉冲宽度来改变输出电压大小的一种调制方法,在交流传动、电力拖动系统和控制领域有着广泛的用途,但采用PWM调制技术在负载上的电流波形是非正弦波,这就使负载上具有很多的高次谐波成份,对系统的指标和稳定性造成很大的危害。正弦型脉宽调制(Sinusoidal Pulse Width Modulation,SPWM)是一种使输出的PWM波形按正弦的规律进行变化的技术,从而大大的提高了后级功率开关器件的稳定性和系统的效率。常见的SPWM波形产生方法主要有两种:一种是利用专门的SPWM产生芯片如TMS320 F2812来产生,这种方法的特点是一次可以产生6路或12路SPWM信号;另一种方法利用自然采样法的原理,采用数字或模拟方法产生三角波和正弦波,再使用比较器对产生的三角波和正弦波进行比较而得到SPWM波,这种方法产生SPWM波的路数比较灵活,电路原理简单,但具体实现比较复杂。

1971年3月,美国学者J.Tiemcy,C.M.Rader和B.Gold提出了从相位概念出发直接合成所需波形的一种新的频率合成原理,称之为直接数字频率合成器(DDS)。DDS技术是一种直接数字合成方法,不需要振荡和锁相环节,直接将波形函数进行离散化,以时间为地址,幅度为量化数据,依次存入波形存储器,使连续的数据流通过数/模转换器产生需要的波形。本文利用FPGA内部的DDS模块产生离散化的正弦波和三角波,进而产生数字的SPWM波形,再经过死区产生、脉冲消去处理后就得到了可以驱动后级功率放大管的驱动信号,利用该方法可以灵活的产生所需的任意调制比和载波比的SPWM波形,并且可以使负载上谐波含量大大减小,有效的保证了整个系统的稳定性。

1 SPWM波形的FPGA实现

根据SPWM自然采样法的原理,产生适合逆变器功率放大管所需的SPWM信号的电路主要包括正弦波产生模块、三角波产生模块、比较和死区产生模块和脉冲消去模块,它们之间的关系如图1所示。

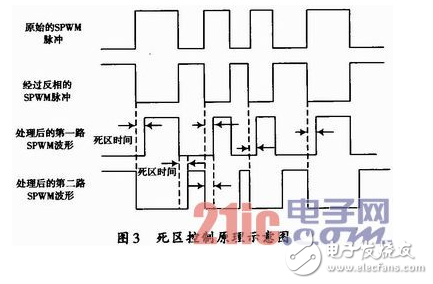

正弦波产生模块根据主控制器传来的频率控制字从ROM表中读出相应的正弦波的离散值,同样,三角波产生模块根据频率控制字从存储三角波的ROM表中读出三角波的离散值,比较器和死区产生模块根据传来的正弦波和三角波的离散值进行比较,直接进行比较产生上桥臂驱动信号,将正弦波离散值或三角波离散值加上一个特定的值或减去一个特定值再和三角波进行比较,产生上桥臂对应的下桥臂驱动信号,这时产生的信号已经是带死区的SPWM信号,再经过脉冲消去模块,消去功率器件来不及反应的窄的驱动信号,最后就可以得到直接驱动逆变器的一对SPWM信号。

1.1 波形产生模块

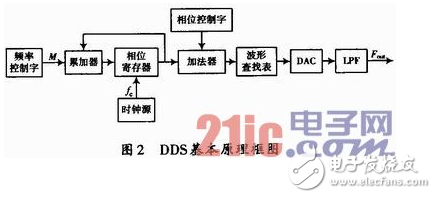

DDS技术是一种全数字的频率合成技术,是将已知的信号经过取样、量化,形成可供查询的数据表存于数据ROM中,通过改变频率控制字来改变输出所需频率的一种技术。如图2所示,DDS主要由频率控制字、累加器、相位寄存器、时钟源、加法器、相位控制字、波形查找表、DAC和LPF等模块组成。但因本设计不需要模拟信号,直接使用其中的数字信号,故不需要DAC和LPF模块,全部在FPGA内部数字化实现。数字三角波的产生和数字正弦波的产生一样,惟一不同就是在波形表中用量化后的三角波数据代替正弦波数据。

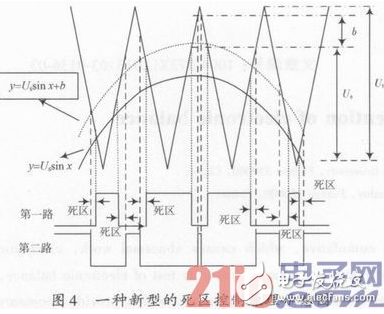

软件实现方法与脉冲消去方法大致相同,一般都是设计一个加减计数器,根据死区时间来确定加减计数器的最大值d,由计数器的最大值d来确定死区时间。这种实现方法是一般的实现方法,本设计提出了一种新型的死区产生方法,如图4所示,实线表示正常采用自然采样法的正弦波形和三角波形,正弦波y=Ussin x的半波的幅度为Us,三角波的幅度为Ut,根据自然采样法的原理,这里假定正弦波大于三角波时输出为高电平,小于时输出为低电平,根据正弦波和三角波的交点及电平输出的判断规则可以得到SPWM脉冲的第一路波形,这时把正弦波向上平移b个单位,如图4中的虚线,正弦波形y=Ussin x变为y=Ussinx+6,再根据自然采样法的原理用平移后的正弦波和三角波相交,根据交点判断输出高低电平,这样判断输出的电平高低就可以得到第二路的SPWM波形,生成了SPWM波形的死区,在本设计中采用的是数字方法产生SPWM,根据图4,可以在程序中按原来的方法产生第一路信号,把从ROM中取出的正弦信号加上b,再和原来的方波信号进行比较,这样就可以得到第二路SPWM信号,同样道理,也可以把三角波向上平移b个单位来产生第二路SPWM信号,但不管平移正弦波或三角波,都要保证平移后的正弦波的波形幅度要小于三角波的波形幅度。也可以设计第三个ROM,在程序外把经过向上平移后的正弦波形进行量化,存入ROM表中,在程序中用这个表和三角波的离散值进行比较,只是这样设计会增加FPGA硬件资源的消耗和增大存储器的存储空间。

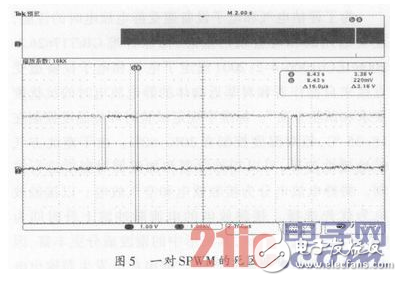

正弦信号往上偏移值b的确定是根据死区时间的值来确定的,这个值越大,则死区时间也越长,所以,可以调节b的值来增大或减小死区时间。一对经过死区处理后的SPWM波形如图5所示,从图5中可以看出,死区时间为16μs。

1.3 脉冲消去模块

在产生的SPWM脉冲中,完整的SPWM脉冲序列包含了占空为从0~100%的脉冲,因此有些脉冲的宽度可以达到非常小,而实际上,过窄的脉冲是无用的,因为在这样短的脉冲持续时间内,后级的功率放大管是不能完全导通或关断,只会增加功率器件的损耗,所以必须删除这些不良窄波;如图4所示,第二路的SPWM波形会出现比第一路SPWM波形小两倍死区时间的脉冲,如果某个脉冲已经在临界的宽度了,经过死区产生模块就会变成一个对后级的功率管来说过窄的脉冲,这也就是脉冲消去模块在死区模块后级的原因,它的作用是消去一些本来就有的和经过死区处理后的毛刺。处理后的波形如图6所示,图7为处理后的一对带死区的SPWM波形。

不论采用这种方法产生的SPWM波形,还是利用加减计数器的方法来产生SPWM波形,经过脉冲消去模块,都会存在输出的两路SPWM脉冲不对称性问题,如图7所示,就是有可能其中一路的波形缺失或所对应的另一路波形出现缺失,但这个问题可以在脉冲消去后再加一个模块进行处理而避免;对于载波频率变小时负载谐波变大的问题可以参考器件参数采用一定频率范围内的动态载波比和动态死区时间来解决。

2 结语

本文设计了一种基于FPGA的带死区的SPWM波形产生技术,对于SPWM的死区产生,一般都是应用加减计数器来实现,本文提出了一个新的选择,把死区产生模块融合到了比较模块中,利用波形平移技术,巧妙的产生了所要求死区时间的SPWM波形。生成的SPWM波形输出给后级的功率放大电路,检测系统负载上的电压和电流波形为较好的正弦波形,很好地满足了设计的要求。

-

用FPGA产生SPWM波形的程序2013-12-22 0

-

PWM死区波形2015-05-07 0

-

求一用STM32产生的SPWM波,有死区的2015-07-20 0

-

请问单相互补带死区时间的SPWM波,有没有例程参考?2018-07-23 0

-

怎样去设计一种基于自然采样法的SPWM波硬件产生电路呢2022-02-17 0

-

为什么CWG产生的波形没有死区2023-02-09 0

-

SPWM波形产生电路2009-03-06 10252

-

开关死区对SPWM逆变器输出电压波形的影响2009-07-10 2807

-

基于DSP2812的三相SPWM波形实现2011-09-22 1476

-

基于SA8382的单相SPWM设计与实现2011-09-22 2015

-

SPWM波形protues仿真程序 51单片机SPWM波形产生代2017-01-14 3229

-

spwm波形是什么 spwm波形的实现方法 生成spwm波形的实现方法2023-05-02 6209

-

生成SPWM波形的方法2024-02-06 588

全部0条评论

快来发表一下你的评论吧 !