影响产品ESD测试的主要因素是什么

描述

影响产品ESD测试的主要因素,总结为以下几点:机身材质、放电点与敏感线路的距离、放电点的静电流放电路径和阻抗、芯片本身的抗干扰能力、内外部结构、测试时的放置方式、散热器、直接注入情况下的防护措施。下面进行详细说明。

1、机身材质:导体(如金属机身)、绝缘体、喷有导电漆的绝缘体。不同外壳材质的产品,可以有不一样的放电路径,也就有不一样的影响。

2、放电点与敏感线路的距离:静电属于高频的干扰,放电时会有电磁场产生,距离近会有较大的寄生电容和较小的耦合阻抗,更容易被干扰。

3、放电点的静电流放电路径和阻抗:不同的路径造成不同的阻抗,不同的阻抗会产生不同的干扰。

4、芯片本身的抗干扰能力:这个应该包含几个方面,如芯片本身承受脉冲干扰而不发生逻辑错误的能力;外围电路的处理;与外部连接的布线。

5、内外部结构:主要是对于放电路径的影响。觉得了静电流是否会通过敏感电路。

6、测试时的放置方式:不同的的放置方式,有不同的放电路径,影响是不一样的。

7、散热器:很多时候散热器成为对CPU干扰的“路径”。

8、直接注入情况下的防护措施:如MIC、喇叭等在进行空气放电时会直接冲击信号线,如果此线路没有做防护,多数情况下会直接将芯片击穿毁坏。

散热器如何成为干扰路径分析

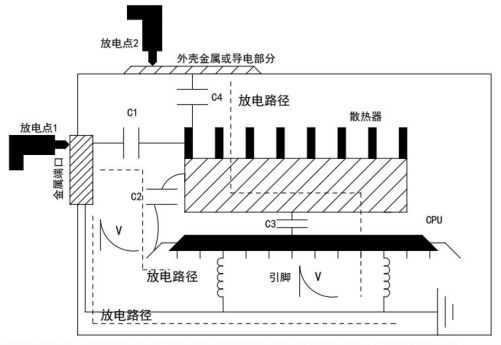

如下图所示:

放电点1和放电点2,都可以通过寄生电容C1和C4耦合到散热器上,散热器上面的静电又会通过C3和C2耦合到CPU内部和引脚上面,以及外围布线。CPU的引脚对于高频干扰来说,阻抗很大,将产生脉冲电压V。这个干扰电压将会造成CPU卡死或者逻辑转换。

总结:对于直接注入干扰,防护器件是必不可少的,RC滤波电路也是很有效的措施。对于间接耦合干扰;最大化减小寄生参数(电容和阻抗)以及尽量避免放电路径靠近敏感电路或通过敏感电路,是产品设计环节最重要的考虑;避免大环路的出现;采用屏蔽线缆。

-

影响SNR损失的主要因素有哪些?2021-03-11 0

-

请问影响绝缘电阻测量值的主要因素是什么?2021-04-09 0

-

请问影响电阻或电阻率测试的主要因素有哪些?2021-04-13 0

-

请问影响磨削变质层的主要因素有哪些?2021-04-20 0

-

请问PCB价格的主要因素有哪些?2021-04-21 0

-

影响超声波测厚仪测量示值的主要因素有哪些?2021-04-29 0

-

影响OTDR测试误差的主要因素有哪些?2021-04-29 0

-

影响绝缘电阻测量值的主要因素是什么?2021-05-08 0

-

选择测试设备时需要考虑的主要因素有哪些?2021-05-18 0

-

产生电弧的主要因素2021-09-16 0

-

决定仿真精度的主要因素2021-11-11 0

-

影响步进电机性能的主要因素有哪些?2023-03-10 0

-

影响手机待机时间的主要因素2009-12-19 335

-

浅析影响产品ESD测试的主要因素2018-10-04 6422

-

影响钻孔的孔位精度与孔壁品质的主要因素2022-09-06 2123

全部0条评论

快来发表一下你的评论吧 !