利用集成锁相环提高设计系统的频率性能

描述

锁相环(PLL)是电子系统中功能最多,最灵活,最有价值的电路配置之一,因此可用于许多应用。它用于时钟重定时和恢复,作为频率合成器,以及作为可调谐振荡器,仅举几个例子。结果,PLL存在于许多RF设备中,包括无线电接收器和测试设备。根据其具体实现,它可以从近DC到GHz和更高频率服务,在系统和电路中发挥许多关键作用。

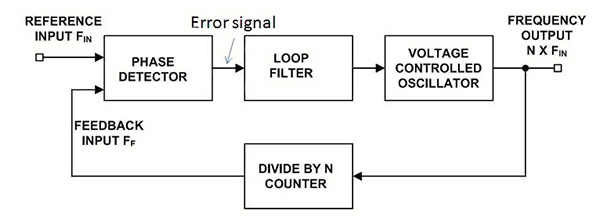

PLL是闭环(负反馈)架构,基本PLL由这些块组成(图1):

图1:基本PLL是闭环负反馈系统,其中参考信号和VCO输出之间的误差用于校正该输出;低通滤波器是建立环路动态的关键因素。

相位/频率检测器(PFD)(通常简称为相位检测器PD)将输入信号与参考信号进行比较信号并产生与其相位差成比例的误差信号(请记住,相位和频率密切相关,因为频率是相位的时间导数);相位检测器输出通常进入电荷泵,该电荷泵将小电流差转换为更大的电压

低通滤波器(LPF),其形成误差信号的频谱;这种滤波器的设计通常是工程科学和直观艺术的结合,是设置PLL操作的许多动态的主要因素。

具有输出相位/频率的压控振荡器(VCO)由误差信号控制

VCO输出端的可选分频器,使PLL产生参考频率的多因子N的频率; N可以是整数,并且许多PLL设计支持小数N非整数除法

VCO(和分频器,如果使用的话)的输出进入相位/频率检测器完成反馈循环。在操作中,误差信号随着相位差的增加而增加。这会以相反的方向驱动VCO相位,从而减少误差信号。结果,输出的相位被锁定到另一个输入的相位。

当PLL输出密切跟踪输入并且误差信号很小且相对稳定时,PLL被称为“锁相”或简单地“锁定”。根据应用,输出系统中使用的PLL系统的一个或者是VCO的输出,或者是VCO的控制信号。

PLL当然是在20世纪20年代左右使用真空管设计的。随着20世纪70年代推出的第一个大众市场PLL作为IC Signetics NE565(0.001 Hz至500 kHz)的运行,它们的受欢迎程度得到了显着提升。虽然这部分显然已经过时(并且Signetics早已不复存在),但其数据表已存档并可在线获取 1 。

PLL可以使用模拟,数字或混合构建信号电路。早期的PLL是全模拟的,具有模拟相位检测器,低通滤波器,VCO和可选的分频器;分频器很快升级为数字分频器,允许整数和小数整数除法。数字PLL现在用一个上下计数器代替相位检测器,该计数器在数字域中执行类似功能,也可以使用数字滤波器,误差信号驱动直接数字合成器作为VCO。

由于其内部结构的模块化,广泛使用和广泛的应用,PLL是莎士比亚或詹姆斯乔伊斯作品的工程对应物,因为它一直是无数文章,论文和书籍的主题。他们广泛分析了PLL的广泛定性讨论以及高度详细的定量模型;几乎所有这些分析都始于Gardner和Viterbi 2,3 的经典着作。

可用的技术论文涵盖了PLL的性能,其每个功能模块中存在多种噪声,抖动,漂移,非线性,失真和其他电路缺陷,以及多种输入的性能信号。其中包括检查时域和频域PLL操作的论文;一些专注于简单的一阶模型,而另一些则使用高度复杂的模型,捕捉PLL电路和信号的许多现实细微之处。

PLL参数满足应用目标

与大多数模型一样电子电路,有一些基本参数适用于几乎所有应用,有些在特定情况下更为关键。通过调整相位检测器,低通滤波器,VCO和分频器的一些设计细节,PLL设计可以在这些参数之间权衡性能,以最好地适应应用优先级。最重要的因素包括:

工作频率:PLL的标称自由频率及其VCO

工作范围:频率范围PLL和VCO将运行。这包括PLL可以获取信号并实现锁定的引入范围,以及一旦实现锁定就可以保持锁定的更宽范围

回转或捕获时间:所需的时间PLL在外部操作极限处获取并锁定信号,在很大程度上由低通滤波器决定;窄带宽滤波器具有更长的捕获时间但限制了噪声和抖动,而更宽带宽的滤波器具有更快的响应但允许更多噪声通过PLL系统

噪声和抖动:添加了任何噪声或抖动通过PLL的元件,即使有完美的信号,它也会出现在输出端。总体噪声品质因数(FOM)以dBc/Hz表示,并且有几种不同类型的FOM

死区:当相位/频率检测器的两个输入非常接近时,检测器可能没有看到这个,因此不会产生错误输出;这有点类似于电子滞后或机械静摩擦

许多其他因素也可能适用于不同应用中的PLL,例如无杂散动态范围(SFDR),失真,截距和温度系数;完整列表可能非常冗长。

PLL IC在频率,性能,集成方面不断提升

为了实现给定应用的最佳性能因素组合,PLL的用户将购买并连接单独的模块:阶段/频率检测器,定制滤波器,VCO和其他元件。当然,模块和混合设备的制造商很快就提供了完整的PLL作为完全特征化的单元,通过组合多个单独的IC芯片和分立元件。

然而,对更高频率的无线系统的需求,例如软件定义的无线电,智能手机,雷达系统和许多其他应用,一直是IC供应商开发流程和设计的动力。在高性能单片PLL中。其中许多功能块集成了大部分或全部功能模块(取决于频率和所需性能),从而减少了设计时间,风险,电路板空间和功耗。

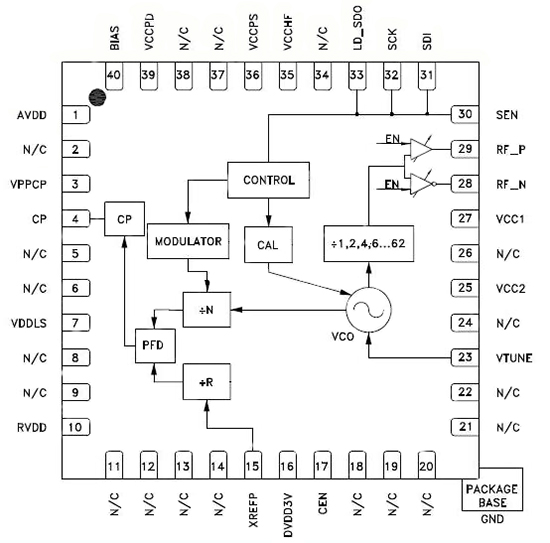

例如,Hittite的HMC830LP6GE PLL(现为ADI公司的一部分)是一款小数N分频PLL,工作频率范围为25 MHz至3 GHz。它针对蜂窝/4G基础设施,中继器和毫微微蜂窝基站以及通信测试设备,以及具有-110 dBc/Hz的超低带内相位噪声,-227 dBc/Hz的FOM以及低于180 fsec的均方根抖动的其他应用。

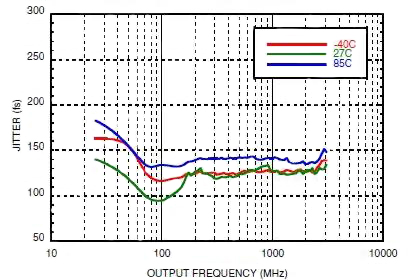

该IC包含一个集成的VCO(图2),传统上它是最难集成的功能,同时仍能在高频率下实现高整体性能。与大多数PLL一样,数据手册中有十几个详细的图表,显示了在各种条件下PLL的许多方面的性能。图3显示了在各种温度下PLL工作范围内的集成均方根抖动。

图2:ADI公司的HMC830LP6GE代表了最近几年:将VCO与PLL的其余部分一起放入IC,同时扩展频率范围,同时不影响品质因数。

图3:PLL数据手册通常有许多性能图,例如HMC830LP6GE的性能图,它显示rms抖动(fsec)与频率的关系,-40⁰C,27⁰C和85⁰C;注意这个宽范围内的性能稳定性。

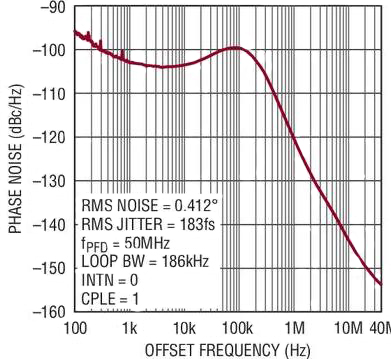

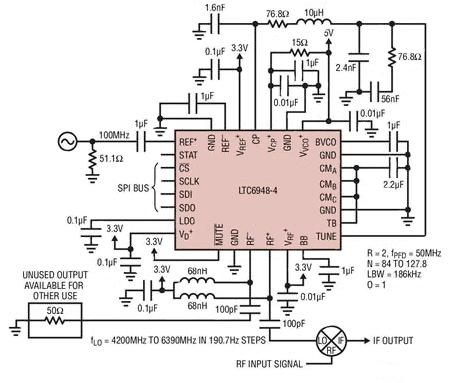

具有集成VCO的另一个PLL是凌力尔特公司的LTC6948,370 MHz至6.39 GHz小数N分频器,具有超低噪声。它还包括一个参考分频器,相位/频率检测器,电荷泵,分数反馈分频器和VCO输出分频器。归一化的带内相位噪声基底FOM为-226 dBc/Hz,宽带输出相位噪声基底为-157 dBc/Hz(图4)。

图4:其他参数中,凌力尔特公司的LTC6948数据手册包括归一化的带内相位噪声基底FOM和宽带输出相位噪声基底;后者在最高频率下从-100 dBc/Hz下降到-157 dBc/Hz。

它支持高达425 MHz的参考输入频率,用于快速频率切换。该IC非常适用于无线基站(LTE,WiMAX,W-CDMA,PCS)等应用;微波数据链路和军用/安全无线电,它可以用作高速,可调谐的6.39 GHz宽带接收机的核心(图5)。

图5:即使高度集成的IC也需要无源元件支持,因为这是一个高速,可调谐的6.39 GHz宽带接收器的原理图,基于LTC6948表示。

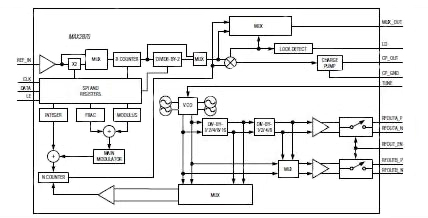

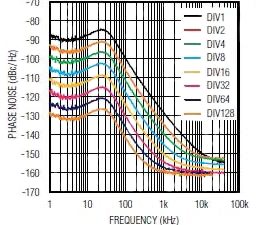

Maxim Integrated的MAX2870是一款23.5 MHz至6 GHz PLL,带有小数/整数N分频合成器和VCO(图6)。该器件通过多个VCO实现超宽频率,覆盖3 GHz至6 GHz,可自动选择或在用户控制下(通过串行接口);用户提供循环过滤器和参考。相位/频率检测器在整数N模式下工作在105 MHz,在分数N模式下工作在50 MHz,并接受高达200 MHz的参考频率。 PLL在多个分频器设置中表现出优异的6.0 GHz相位噪声性能(图7)。应用包括无线基础设施,测试和测量,卫星通信和无线局域网。

图6:Maxim Integrated的MAX2870通过以下方式实现了6 GHz的额定值使用多个内部VCO,可以自动选择或由用户主动选择。

图7:PLL供应商再次提供详细的性能规格,例如MAX2870在工作带宽内的相位噪声图,具有不同的分频因子。

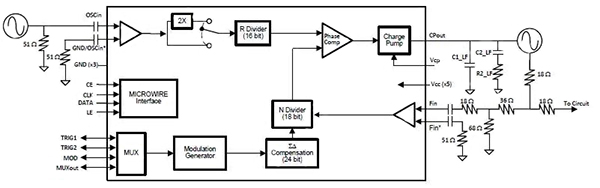

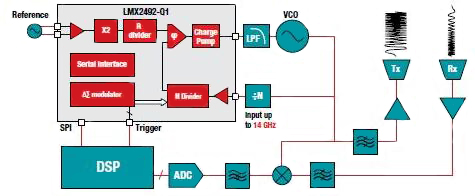

尽管德州仪器LMX2492分数PLL(图8),不包括集成VCO,它使用外部VCO在500 MHz至14 GHz范围内工作;其FOM为-227 dBc/Hz。当与合适的环路分频器结合使用时,它可以用作77 GHz汽车雷达系统的核心(图9);它还包括针对此重点应用的斜坡/啁啾生成。

图8:德州仪器LMX2492 PLL不包含VCO,但FOM为-227 dBc/Hz时性能达到14 GHz。/p>

图9:LMX2492针对77 GHz自动雷达等应用,具有雷达所需的积分斜坡和啁啾功能。

由于其200 MHz相位检测器响应,该PLL还可用于非雷达应用,如移动无线,紧凑型RF,雷达模块,微波回程,示波器,频谱分析仪,陆地移动无线电和软件定义无线电。尽管具有高频额定值,但IC的工作电压为3.15至3.45 V,功耗仅为60 mA。

除了RF性能之外,许多PLL现在还包括SPI或I 2 C串行接口,因此系统处理器可以设置和更改一些PLL参数,如增益,滤波器带宽或范围。这使软件能够在给定电路中调整这些因素以满足不断变化的情况,或允许在多个设计中使用相同的组件。

-

锁相环的原理,特性与分析2008-08-15 0

-

锁相环进行频率跟踪2014-06-23 0

-

锁相环在电力系统中的应用2015-01-04 0

-

求一款频率高的集成锁相环PLL!!!2015-07-30 0

-

锁相环常见问题解答2018-10-31 0

-

关于锁相环的组成你了解多少?2019-03-17 0

-

浅析低相噪Hittite锁相环产品2019-06-25 0

-

一种基于ADF4106的锁相环频率合成器应用实例介绍2019-07-04 0

-

SFS11000Y-LF锁相环2021-04-03 0

-

高频锁相环的可测性设计,不看肯定后悔2021-04-21 0

-

锁相环频率合成器是什么原理?2021-04-22 0

-

MCU锁相环的相关资料分享2021-11-04 0

-

锁相环控制频率的原理2022-06-22 0

-

集成锁相环频率合成器,什么是集成锁相环频率合成器2010-03-23 777

全部0条评论

快来发表一下你的评论吧 !