利用32位处理器和无线收发器实现物联网

描述

集成度和灵活性之间的平衡是物联网 (IoT) 中低成本无线节点的关键设计指标之一。 高度集成的超低功耗无线收发器在很多方面都有助于降低传感器节点成本,从而提供既能置于任何位置,又能回连至物联网的节点。

现在,许多无线收发器通过集成微控制器来处理无线堆栈,并且有众多不同的器件选择。 其中有些器件越来越多地增加额外存储器和处理能力,以运行小型代码块,这样做可以避免在无线节点中单独采用微控制器。 因此,可以节省空间、成本和功耗,使节点在小型电池供电下长期运行,并提高最终应用的灵活性。

对于物联网来说,象 IEEE802.15.4 ZigBee 之类技术就支持 2.4 GHz 网络的低成本无线节点,使用些技术可以连接到互联网,并能够通过互联网终端从全球任何地方安全地监视、控制单个设备。 云服务则提供可扩展控制机制,管理这些无线节点。 这种方法正在更多地用于如智能家庭、楼宇管理和安防系统等应用。

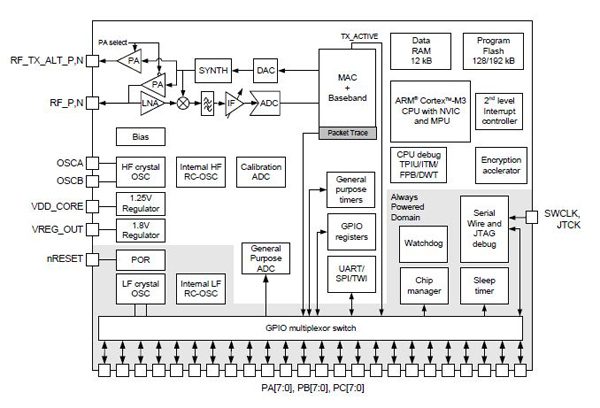

EM351 和 EM357 由 Silicon Labs 提供,是全集成片上系统,它集成了一个 2.4 GHz、符合 IEEE 802.15.4-2003 标准的收发器、32 位 ARM Cortex-M3 微处理器、闪存和 RAM 存储器,以及用于设计 ZigBee 型系统的各种外设。

图 1:Silicon Labs 的 EM35x 系列产品采用 ARM Cortex-M3 处理器来处理 ZigBee 无线协议堆栈和物联网的用户应用。

收发器使用高效架构,比 IEEE 802.15.4-2003 标准规定的动态范围高 15dB 以上。 集成式接收通道过滤功能允许在 2.4GHz 频段中与其它通信标准稳定共存,例如 Wi-Fi 和蓝牙。 集成式稳压器、VCO、环路滤波器和功率放大器有助于保持较少外部元件和较低成本。

ARM Cortex-M3 集成内核针对高效存储器使用进行了优化,并提供两种不同的运行模式:特权模式和用户模式。 这样,就可将网络堆栈与应用程序代码分离,以避免意外修改存储器和寄存器的受限区域,从而提升已部署解决方案的稳定性和可靠性。

EM351 和 EM357 分别具有 128kB 和 192kB 嵌入式闪存。 这两款芯片均采用 12 kB 集成 RAM 存储数据和程序,内置软件则采用可优化嵌入式闪存使用寿命的高效率损耗均衡算法。 这是一个关键考虑点,因为无线节点的使用寿命超过 10 年,同时还应考虑闪存单元的损耗情况。

为满足 ZigBee 无线连接规定的严格定时要求,该器件在硬件中集成了许多 MAC 功能、AES128 加密加速计和自动 CRC 处理功能。 MAC 硬件可执行自动 ACK 发送和接受、自动回退延时和发送前的空闲信道评估,以及自动过滤接收到的数据包。 此外,数据包跟踪接口与 MAC 集成在一起,从而能完好无损地够捕获发送至或来自开发工具的所有数据包。

EM35x 无线接收器是一款低 IF、超外差接收器,能够采用差分信号路径降低对噪声干扰的灵敏度。 经 RF 放大后,信号由图像抑制混合器进行下变频处理,然后由 ADC 过滤后再进行数字化。 接收器的数字部分采用一个相干解调器,为基于硬件的 MAC 生成各种符号。 数字接收器也包括模拟无线电校准程序,并控制接收器路径中的增益。

MAC 将片上 RAM 与 RX 和 TX 基带模块连接起来。 MAC 提供基于硬件的 IEEE 802.15.4-2003 数据包级过滤功能。 它可提供精确的符号时基,这种时基能最大限度减少堆栈软件的同步工作并满足协议定时要求。 此外,还能为 IEEE 802.15.4-2003 CSMA-CA 算法提供定时器和同步辅助。

该器件采用二十四个与其它外设或替代性功能共享的 GPIO 引脚,以连接外部数字传感器或控制器。 集成的串行控制器 SC1 经过配置后可用于 SPI(主机或从机)、TWI(仅主机)或者 UART 工作模式,而串行控制器 SC2 经配置后可用于 SPI(主机或从机)、TWI(仅主机)工作模式。

EM35x 系列具有通用 ADC,能够针对模拟传感器在单端或者差分模式下在六个 GPIO 引脚上采样。 ADC 采用 DMA 模式捕获采样数据并自动发送至 RAM,然后集成的微控制器就能轻松访问这些数据。

电源是物联网中无线节点的一个关键点,EM35x 器件具有超低功耗、深度休眠状态以及各种可选时钟模式。 睡眠定时器可从外部 32.768 kHz 晶体振荡器计时,或从内部 10 kHz RC 振荡器衍生出的 1 kHz 时钟计时。 还有一种方法是,为达到最低功耗模式禁用所有时钟。 在最低功耗模式下,只有 GPIO 引脚上的外部事件才可唤醒芯片。 EM35x 具有快速启动时间(通常 110 μs),即从深度睡眠快速唤醒并执行第一条 ARM Cortex-M3 指令。 将该处理器集成到设备中,可直接控制所有的功率域,进而达到应用的最小功率包络。

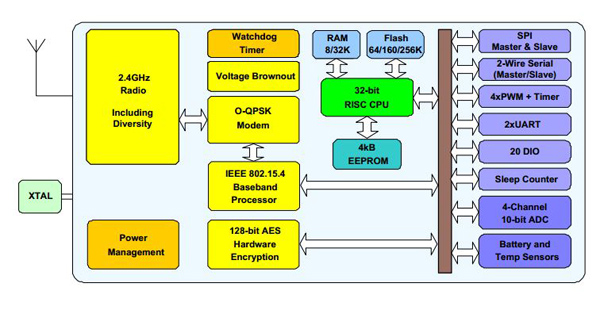

JN516x(NXP Semiconductor 产品)采用了不同的微处理器集成方法,它集成了 2.4 GHz 无线电、一个调制解调器、一个基带控制器和一个安全协处理器。 该器件采用了允许在芯片上运行软件的定制式 32 位负载/存储 RISC 内核,且由 IEEE802.15.4 MAC 协议、其它更高层协议和用户应用共同分担处理功能。

JN516x 采用统一存储器架构,并把代码存储器、数据存储器、外设器件和 I/O 端口全部组织在同一个线性地址空间内,以简化代码开发和调试工作。 该器件包含高达 256 KB 的闪存、高达 32 KB 的 RAM 和 4 KB EEPROM。

图 2:JN516x 采用定制 32 位负载/存储 RISC 处理器内核来处理线性地址空间内的 ZigBee 协议堆栈和用户应用。

该 CPU 采用能够和无线收发器一起集成的架构,以使电池供电型应用实现低功耗,并提供足够的性能来供执行无线协议;与此同时,为混合型应用和高级语言的有效编码(如 C 语言)提供了软件开发者套件。

该 CPU 可以访问一批十五个 32 位通用 (GP) 寄存器以及少量专用寄存器(用于存储处理器状态信息和控制中断处理)。 任何 GP 寄存器的内容都可从存储器加载或保存其中,而算术和逻辑操作、移动和旋转操作、签名和非签名比较操作可在两个寄存器之间执行并在第三个寄存器中存储,或者在寄存器间执行而常数携带在指令中。 通用或专用寄存器的操作在一个周期内执行,而访问存储器则还需一个周期,以等待存储器响应。

指令集控制 8、16 和 32 位数据,也就是说,程序能够非常高效地使用这些长度的对象。 32 位长度操作能力对协议和高端应用尤其有用,可使算法的执行指令少于小型字处理器且在较少的时钟周期内执行完毕,从而实现节能。 这种内核也支持可用于高效执行 DSP 算法的硬件乘法器块。

该 CPU 架构还包括一些特性,能使处理器适合那些需要在处理器上执行个多任务的嵌入式、实时应用。 为保护设备范围内的资源,处理器可在监督或用户模式下运行,允许访问所有的处理器寄存器或仅访问 GP 寄存器。 监督模式在复位或中断后进入,而任务启动则通常在 RTOS 环境的用户模式下运行。

总结

将 32 位处理器和无线收发器集成在一起,能增强成熟、稳健型网络堆栈和用户应用的性能,从而减少物联网中无线节点的材料成本和功耗。 利用定制内核(如 JN516x)或业内标准内核(如 EM35x 器件)即可实现上述目标。 在这两个示例中,集成内核允许无线收发器块和内核的功率域均通过代码管理,从而降低总体功耗,延长电池寿命。 这样,便能在无线节点使用寿命内减少维护和电池更换次数,节约运营成本。

-

详析32位嵌入式处理器与8位处理器应用开发的三大不同2016-08-08 0

-

两种ARM 64位处理器学习平台2016-10-26 0

-

32位嵌入式处理器与8位处理器应用开发有什么不同?2017-04-06 0

-

32位嵌入式处理器与8位处理器应用开发的三大不同点2017-06-02 0

-

32位处理器S3C44B0怎么移植?2019-08-19 0

-

如何将FIFO连接到我的16位处理器2020-06-02 0

-

32位处理器可以装64位系统吗 32位处理器能否装64位系统分析2020-06-28 0

-

32位处理器的开发与8位处理器的开发有哪些明显的不同?2021-04-19 0

-

何谓32位处理器2021-07-13 0

-

MT7628处理器是什么2021-07-22 0

-

mt7628处理器2021-07-30 0

-

为什么说8086是16位处理器2021-08-06 0

-

RK3566四核64位处理器有哪些特点及其功能呢2022-03-02 0

-

Sitara AM62处理器的资料分享2022-11-03 0

全部0条评论

快来发表一下你的评论吧 !