分析影响PCB阻抗的主要因素和阻抗影响不同程度

电子说

描述

摘要:通过对不同线宽、不同介质厚度、不同介电常数变化、线路层棕化、线路补偿等影响因素研究,分析影响PCB阻抗的主要因素和阻抗影响不同程度,为PCB高精度阻抗设计提供最佳建议方案。

0

前言

在IC(集成电路)集成应用中,装配后的PCBA(印制电路板组装件)信号传输频率(发射)高到某一定值后,将受到PCB导线本身的影响,从而导致传输信号的严重失真或完全丧失。这表明在高集成PCB导线所流通的不是电流,而是方波讯号或脉冲在能量上的传输,这种讯号传输时所受到的阻力称之为“阻抗”。特别是在电子通信业对高频、高速信号等技术的快速推广及运用背景下,客户对PCB的要求不仅仅是满足物理性能,对PCB电气性能的要求日益增加,如7%、5%阻抗公差,插入损耗控制等等。PCB制造业面临的挑战也不仅仅是加工工艺能力的考验,更多将是对设计能力的考验。由此可见,阻抗在IC高度集成化的PCB应用中越来越重要。

1

试验方法

1.1 设备与材料

设备:CITS900S4 Polar阻抗测试仪;TEKTRONIX阻抗测试仪。

材料:规格为1080、2313、2116、7628的半固化片;0.10 mm内层芯板。

1.2 试验项目

(1)不同线宽对单线阻抗、差分阻抗的影响;

(2)不同介质厚度对单线阻抗、差分阻抗的影响;

(3)不同εr(介电常数)变化对单线阻抗、差分阻抗的影响;

(4)介质厚度管控之阻抗条和单元内阻抗控制区残铜率的影响;

(5)线路层棕化(或黑化)对阻抗值的影响;

(6)线路补偿对阻抗的影响。

2

结果与讨论

2.1 线宽变化对单线阻抗、差分阻抗的影响

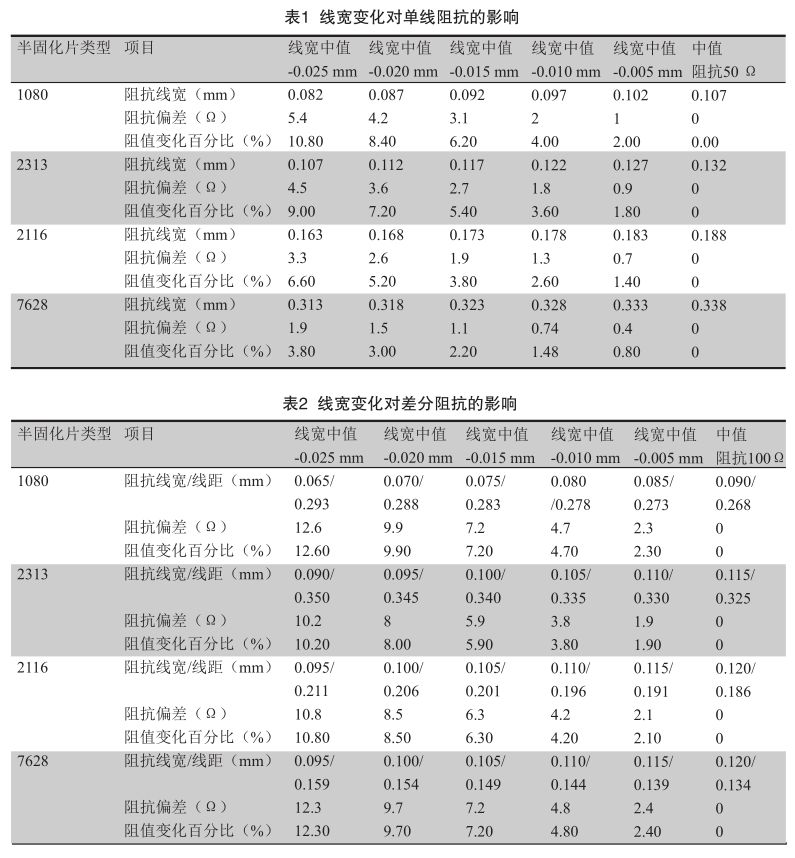

线宽控制是影响PCB阻抗控制精度的重要因素。采用不同半固化片、阻抗线宽测试对阻抗的影响,如表1、表2所列。

半固化厚度越厚,线宽的宽度变化对阻抗值的影响越小。半固化厚度越薄,线宽的宽度变化对阻抗值的影响越大。特别是介质层中如果使用单张1080或更薄的半固化片作为阻抗线的介质层时,需要特别注意管控阻抗线宽的波动范围。

2.2 介质厚度对单线阻抗、差分阻抗的影响

介质厚度对阻抗精度有很大的影响,介质厚度包括芯板的介质层厚度和半固化片压合后的厚度。采取不同半固化片和介质厚度分析对阻抗的影响,如表3、表4所列。

介质层厚度越薄,介质层厚度的波动对阻抗线阻值的影响越大;介质层厚度越厚,介质层厚度的波动对阻抗线阻值的影响越小;特别是介质层中如果使用单张1080或更薄的半固化片作为阻抗线的参考层对应的介质层时,需要特别注意管控此介质层厚度的波动范围。

2.3 不同ε(介电常数)对单线阻抗、差分阻抗的影响

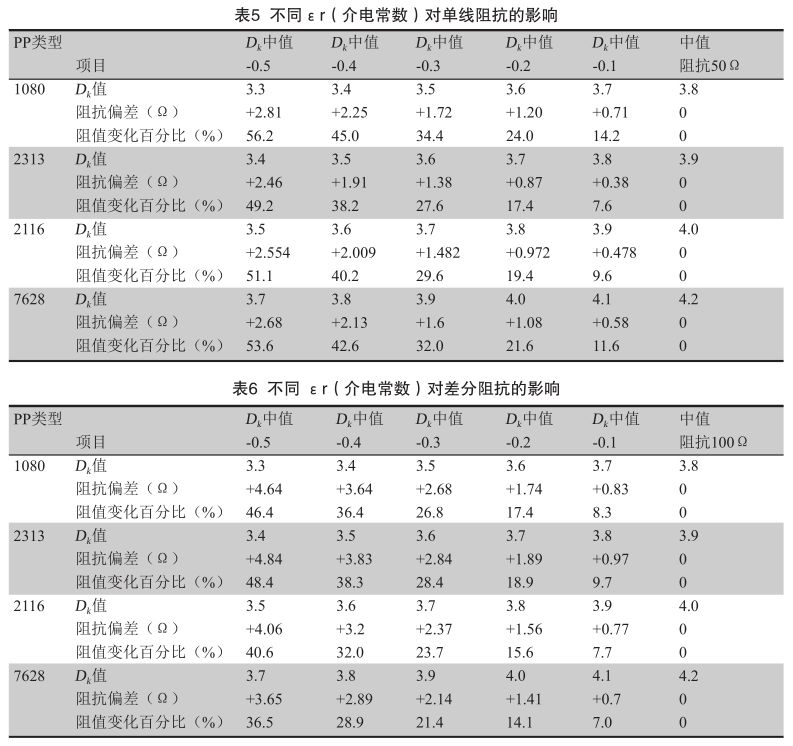

采取不同半固化片的介电常数分析对阻抗的影响,如表5、表6所列。

介电常数每变化0.1时,对单线阻抗线阻抗值的影响约为10%;对差分阻抗线的阻抗值影响约为8%。

2.4 介质厚度管控之阻抗条和单元内阻抗控制区的残铜率对阻抗的影响

介质厚度=半固化片厚度-铜厚*(100%-残铜率),因此,在相同半固化片结构下,影响介质层厚度的其中一个主要因素为残铜率,而残铜率与Gerber图形设计相关联。因此要区分阻抗线所在位置的残铜率大小。

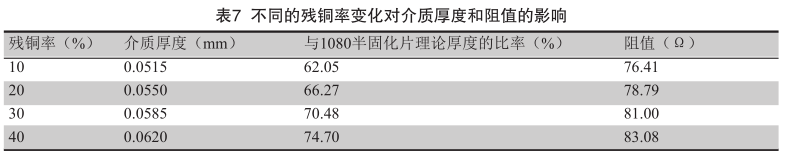

以下为不同残铜率对介质厚度的影响度。以1080半固化片的理论厚度0.083 mm,内层铜厚35 μm为例,不同的残铜率变化对介质厚度的影响度如表7所述。

从表7可知,残铜率每改变10%,介质厚度将改变4.2%,对差分阻抗线宽/线距(0.10 mm/0.152 mm)的阻抗值影响度为2.08~2.38 ohm。若阻抗中值为76 ohm,阻抗公差按±10%(7.6ohm)管控,则残铜率每改变10%时,对阻抗值偏差的贡献度为26%~31%。

为了让阻抗测试专用测试板上的阻抗值(CITS900S4 Polar阻抗测试仪只能使用专用测试板)更接近于单元内的阻抗值,在工程设计时阻抗测试板与单元内的残铜率应尽量保持一致。当阻抗测试板的残铜率与单元内的残铜率极差达到5%以上时,阻抗测试板上的阻抗线宽设计与单元内的阻抗线宽设计需分开制作。如图1这种阻抗线分布的情形,在计算残铜率时不能按整个单片的面积大小来计算残铜率,而应该根据阻抗线分布的区域铜面范围来计算残铜率。

2.5 内层芯板棕化对阻抗值的影响

为了增加内层铜面与半固化片的结合力,压合之前需要对内层图形做棕化或黑化。通过对铜表面进行微蚀,同时对阻抗线也会作相应的蚀刻处理,经切片分析棕化前与棕化后将有3 μm~5μm的线宽减少量。对于精细密的阻抗线的阻抗值影响约3.1Ω。棕化微蚀对阻抗值的影响度比重占阻抗公差的30%以上,因此,工程在阻抗线补偿时需要增加棕化补偿(通常是补偿值的1/4),内层铜厚为35 mm时正常补偿0.02 mm后再加补0.005 mm。

2.6 线路补偿对阻抗的影响

图2是高亮显示的阻抗线,如果补偿量与其他板内的线一样进行补偿,因其分布在相对独立的区域,蚀刻后的板容易出现局部阻抗线线幼的问题,阻抗会局部偏大。

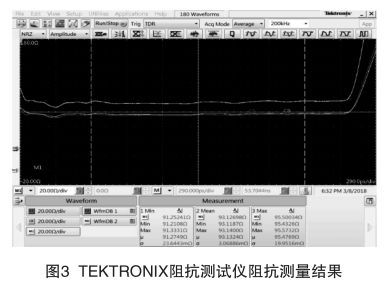

图2高亮显示的阻抗线工作稿设计线宽/线距为0.094 mm/0.109 mm,目标管控阻抗值(85±8.5)Ω。使用TEKTRONIX阻抗测试仪测量板内此组阻抗线,阻值为91.25Ω~95.5Ω,最大值超出阻抗管控规格,同时阻抗值的波动范围为4.25Ω,如图3所示。

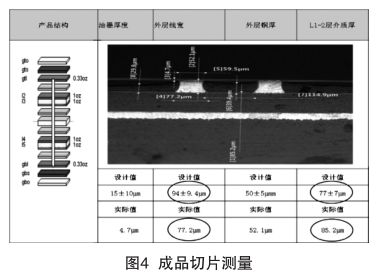

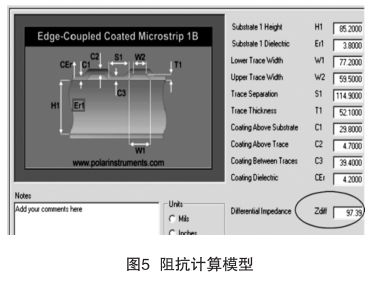

从切片数据(图4)分析来看,在各项影响阻抗值的因素中,外层线宽超出管控值的下限,介质厚度超出上限,其它可能产生变异的因素数据相对比较稳定,从阻抗分析的影响因素来看,主要是线幼和介质层超厚导致阻抗偏大。

将外层切片数据代入阻抗计算模型,如图5所示。对阻抗各影响因素进行层别分析,可以发现,当介质层很薄时,阻抗线宽对阻值的影响度很大。因此,在工程设计时对不同的阻抗线宽应进行区分补偿,特别是密集区、稀疏区、独立区应该进行分段补偿。即使是同一组线或同一根线,也需要按其在PCB上的区域分布进行区分补偿,这样才能使阻抗值的波动范围尽量的减小。

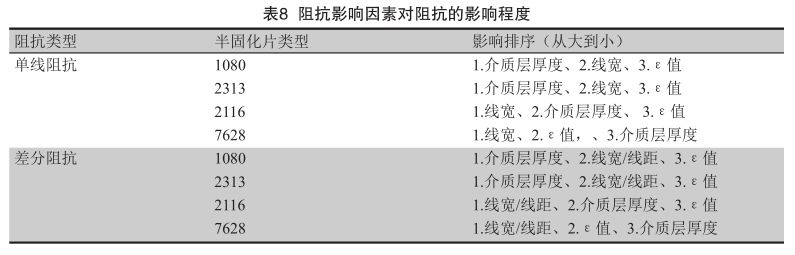

2.7 小结

通过上述试验和分析,影响PCB阻抗的主要因素和阻抗影响不同程度,如表8所列。

3

结论

通过上述试验和分析,高精度阻抗在设计时应根据不同半固化片类型来管控阻抗,建议管控方案如下:

(1)当半固化片的厚度越薄时,需要管控介质层厚度的波动范围,主要从阻抗线的图形分布,来确定残铜率的计算。

(2)当半固化片的厚度越薄时,需要管控阻抗线宽的波动范围,主要从阻抗线的图形分布,来确定分段补偿的方式。同时对于内层阻抗,根据棕化前处理的微蚀量对阻抗线宽进行补偿。

(3)当ε值偏离真实的ε值达到0.5时,对阻抗值的公差范围影响度接近50%,因此在实际生产中,应根据实际生产结果来反推ε值,让ε值稳定在0.1的波动范围。

-

影响SNR损失的主要因素有哪些?2021-03-11 0

-

请问影响绝缘电阻测量值的主要因素是什么?2021-04-09 0

-

请问影响磨削变质层的主要因素有哪些?2021-04-20 0

-

请问PCB价格的主要因素有哪些?2021-04-21 0

-

影响OTDR测试误差的主要因素有哪些?2021-04-29 0

-

影响绝缘电阻测量值的主要因素是什么?2021-05-08 0

-

选择测试设备时需要考虑的主要因素有哪些?2021-05-18 0

-

决定仿真精度的主要因素2021-11-11 0

-

影响步进电机性能的主要因素有哪些?2023-03-10 0

-

PCB加工中影响阻抗因素2006-04-16 2203

-

Cadence PCB SI分析特性阻抗变化因素教程2010-03-21 3336

-

PCB设计阻抗不连续的解决办法2020-12-27 4258

-

影响电缆特性阻抗的主要因素都有哪些2021-01-19 6416

-

影响放大电路高频特性的主要因素2023-09-18 1943

-

影响阻抗的因素有哪些?阻抗线都有哪些类型?2023-10-30 2612

全部0条评论

快来发表一下你的评论吧 !