资料下载

高速电路信号完整性分析与设计PDF可复制版电子书免费下载

网上曾报道一则技术消息,美国一家著名的影像探测系统制造商的电路板设计师们曾经碰到一件奇特的事:一个7 年前就已经成功设计、制造并且上市的产品,一直以来都能够非常稳定可靠地工作,而最近从生产线上下线的产品却出现了问题,产品不能正常运行。这是一个20MHz 的系统设计,似乎无需考虑高速设计方面的问题,没有任何的设计修改,采用的元器件型号同原始设计的要求一致。

系统缘何失效?这让设计工程师们觉得十分困惑:没有任何的设计修改,生产制造基于原始设计中一致的电子元器件。唯一的区别是由于今天不断进步的IC 制造技术,所以新采购的电子元器件实现了小型化也更加快速。新的器件工艺技术使得新近生产的每一个芯片都成为高速器件,正是这些高速器件应用中的信号完整性问题导致了系统的失效。随着IC 输出开关速度的提高,信号的上升和下降时间迅速缩减,不论信号频率如何,系统都将成为高速系统并且会出现各种各样的信号完整性方面的问题。

高速数字电路方面的问题突出体现为以下的类型:1)时序问题总是第一位的,工作频率的提高和信号上升/下降时间的缩短,首先会使设计系统的时序容量缩小甚至出现时序方面的问题。2)传输线效应导致的信号震荡、过冲和下冲都会对设计系统的故障容限、噪声容限以及单调性造成很大的威胁。3)信号沿时间下降到1ns 以后,信号之间的串扰就成为很重要的一个问题。4)当信号沿的时间接近0.5ns 时电源系统的稳定性问题和电磁干扰(EMI)问题也变得十分关键。

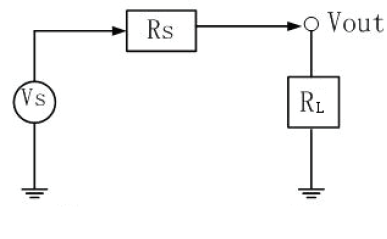

什么是高速数字信号?高速信号是由信号的上升边沿速度决定,Tr 为信号上升时间;Tpd 为信号线传播延时:

对于落在不确定区域及问题区域的信号,会出现信号质量的突变。一般认为上升时间小于4 倍信号传输延迟时可视为高速信号,应该使用高速数字电路和高速数字布线的方法。

在高速脉冲作用的情况下,研究高速电路系统互连和封装结构和半导体单元电路通过接口构成的整体系统的电特性分析。信号完整性(Signal Integrity,简称SI)是信号在电路中能

以正确时序和电压做出响应的能力。通俗地说,可以理解为信号的质量。信号完整性问题的影响主要包括:接口反射、串扰、地平面反弹噪声、EMC/EMI 和电源完整性等等。IC 开关速度高、端接元件的布局不正确或高速信号的错误布线都会引起SI 问题。随着电子技术和计算机技术的发展,信号速率不断提高。近年来,随着高速电路的迅速发展,高速芯片和器件越来越被广泛使用,信号完整性问题变得越来越突出,越来越引起关注。高速数字信号完整性是表明信号通过信号线传输后仍保持其正确的功能特性,信号在电路中能以正确的时序和电压做出响应,由IC 的时序可知,如果信号在稳态时间(为了正确识别和处理数据,IC 要求在时钟边沿前后输入数据保持不变的时间段)内发生了较大的跳变,IC 就可能误判或丢失部分数据。若信号具有良好的信号完整性,则电路具有正确的时序关系和信号幅度,数据不会出现错误的捕获,意味着收端能够得到比较纯净的数据。相反,若出现误触发、阻尼振荡、过冲、欠冲等信号完整性故障,就会引起任意的信号跳变,导致输入的畸变数据被送入锁存,或在畸变的时钟跳变沿捕获数据,信号不能正常响应,导致系统工作异常,性能下降。

在高速系统中,一段导体不仅仅是导体,也已成为具有分布参数的传输线。对此,电路设计工程师和PCB 设计工程师已不能回避。能否处理好系统的信号互连,解决信号完整性的问题,是系统设计成功的关键。同时,信号完整性也是解决电源完整性、电磁兼容与电磁干扰(EMC/EMI)问题的基础和前提。

目前,信号完整性工程还是一门尚未成熟的学科,其分析方法和实践都还没有很好的定义,还处于不断的探索阶段。在基于信号完整性计算机分析的PCB 设计方法中,最为核心的部分就是PCB 板级信号完整性模型的建立,这是与传统的设计方法的区别之处。SI 模型的正确性将决定设计的正确性,而SI 模型的可建立性则决定了这种设计方法的可行性。在电子设计中已经有多种可以用于PCB 板级信号完整性分析的模型。其中最为常用的有三种,分别是SPICE、IBIS 和Verilog-A。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。 举报投诉

- 相关下载

- 相关文章