资料下载

具有最小路由资源的数据路径性能多路复用器设计技术资料说明

信号的多路复用是一种常见功能,通常由Xilinx实现工具和设备充分处理。然而,可能会有一些特别具有挑战性的设计,其中考虑不同的复用技术并选择最适合这种情况的技术是很有帮助的。对设备特性及其在实现每种复用技术方面的适用性的深入理解使设计者能够为成功进行结构设计。本应用说明还说明了VHDL和Verilog代码,这些代码确保对实现的最大控制,从而产生最可预测的结果。

您可以从Xilinx网站下载此应用程序说明的参考设计文件。有关设计文件的详细信息,请参见参考设计。

FPGA是一种具有许多并行交换活动的计算和逻辑基板。例如,在有线网络路由系统中,FPGA可以在m:n的倍数逻辑元件之间有许多布线模式。随着对高带宽需求的增加,m和n都可以相对较大,并且,使用,这可能导致一些重要的多路复用任务必须执行。因此,跨越spartan-6 fpgas、virtex-6 fpgas和7系列fpgas的数据路径路由是系统设计的基础部分。

有时需要付出超越综合的努力来确保FPGA实现满足系统目标,例如使用Planahead™设计工具锁定位置。作为一种额外的方法,本应用说明为系统设计者提供了有效实现数据路由逻辑的新技术,该技术只需要ISE设计套件或Vivado®设计套件的HDL规范即可工作。这些技术同时做两件事来改进设计闭包。首先,通过在片内压缩更多的逻辑,而使用较少的通用互连线,可以提高性能。其次,使用更多的逻辑/更少的线来实现会增加结果的确定性,影响系统设计的其他方面,包括降低FPGA利用率和用于实现的软件运行时间。

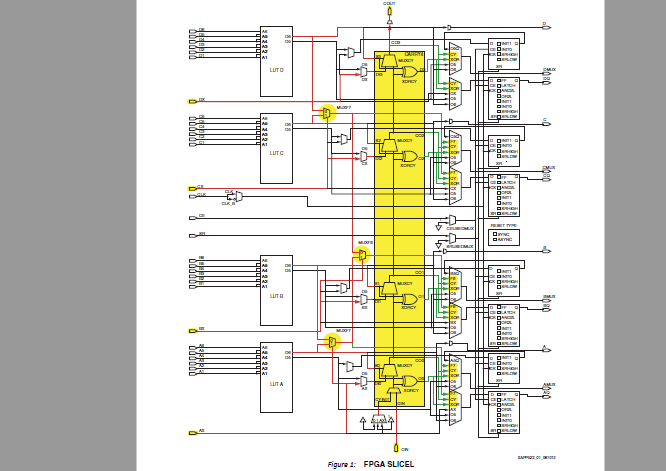

实现更高效的多路复用和数据路由的途径是首先了解Spartan-6 fpgas、Virtex-6 fpgas和7系列fpgas切片结构的特征,这些特征通常不是通过路由逻辑的行为合成推断出来的。从这个角度来看,相对简单的实用技术在减少资源和减少每比特m:n逻辑的连线方面可以获得很大的收益。本设计说明了几种2N宽的多路复用器,二进制选择

尺寸不超过2N的多路复用器、可选数据选择器及其在FPGA中的实现。这些技术使用FPGA切片中的基本元素(BEL)来形成可重复使用的单元,这些单元很容易根据用户需求进行修改,并且可以在不受用户约束的情况下放置在FPGA的任何位置。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。 举报投诉

- 相关下载

- 相关文章