DC-DC开关电源的经验总结

描述

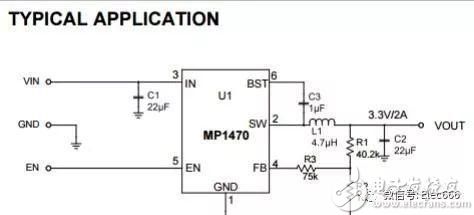

相关的Layout经验,供各位EE参考。先上一张MPS经典热销产品MP1470的典型应用图,可以轻松实现12V转3.3V/2A:

DC-DC的layout非常重要,会直接影响到产品的稳定性与EMI效果,总结经验/规则如下:

1、处理好反馈环(对应上图中R1-R2-R3-IC_FB&GND),反馈线不要走肖特基下面,不要走电感(L1)下面,不要走大电容下面,不要被大电流环路包围,必要时可在取样电阻并个100pF的电容增加稳定性(但瞬态会受到一点影响);

2、反馈线宁可细不要粗,因为线越宽,天线效应越明显,影响环路的稳定性。一般用6-12mils的线;

3、所有电容尽可能靠近IC;

4、电感按规格书指标的120-130%的容量选取,不可过大,过大会影响效率和瞬态;

5、电容按规格书的150%的容量选取。如果是用贴片陶瓷电容,如果用22uF,用两个10uF并联会更好。若对于成本不敏感,电容可用更大些。特别提示:输出电容,若是用铝电解电容,千万记得要用高频低阻的,不可随便放个低频滤波电容!

6、尽可能缩小大电流环路的包围面积。如果不方便缩小,用敷铜的方式变成一条窄缝。

7、不要在关键回路上使用热阻焊盘,它们会引入多余的电感特性。

8、当使用地线层的时候,要尽力保持输入切换回路下面的地层的完整性。任何对这一区域地线层的切割都会降低地线层的有效性,即使是通过地线层的信号导通孔也会增加其阻抗。

9、导通孔可以被用于连接退藕电容和IC的地到地线层上,这可使回路最短化。但需要牢记的是导通孔的电感量大约在0.1~0.5nH之间,这会根据导通孔厚度和长度的不同而不同,它们可增加总的回路电感量。对于低阻抗的连接来说,使用多个导通孔是应该的。

在上面的例子中,通到地线层的附加导通孔对缩减CIN回路的长度没有帮助。但在另一个例子中,由于顶层的路径很长,通过导通孔来缩小回路面积就十分有效。

10、需要注意的是将地线层作为电流回流的路径会将大量噪声引入地线层,为此可将局部地线层独立出来,再通过一个噪声很低的点接入主地当中。

11、当地线层很靠近辐射回路的时候,其对回路的屏蔽效果会得到有效的加强。因此,在设计局多层PCB的时候,可将完整的地线层放在第二层,使其直接位于承载了大电流的顶层的下面。

12、非屏蔽电感会生成大量的漏磁,它们会进入其他回路和滤波元件之中。在噪声敏感的应用中应当使用半屏蔽或全屏蔽的电感,还要让敏感电路和回路远离电感。

解决EMI问题可能是一件很复杂的事情,尤其是在面对完整的系统,同时又不知道辐射源所在的时候。有了关于高频信号和开关切换式转换器中的电流回路的基础知识,再加上对元器件和PCB布局在高频情况下的表现的了解,结合某些简单自制工具的使用,要想找出辐射源和降低辐射的低成本解决方案,从而轻松的解决EMI问题是有可能的。预告下期将为大家带来一个DIY EMI探测工具。

-

五个木LSY

2019-03-22

0 回复 举报请问DIY EMI探测工具这一期什么时候推出,谢谢。 收起回复

五个木LSY

2019-03-22

0 回复 举报请问DIY EMI探测工具这一期什么时候推出,谢谢。 收起回复

- 相关推荐

- DC-DC

-

开关电源啸叫的一点经验总结2012-08-07 0

-

DC-DC开关电源2016-03-17 0

-

DC-DC可调开关电源设计与仿真研究2017-03-28 0

-

DC-DC开关电源工作原理详解2019-03-19 0

-

DC-DC开关电源设计2019-03-19 0

-

DC-DC变换的开关电源电路有什么功能?2019-10-25 0

-

.基本DC-DC变换器开关电源学习笔记2021-10-29 0

-

DC-DC变换的开关电源电路图2009-05-13 1942

-

开关电源EMI整改经验总结2016-09-18 725

-

开关电源测量的经验总结2016-09-18 687

-

ADP1828低压DC-DC开关电源2021-05-18 676

-

利用推挽正激技术设计DC-DC开关电源2021-08-31 655

-

车载DC-DC开关电源的设计2021-09-22 891

-

开关电源(DC-DC)与LDO电源的区别---原理2021-10-21 825

-

DC-DC开关电源电路中的伏秒平衡2022-09-19 1200

全部0条评论

快来发表一下你的评论吧 !