BJ-EPM240学习板之乘法器设计实验

电子说

1.2w人已加入

描述

乘法器是众多数字系统中的基本模块。从原理上说它属于组合逻辑范畴:但从工程实际设计上来说,它往往会利用时序逻辑设计的方法来实现,属于时序逻辑的范畴。

通过这个实验使大家能够掌握利用FPGA/CPLD设计乘法器的思想,并且能够将我们设计的乘法器应用到实际工程中。乘法器的设计方法有两种:组合逻辑设计方法和时序逻辑设计方法。采用经合逻辑设计方法,电路事先将所有的乘积项全部计算出来,最后加法运算。采用时序逻辑设计方法,电路将部分已经得到的乘积结果右移,然后与乘积项相加并保存和值,反复迭代上述步骤直到计算出最终乘积。

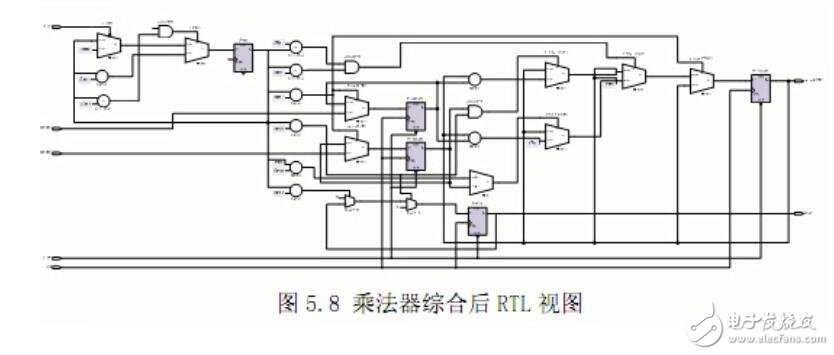

在该实验中就是要利用时序逻辑设计方法来设计-一个16位乘法器,既然是利用时序逻辑设计方法那么就得利用时钟信号控制乘法器运算。用时序逻辑设计方法与用组合逻辑设计方法比较,它有什么好处呢?利用时序逻辑设计方法可以使整体设计具备流水线结构的特征,能适用在各种实际工程设计中。

更多关于BJ-EPM240学习板之乘法器设计实验请看视频。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

#硬声创作季 #FPGA 玩转FPGA-12 BJ-EPM240实验5-乘法器设计实验-1水管工 2022-10-29

-

#硬声创作季 #FPGA 玩转FPGA-12 BJ-EPM240实验5-乘法器设计实验-2水管工 2022-10-29

-

1/4平方乘法器2010-05-18 1815

-

N象限变跨导乘法器2010-05-18 1580

-

变跨导乘法器2010-05-18 1115

-

基于IP核的乘法器设计2011-05-20 837

-

FPGA视频教程之使用BJ-EPM240学习板进行数码管显示实验的资料说明2019-02-28 1038

-

FPGA视频教程之BJ-EPM240学习板的详细资料介绍2019-03-01 1112

-

FPGA视频教程之BJ-EPM240学习板乘法器设计实验的详细资料说明2019-03-04 785

-

BJ-EPM240学习板之Johnson.计数器实验2019-03-06 4999

-

课程5:BJ-EPM240学习板介绍2019-12-23 2709

-

深入浅出玩转FPGA视频:BJ-EPM240学习板介绍2019-12-16 1461

-

FPGA视频教程:BJ-EPM240学习板-乘法器设计实验2019-12-11 1708

-

FPGA视频教程:BJ-EPM240学习板介绍2019-12-10 3463

-

BJ-EPM240学习板:乘法器设计实验2019-12-24 2375

全部0条评论

快来发表一下你的评论吧 !